Прокладка управляемого импеданса

С ростом скоростей переключения устройств трассировка с контролируемым импедансом стала одной из самых актуальных тем для цифрового разработчика. На этой странице рассказывается, как использовать механизм анализа целостности сигналов для согласования импедансов компонентов, а также возможности трассировки с контролируемым импедансом в редакторе PCB.

В инженерной среде есть поговорка: существует только два типа инженеров-электронщиков, работающих в области цифрового проектирования: те, у кого уже были проблемы с целостностью сигналов, и те, у кого они еще будут. Еще не так давно термин «целостность сигнала» относился к узкоспециализированной области, и заниматься этим приходилось только в высокоскоростных проектах. Однако скорости переключения устройств в таких высокоскоростных проектах уже перестали быть чем-то особенным — они быстро становятся нормой. По мере того как совершенствование технологии интегральных схем уменьшает размеры транзисторов, растут и скорости их переключения. Именно эта скорость переключения влияет на целостность цифровых сигналов.

К счастью, многих потенциальных проблем с целостностью сигналов можно избежать, если следовать хорошим принципам проектирования и реализовывать проект в виде платы с контролируемым импедансом. Для этого требуются определенные возможности средств проектирования: нужны инструменты анализа, которые выявляют цепи с потенциальными проблемами звона и отражений, а также инструменты проектирования платы, позволяющие получить правильные импедансы трассировки. Редактор PCB в Altium Designer обладает этими возможностями.

Эта страница поможет вам понять, что вызывает проблемы с целостностью сигналов и может ли ваша плата, вероятно, страдать от них. Также будут рассмотрены два подхода к проектированию, которые необходимо применять для минимизации потенциальных проблем SI: согласование импедансов компонентов и трассировка с контролируемым импедансом.

Когда трассировка становится частью схемы

По мере роста скоростей переключения устройств возрастают и требования к разработчику печатной платы и производителю. Когда длительность фронта переключения сигнала становится меньше длины проводника PCB, по которому он передается, этот проводник необходимо рассматривать как часть схемы. Этот проводник имеет импеданс, который называется characteristic impedance (Zo).

Лучший способ управлять влиянием этих дополнительных элементов схемы — спроектировать трассировку так, чтобы характеристический импеданс был постоянным по всей длине. Этот метод называется controlled impedance routing.

Импеданс трассировки определяется:

- Cross-sectional area of the trace - определяется шириной, высотой (толщиной меди) и наклоном боковых стенок проводника, формируемых в процессе травления.

- Distance from the trace to the reference plane(s) - путь возврата энергии сигнала так же важен, как и путь самого сигнала. Этот обратный путь проходит вдоль сигнального пути в соседней(их) опорной(ых) плоскости(ях).

- Properties of the surrounding materials - энергия сигнала не ограничивается медью проводника; из-за скин-эффекта она также распространяется в диэлектрическом материале, окружающем проводник. Диэлектрическая проницаемость материала показывает, насколько диэлектрик влияет на прохождение этой энергии.

Калькулятор импеданса Simbeor рассчитывает ширину(ы), необходимую(ые) для достижения заданного импеданса.

Нужна ли мне трассировка с контролируемым импедансом?

Вы спрашиваете, стоит ли вообще заниматься трассировкой с контролируемым импедансом?

В идеальной ситуации вся энергия, выходящая с выходного вывода компонента, должна передаваться в подключенный проводник на PCB, проходить по трассировке PCB к входному выводу нагрузки на другом конце и поглощаться этой нагрузкой. Если нагрузка не поглощает всю энергию, оставшаяся энергия может отразиться обратно в трассировку PCB и вернуться к выходному выводу источника. Эта отраженная энергия может взаимодействовать с исходным сигналом, складываясь с ним или вычитаясь из него (в зависимости от полярности энергии), что приводит к звону. Если звон достаточно велик, он повлияет на целостность сигнала, что приведет к непредсказуемому, ошибочному поведению схемы.

Итак, как понять, может ли это произойти? Если вывод источника способен завершить переход фронта до того, как сигнал достигнет вывода нагрузки, существуют условия, при которых на ваш проект может повлиять отраженная энергия. Распространенное практическое правило, используемое для определения вероятности проблем SI, — это правило «1/3 времени нарастания». Оно гласит, что если длина проводника превышает 1/3 длины, соответствующей времени нарастания, могут возникать отражения (звон). Если время нарастания на выводе источника составляет 1 нс, то трассу длиннее 0,33 нс (примерно 2 дюйма в FR4) необходимо рассматривать как линию передачи, то есть как потенциальный источник проблем с целостностью сигнала. Если ваши устройства имеют такое время нарастания и вы знаете, что у вас будут трассы такой длины, то на PCB могут возникнуть проблемы с целостностью сигнала.

Как контролировать импедансы?

Как избежать ситуации, когда энергия многократно отражается между источником и нагрузкой? Это достигается согласованием импедансов. Согласование импедансов гарантирует, что вся энергия передается от источника в трассировку, а затем из трассировки в нагрузку. Трассировка платы с учетом импеданса называется трассировкой с контролируемым импедансом; иначе говоря, плата, в которой импедансы были учтены и настроены, называется PCB с контролируемым импедансом.

Для достижения согласования импедансов есть два отдельных элемента: первый — согласование компонентов, второй — трассировка платы для получения требуемого импеданса.

Согласование импедансов компонентов

Невозможно получить PCB с контролируемым импедансом только за счет трассировки. Сначала необходимо проверить и при необходимости согласовать импедансы компонентов.

В идеале нужно выявлять цепи, которые могут иметь потенциальные проблемы с целостностью сигналов, уже на этапе захвата схемы, чтобы все дополнительные компоненты терминирования можно было включить в проект до начала проектирования платы. Поскольку выходные выводы имеют низкий импеданс, а входные — высокий, вероятно, для согласования импедансов вам потребуется добавить в проект компоненты терминирования.

Вы можете выполнить анализ целостности сигналов для своего проекта на этапе захвата схемы. При запуске команды Tools » Signal Integrity часто появляется диалог Errors or Warnings, указывающий, что не всем компонентам назначены модели целостности сигналов. Механизм анализа Signal Integrity автоматически выберет модели по умолчанию на основе позиционных обозначений компонентов; нажмите Continue, чтобы использовать значения по умолчанию, или Model Assignments, чтобы просмотреть и изменить модели. Вы можете открыть диалог Signal Integrity Model Assignments в любое время с помощью кнопки Model Assignments на панели Signal Integrity.

Анализ проекта

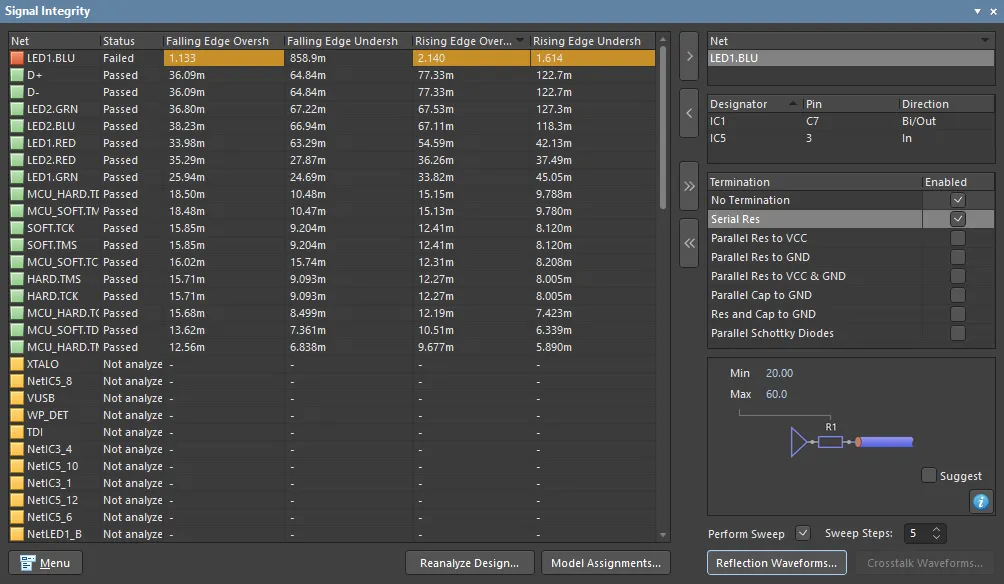

Когда выполняется команда Tools » Signal Integrity, проект анализируется, и все потенциально проблемные цепи отображаются на панели Signal Integrity, как показано ниже.

Проверка проекта на наличие потенциальных проблем с целостностью сигналов на этапе захвата схемы.

Проверка проекта на наличие потенциальных проблем с целостностью сигналов на этапе захвата схемы.

С панели можно выполнить анализ отражений для выбранной цепи (или цепей). Слева отображаются результаты анализа для всех цепей проекта. Выберите цепь и нажмите кнопку ![]() (или дважды щелкните имя цепи), чтобы перенести эту цепь в поле Net в правой части панели, где можно выполнить ее подробный анализ, включая:

(или дважды щелкните имя цепи), чтобы перенести эту цепь в поле Net в правой части панели, где можно выполнить ее подробный анализ, включая:

- Просмотр выводов в этой цепи, при этом одинарный щелчок позволяет выполнить перекрестный переход к этому выводу на схеме, а двойной щелчок — проверить и настроить модель, назначенную этому выводу.

- Включение одного или нескольких теоретических вариантов терминирования для этой цепи.

- Выполнение анализа отражений для цепи с получением набора осциллограмм, показывающих поведение на каждом выводе в этой цепи.

Панель позволяет экспериментировать с возможными конфигурациями и значениями терминирования. Обратите внимание, что в показанной выше области Termination панели Signal Integrity включен параметр Serial Res. В разделе панели ниже показан последовательный терминальный резистор. Здесь задаются минимальное и максимальное теоретические значения сопротивления последовательного терминирования, которые будут использоваться для анализа отражений (снимите флажок Suggest, чтобы ввести собственные значения).

Изучение результатов

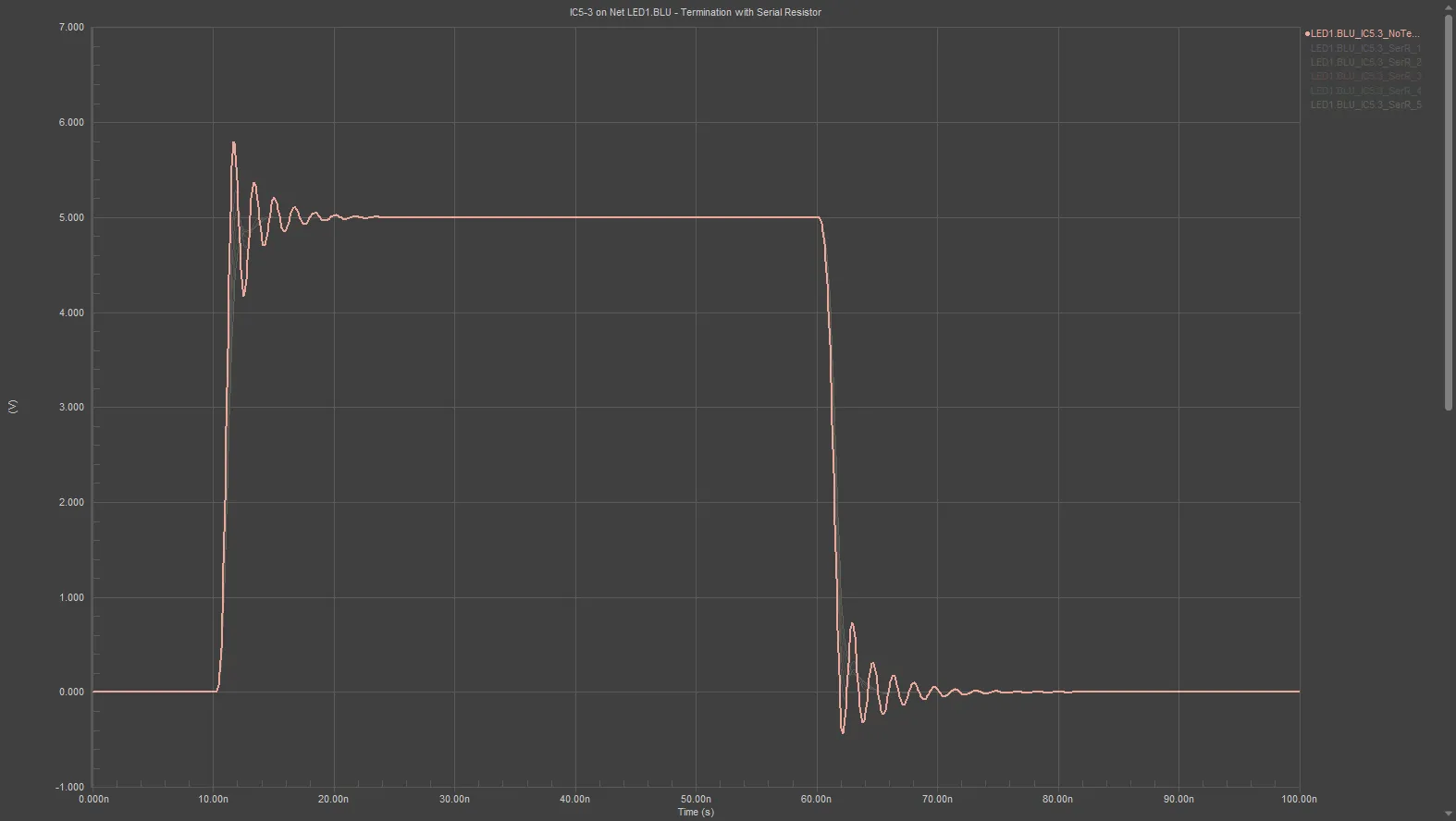

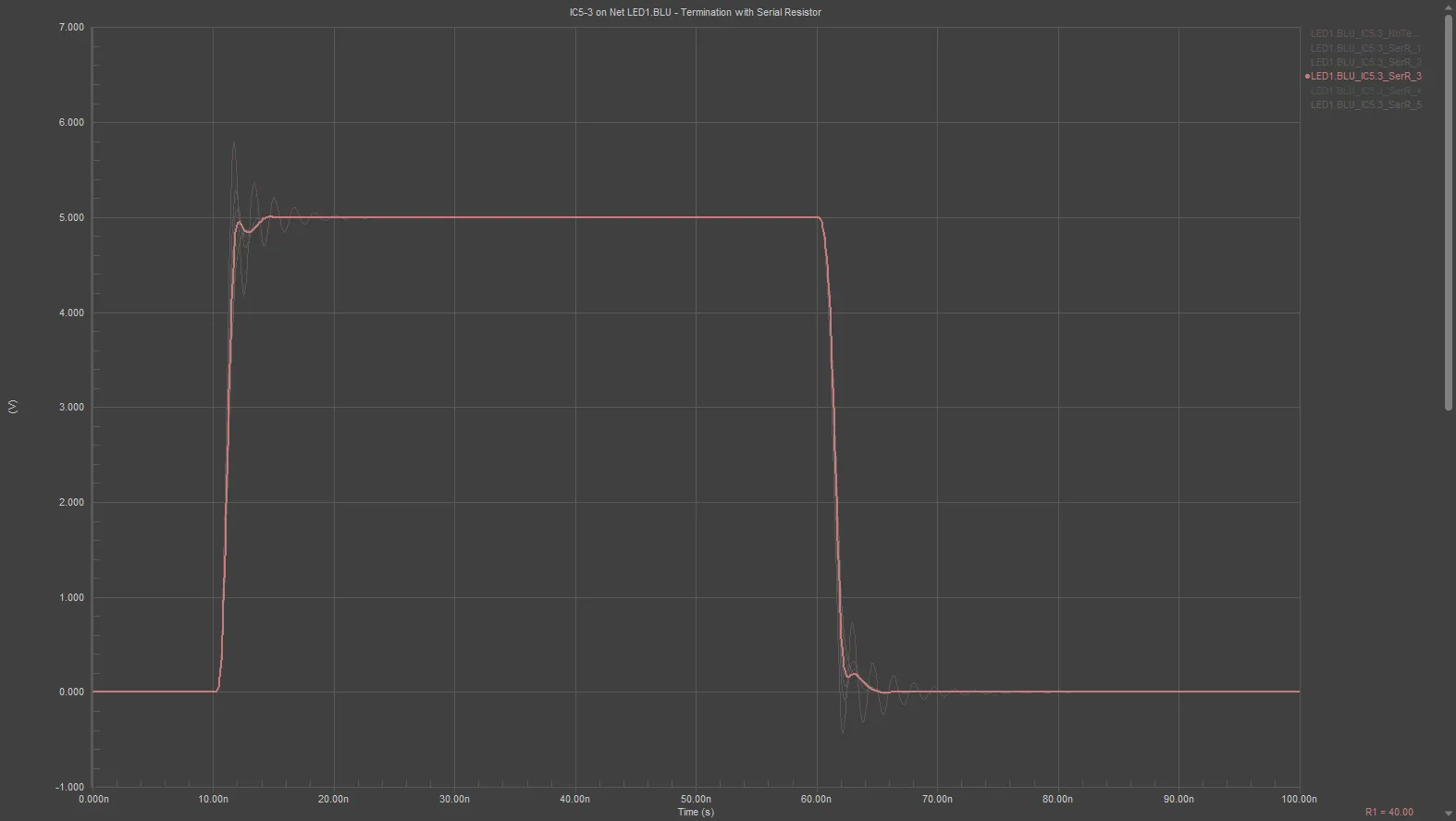

При нажатии кнопки Reflection Waveforms для этой цепи выполняется точный анализ отражений, а результаты отображаются в новом окне осциллограмм (*.SDF).

Окно осциллограмм будет включать:

- Диаграмму для каждой анализируемой цепи; нажимайте вкладки в нижней части окна для переключения между диаграммами.

- Каждая диаграмма будет включать график для каждого вывода в этой цепи, показывающий поведение сигнала на этом выводе.

На изображениях ниже показаны два графика результатов на входном выводе цепи, выбранной на изображении предыдущей панели. Первый график показывает входной вывод в цепи без согласования; второй график показывает шесть проходов: один для исходной цепи без согласования, а затем пять проходов с теоретическим последовательным согласующим сопротивлением, добавленным на выводе источника.

Было выполнено пять проходов анализа отражений (Sweep Steps значение параметра = 5), при этом теоретический согласующий резистор изменялся ступенчато от Min = 20 Ом до Max = 60 Ом. Эти пять проходов (первый проход при 20 Ом, последний — при 60 Ом) перечислены в правой части графика. Щелчок по каждой метке выделяет соответствующий результат и отображает значение теоретического согласующего сопротивления внизу справа. Для этой цепи последовательное согласующее сопротивление 40 Ом даст график, выбранный на изображении справа.

График слева показывает анализ отражений для цепи с потенциальными проблемами целостности сигнала; график справа — это та же цепь, но с добавленным теоретическим последовательным согласующим резистором примерно 40 Ом.

График слева показывает анализ отражений для цепи с потенциальными проблемами целостности сигнала; график справа — это та же цепь, но с добавленным теоретическим последовательным согласующим резистором примерно 40 Ом.

Что определяет импеданс трассировки?

Вторая часть создания печатной платы с контролируемым импедансом заключается в трассировке платы таким образом, чтобы проводники имели заданный импеданс. Существует ряд факторов, влияющих на импеданс сигнальных трасс, включая размеры проводников и свойства материалов, используемых при изготовлении печатной платы.

Редактор PCB включает электромагнитный движок Signal Integrity Simbeor® от Simberian. Точность моделей Simbeor подтверждена с использованием передовых алгоритмов полного 3D-волнового анализа, бенчмаркинга и экспериментальной валидации. Движок Simbeor поддерживает все современные структуры плат и материалы.

Версия Simbeor

Simbeor SFS

Импедансы рассчитываются с помощью Simbeor SFS, квазистатического решателя полей. Simbeor SFS — это продвинутый квазистатический 2D-решатель полей, основанный на методе моментов, который был подтвержден сходимостью, сравнениями и измерениями. Решатель строит сетку границ диэлектриков и проводников и решает соответствующие уравнения для построения частотно-зависимых матриц RLGC для телеграфных уравнений.

Simbeor SFS не является полноволновым решателем, поскольку это не требуется для оценки импеданса, задержки или затухания в межсоединениях PCB из-за квази-TEM-характера распространяющихся там волн. Такие волны можно точно моделировать с помощью параметров RLGC, извлеченных квазистатическим 2D-решателем полей.

Уникальное свойство решателя Simbeor SFS заключается в поддержке моделей шероховатости проводников. Обратите внимание, что он не поддерживает многослойную модель проводника (покрытие), а шероховатость является общей для всех проводников. Решатель является квазистатическим, поскольку решение не включает высокочастотную дисперсию, возникающую в микрополосковых линиях (более высокая концентрация полей в диэлектрике с большей диэлектрической проницаемостью на высоких частотах).

► Узнайте больше о технологии электромагнитного анализа целостности сигнала Simberian

Поддерживаемые структуры PCB

Импедансы могут быть рассчитаны для следующих структур PCB:

- Микрополосковая линия

- Симметричная стриплайн-линия

- Асимметричная стриплайн-линия

- Одиночные и дифференциальные копланарные структуры

- Несколько соседних диэлектрических слоев с различными диэлектрическими свойствами.

Настройка PCB для трассировки с контролируемым импедансом

Трассировка с контролируемым импедансом — это настройка размеров проводников и свойств материалов платы для получения заданного импеданса. Это выполняется в Layer Stack Manager редактора PCB. Чтобы открыть Layer Stack Manager,, выберите Design » Layer Stack Manager в главном меню. Layer Stack Manager открывается в редакторе документов так же, как лист схемы, PCB и другие типы документов.

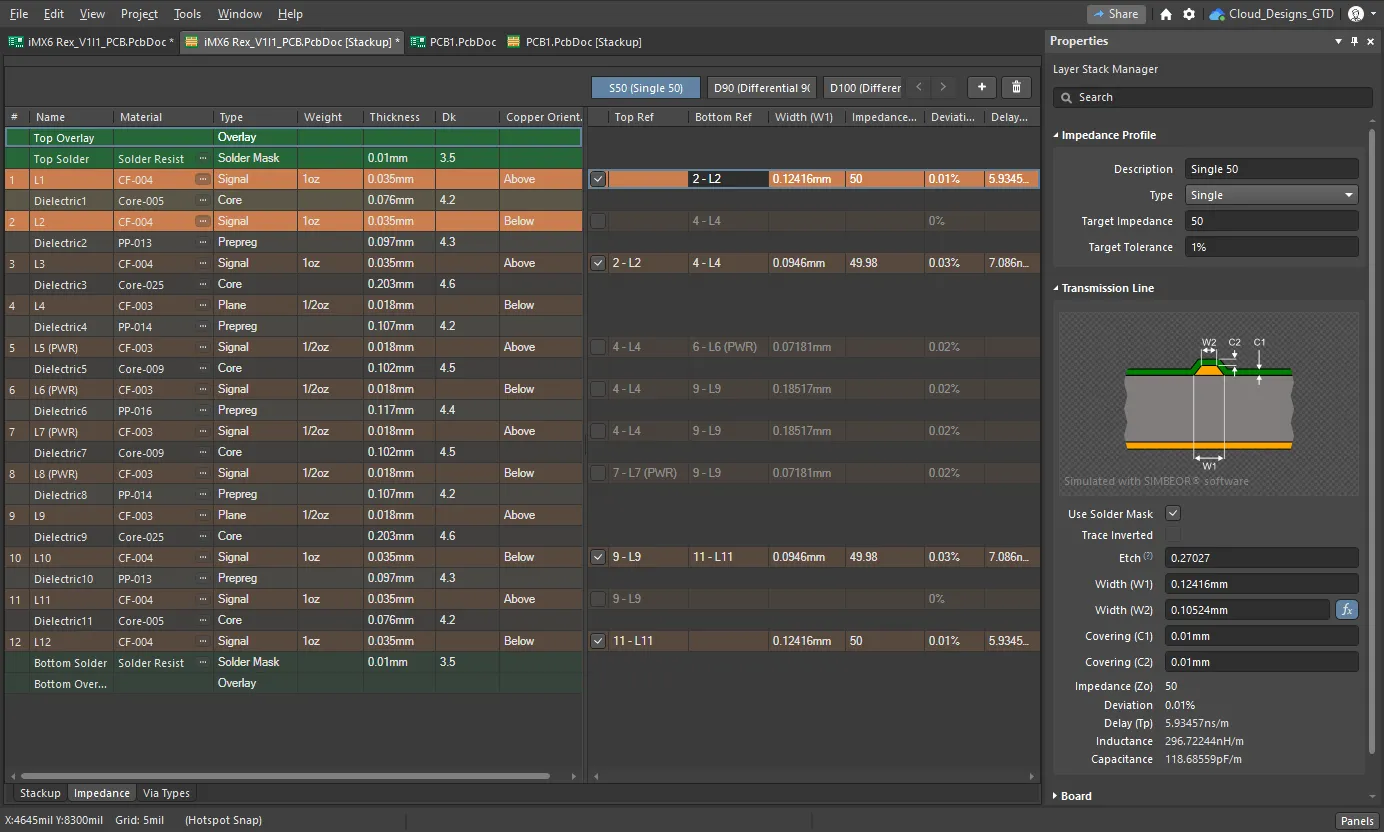

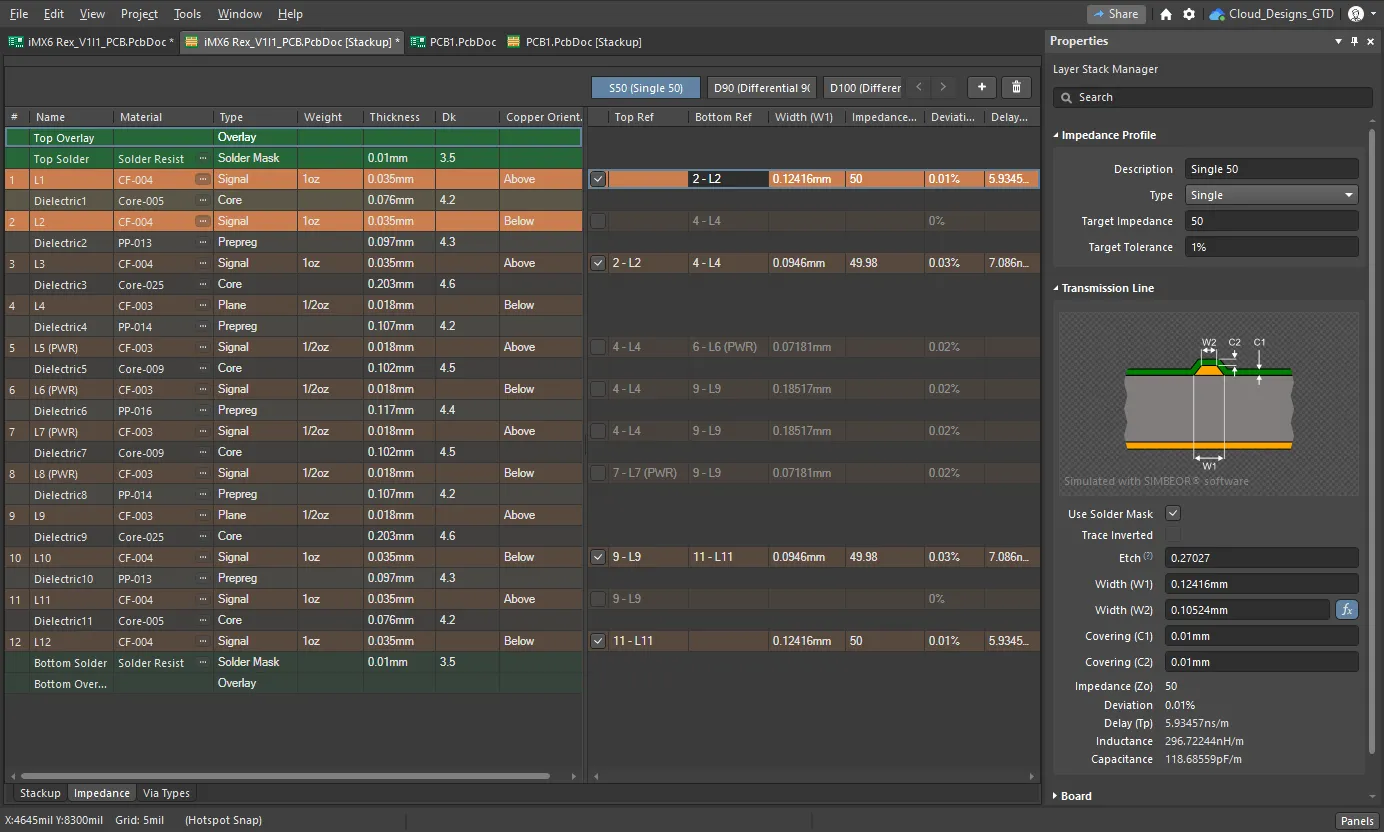

Ширина проводника, необходимая для получения заданного импеданса, рассчитывается как часть профиля импеданса, настраиваемого на вкладке Impedance в Layer Stack Manager.

На основе:

- значений Target Impedance, Target Tolerance и Roughness, которые вы настраиваете на вкладке Impedance, и

-

настроек материалов, заданных на вкладке Stackup, включая:

- толщину сигнального слоя,

- толщину окружающих диэлектрических слоев (расстояния до опорной(ых) плоскости(ей)), и

- свойства диэлектрического материала (диэлектрическая проницаемость Dk и коэффициент потерь Df).

Когда все это настроено правильно, калькулятор импеданса имеет достаточно информации для расчета следующего:

- Ширина проводника

- Расчетный импеданс (Z)

- Синфазный импеданс (Zcomm)

- Отклонение импеданса (Z Deviation)

- Задержка распространения (Tp)

- Индуктивность на единицу длины (p.u.l.)

- Емкость на единицу длины (p.u.l.)

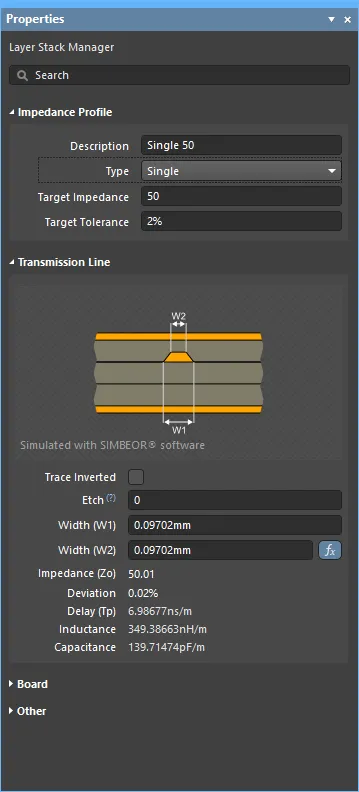

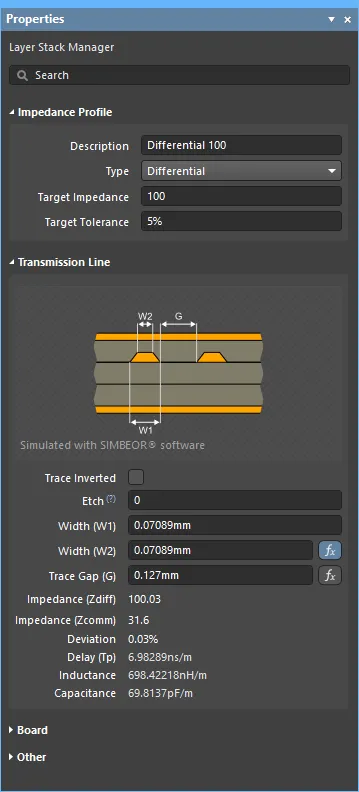

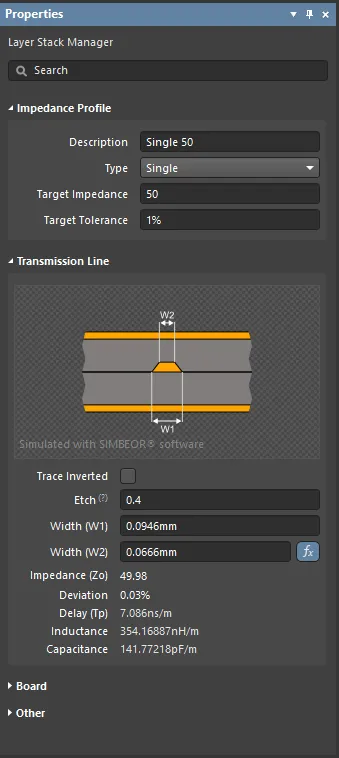

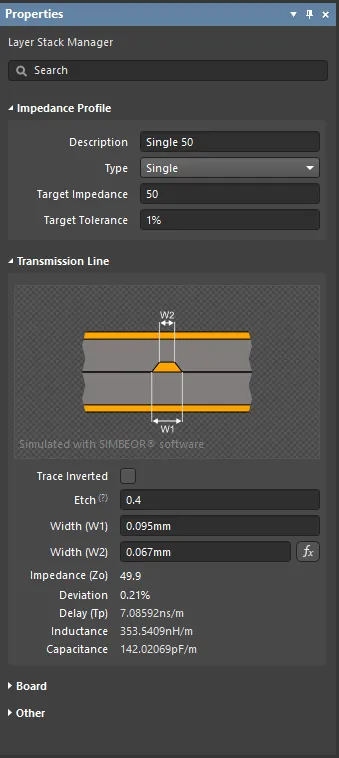

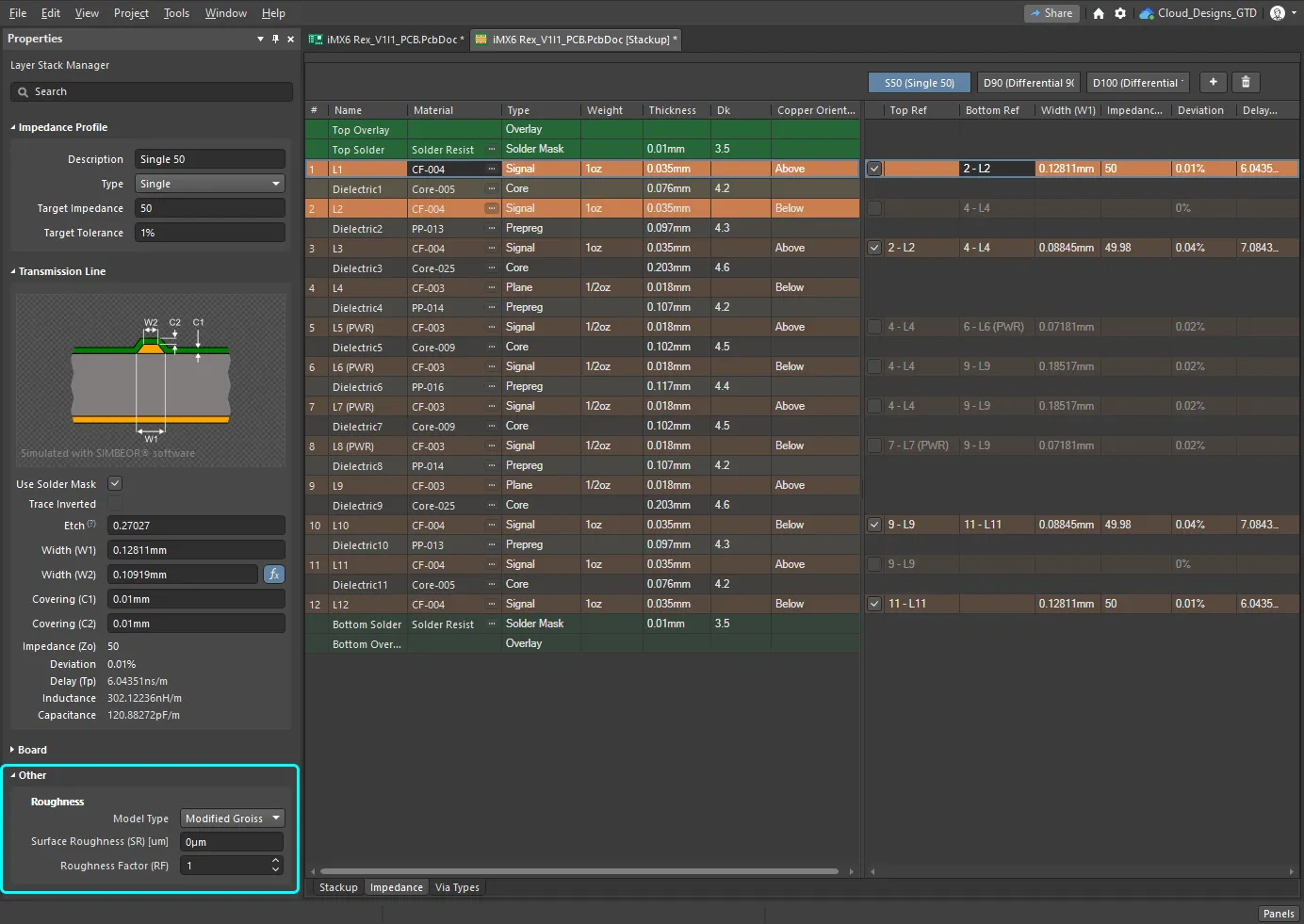

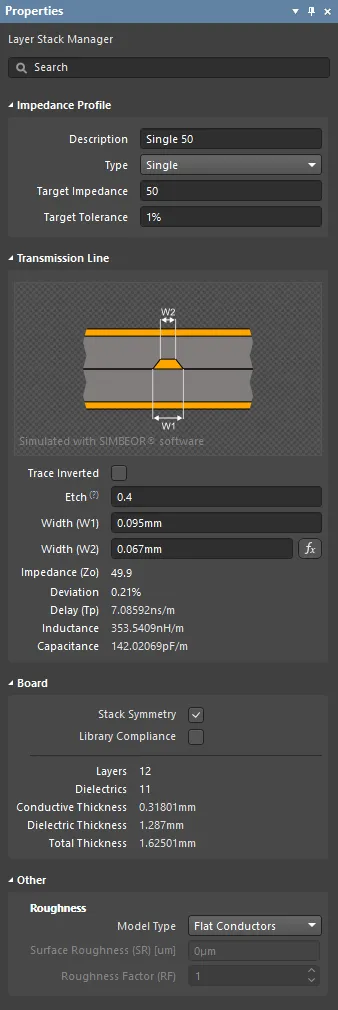

Рассчитанные значения отображаются в разделе Transmission Line панели Properties когда на Impedance выбрана вкладка Layer Stack Manager, как показано ниже.

Профиль импеданса 50Ω, определенный для одиночных цепей, трассируемых на верхнем слое. Наведите курсор на изображение, чтобы отобразить настройки того же профиля для слоя L3 (изображение предоставлено FEDEVEL Open Source, www.fedevel.com).

Профиль импеданса 50Ω, определенный для одиночных цепей, трассируемых на верхнем слое. Наведите курсор на изображение, чтобы отобразить настройки того же профиля для слоя L3 (изображение предоставлено FEDEVEL Open Source, www.fedevel.com).

Настройка стека слоев

Main page: Определение стека слоев

Медные и диэлектрические технологические слои настраиваются на вкладке Stackup в Layer Stack Manager.

- На этой вкладке слои добавляются, удаляются и настраиваются. Для rigid-flex конструкции на этой вкладке также включаются и отключаются слои.

-

Свойства текущего выбранного слоя можно редактировать непосредственно в таблице или на панели Properties. Нажмите кнопку

внизу рабочей области, чтобы включить панель.

внизу рабочей области, чтобы включить панель.

- Щелкните правой кнопкой мыши в таблице слоев или используйте команды Edit » Add Layer, чтобы добавить слой. При добавлении медного слоя также будет добавлен диэлектрический слой, если существующий соседний слой тоже является медным.

- Если в разделе Board панели Properties включен параметр Stack Symmetry, слои добавляются попарно симметрично относительно центрального диэлектрического слоя.

- Материал слоя можно либо ввести в выбранную ячейку Material, либо выбрать в диалоговом окне Select Material; нажмите кнопку многоточия , чтобы открыть его.

- К медному слою можно добавить финишное покрытие поверхности. Используйте подменю Add Layer, чтобы добавить слой Surface Finish к текущему выбранному медному слою, затем нажмите кнопку многоточия для нового слоя финишного покрытия, чтобы выбрать тип покрытия.

- Выбранный слой можно перемещать вверх или вниз среди слоев того же типа с помощью контекстного меню или меню Edit.

- Область Board панели Properties включает параметры для принудительного соблюдения Stack Symmetry и Library Compliance. Подробнее об этом ниже.

- Область Board панели Properties отображает сводку по текущему выбранному стеку (или подстеку для многосекционной rigid/flex-конструкции).

Рекомендации по стеку слоев

Базовое требование для контроля импеданса — наличие пути возврата сигнала под каждым сигнальным путем. Движок Simbeor SI поддерживает как слои-плоскости, так и сигнальные слои, покрытые полигоном. Эти слои пути возврата должны быть распределены по стеку платы. В идеале они располагаются так, чтобы по крайней мере один слой пути возврата был смежным с каждым сигнальным слоем, несущим трассировку с контролируемым импедансом. Смежный слой пути возврата обеспечивает путь возвратного тока сигнала и, по причинам, которые здесь не рассматриваются, делает это независимо от постоянного напряжения, распределяемого этой плоскостью.

Возвратный ток, протекающий по плоскости, будет стремиться следовать по тому же физическому пути, что и трасса на сигнальном слое, поэтому важно избегать внесения разрывов, таких как разделение или вырез, в слое пути возврата под любой критически важной сигнальной трассировкой.

Помимо выбора подходящего порядка сигнальных слоев и слоев-плоскостей, необходимо также определить свойства материалов каждого слоя, включая:

- Толщину меди

- Толщину диэлектрика

- Диэлектрическую постоянную

Эти значения, а также ширина трассировки, вносят вклад в итоговый импеданс. Достижение требуемого импеданса затем становится процессом подстройки всех этих значений. Помните, что возможные значения толщины меди и диэлектрика также могут быть ограничены — в зависимости от материалов, доступных у вашего производителя PCB.

► Узнайте больше о возможных стеках слоев

Определение профилей импеданса

Движок Simbeor встроен в Layer Stack Manager редактора PCB (Design » Layer Stack Manager). Чтобы настроить стек слоев для трассировки с контролируемым импедансом, перейдите на вкладку Layer Stack Manager's Impedance, где можно добавить и настроить профиль импеданса.

Профиль импеданса 50Ω, заданный для отдельных цепей, трассируемых на верхнем слое. Наведите курсор на изображение, чтобы отобразить настройки того же профиля для слоя L3.

Профиль импеданса 50Ω, заданный для отдельных цепей, трассируемых на верхнем слое. Наведите курсор на изображение, чтобы отобразить настройки того же профиля для слоя L3.

Примечания по созданию и настройке профиля импеданса:

- В Layer Stack Manager переключитесь на вкладку Impedance, как показано выше.

-

Нажмите кнопку

(или кнопку

(или кнопку  , если профиль уже определен), чтобы добавить новый профиль.

, если профиль уже определен), чтобы добавить новый профиль.

- Задайте требуемые Type, Target Impedance и Target Tolerance импеданса на панели Properties. Поле Description является необязательным; оно будет отображаться везде, где отображается имя профиля импеданса.

-

Сетка слоев разделена на 2 области: слои в стекe отображаются слева, а затем для каждого сигнального слоя в стекe в области профиля импеданса справа отображается соответствующий слой. Используйте флажок слоя в области Profile, чтобы включить расчет импеданса для этого слоя. Используя изображение выше в качестве примера и ориентируясь на номер слоя, показанный в крайнем левом столбце, слои

L1,L3,L10иL12имеют установленный флажок слоя, что включает их в расчеты импеданса. -

Когда вы щелкаете по включенному слою в области Profile, все слои в стекe становятся приглушенными, кроме тех, которые используются для расчета импеданса для выбранного сигнального слоя (как показано на изображении выше). Отредактируйте опорный(е) слой(и) этого слоя в столбцах Top Ref и Bottom Ref области Impedance Profile . Обратите внимание, что опорные слои могут иметь Type слоя либо

Plane, либо Signal. Например, на изображении выше слойL10в стекe включен для расчетов импеданса, при этом Top Ref задан как9-L9, который является слоемPlane, а Bottom Ref задан как11-L11, который является слоем Signal . Программное обеспечение предполагает, что если сигнальный слой используется как опорная плоскость, то он содержит сплошную медную плоскость, подключенную к цепи питания или земли. - Установите флажок Impedance Profile для каждого другого слоя, на котором будет выполняться трассировка с этим импедансом, и настройте опорную(е) плоскость(и). Наведите курсор на изображение выше, чтобы отобразить профиль импеданса S50 для слоя L3.

- Если рассчитанная ширина проводника трассировки имеет значение, которое нельзя заказать, вы можете подстроить настройки ширины и зазора.

Подстройка настроек ширины и зазора

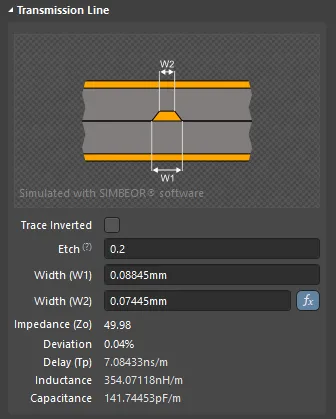

Программное обеспечение рассчитывает ширину проводника на основе целевого импеданса и допуска. Нередко рассчитанная ширина проводника оказывается значением, которое нельзя заказать, например 0.0683 мм. Производитель платы сообщит, какие толщины материалов доступны и какой точности они могут достичь для ширины проводников. После этого процесс сводится к тому, чтобы начать с желаемых значений, а затем проверять влияние на рассчитанные значения импеданса при корректировке размеров до доступных.

Для поддержки этого процесса проверки и подстройки настроек калькуляторы импеданса поддерживают прямой и обратный расчет импеданса. Режим по умолчанию — прямой (вводится импеданс, программное обеспечение рассчитывает ширину). Значок ![]() указывает на рассчитываемую переменную.

указывает на рассчитываемую переменную.

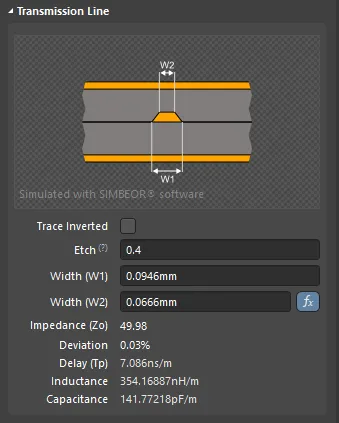

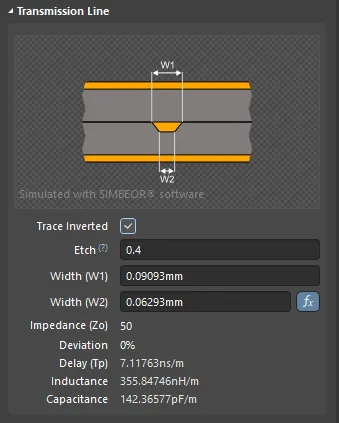

Целевой импеданс 50Ω дает рассчитанную в прямом режиме ширину (W1) 94.6 мкм. Изображение справа показывает обратный расчет, когда ширина (W1) установлена в 95 мкм.

Целевой импеданс 50Ω дает рассчитанную в прямом режиме ширину (W1) 94.6 мкм. Изображение справа показывает обратный расчет, когда ширина (W1) установлена в 95 мкм.

Чтобы выполнить обратный расчет и исследовать различные ширины проводника для выбранного слоя, введите новое значение Width (W1) и нажмите Enter на клавиатуре. Рассчитанные значения обновятся, чтобы отразить влияние изменения на эту ширину. Нажмите кнопку ![]() , чтобы вернуть калькулятор в режим прямого расчета. Ввод нового значения в Width (W2) изменит значение Etch.

, чтобы вернуть калькулятор в режим прямого расчета. Ввод нового значения в Width (W2) изменит значение Etch.

Чтобы исследовать результаты для линии передачи дифференциальной пары, выберите рассчитываемую переменную — либо Trace Width, либо Trace Gap — нажатием соответствующей кнопки ![]() . Измените другую переменную, чтобы изменить Target Impedance, либо, как вариант, измените Target Impedance, чтобы исследовать влияние на другую переменную.

. Измените другую переменную, чтобы изменить Target Impedance, либо, как вариант, измените Target Impedance, чтобы исследовать влияние на другую переменную.

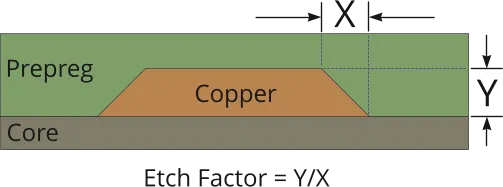

Коэффициент травления

Сигнальные проводники на PCB изготавливаются путем травления лишней меди. Поскольку травитель начинает удалять медь с поверхности, эта медь дольше находится в контакте с травителем. В результате готовые края проводника будут иметь наклон, уменьшая площадь поперечного сечения готового проводника, как показано на изображении ниже.

Площадь меди, потерянной на краях проводника (с обеих сторон) в процессе травления = X * Y

Величина наклона называется коэффициентом травления, где:

Etch Factor = Y/X

Если Y = X, то Etch Factor = 1

Ссылаясь на изображение, показанное на панели Properties:

Наведите курсор на ?, чтобы показать формулу.

Наведите курсор на ?, чтобы показать формулу.

Стандартное определение коэффициента травления — задавать его как отношение trace thickness / amount of over-etching. Это дает следующую формулу:

Etch Factor = T/[0.5(W1-W2)]

Недостаток этого подхода в том, что для указания отсутствия перетравливания (то есть когда края проводника вертикальны) пришлось бы ввести значение inf (бесконечность) для коэффициента травления. Чтобы упростить задание величины травления, формула была инвертирована, так что можно ввести значение 0 (ноль), чтобы указать отсутствие перетравливания.

Etch = [0.5(W1-W2)]/T

Ориентация меди

Еще одна технологическая деталь, влияющая на коэффициент травления, — это ориентация меди. Проводники PCB формируются путем травления лишней меди из сплошного листа меди, ламинированного на диэлектрическую подложку. Ориентация меди определяет направление, в котором медь выступает от этой подложки. Это также можно рассматривать как направление, с которого медь травится: сверху или снизу.

Установите флажок Trace Inverted, чтобы переключить ориентацию меди с Above на Below.

Установите флажок Trace Inverted, чтобы переключить ориентацию меди с Above на Below.

Шероховатость поверхности проводника

Поверхность каждого медного слоя в печатной плате имеет определенную шероховатость. В процессе изготовления PCB поверхность медных слоев обрабатывается для увеличения шероховатости с целью улучшения адгезии между медью и диэлектрическими слоями. Эта шероховатость поверхности становится значимым фактором, влияющим на импеданс проводника, при скоростях переключения выше 10 Гбит/с. В результате обширных исследований и анализа отраслевые эксперты пришли к выводу, что шероховатость поверхности можно моделировать с помощью коэффициента коррекции шероховатости, полученного из значений Surface Roughness и Roughness Factor.

RoughnessПараметры

Шероховатость поверхности учитывается при расчете характеристического импеданса.

Шероховатость поверхности учитывается при расчете характеристического импеданса.

Шероховатость:

-

Model Type - предпочтительная модель для расчета влияния шероховатости поверхности (дополнительную информацию о различных моделях см. в статьях ниже). Применяется ко всем медным слоям в подстеке.

-

Surface Roughness - значение шероховатости поверхности (можно получить у вашего производителя). Введите значение от 0 до 10 мкм, значение по умолчанию — 0.1 мкм

-

Roughness Factor - характеризует ожидаемое максимальное увеличение потерь в проводнике из-за эффекта шероховатости. Введите значение от 1 до 100; значение по умолчанию — 2.

Дополнительные материалы

- Practical methodology for analyzing the effect of conductor roughness on signal losses and dispersion in interconnects: Y. Shlepnev, C. Nwachukwu, DesignCon2012.

- Unified approach to interconnect conductor surface roughness modeling: Y. Shlepnev, 2017 IEEE 26th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS2017)

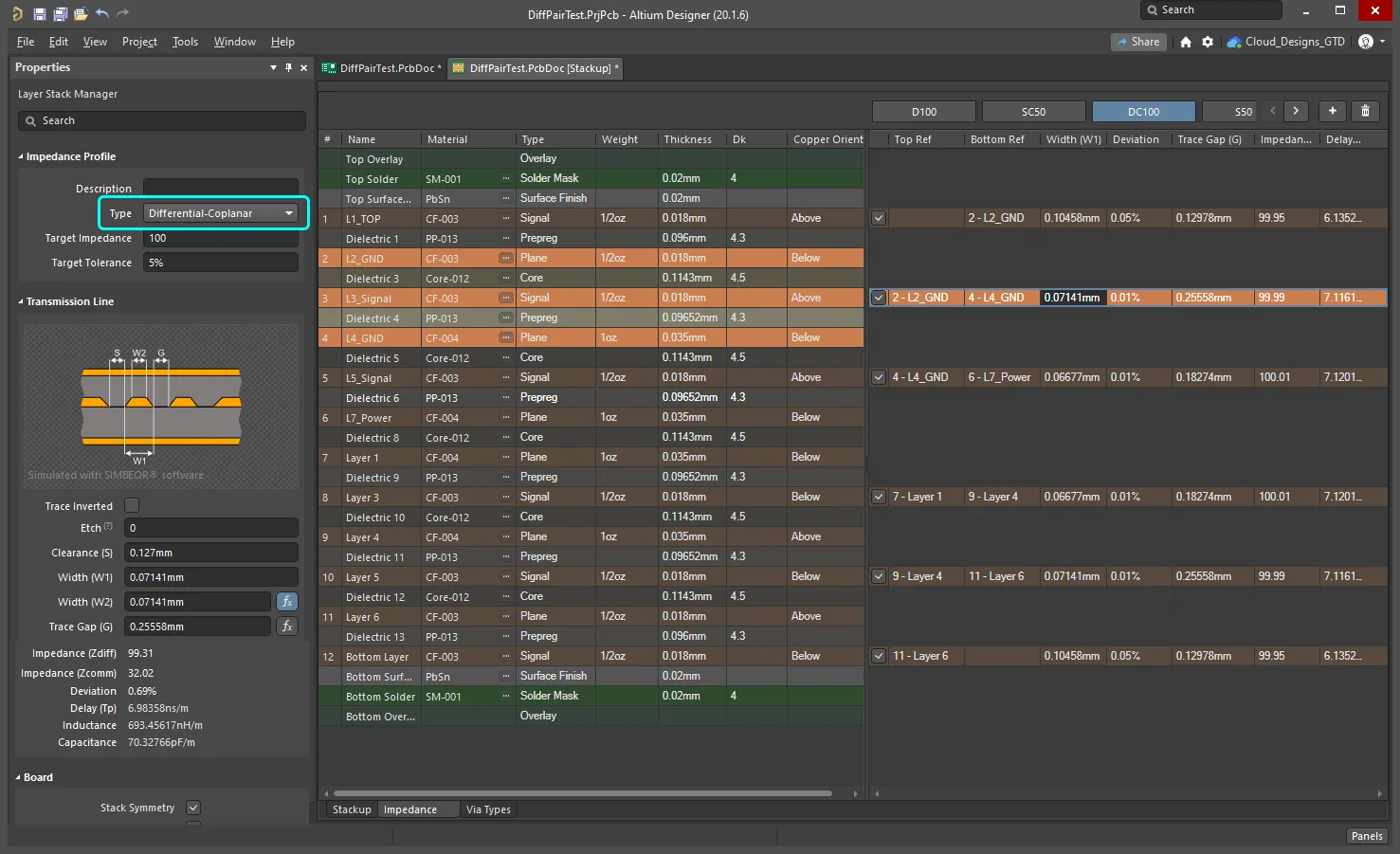

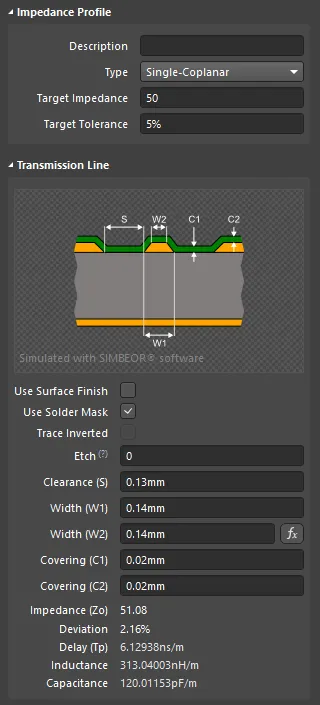

Поддержка структур копланарных линий передачи

Калькулятор импеданса в Layer Stack Manager поддерживает одиночные и дифференциальные копланарные структуры. Создайте новый профиль импеданса, затем выберите Single-Coplanar или Differential-Coplanar из раскрывающегося списка Type профиля импеданса.

Работа с копланарными структурами:

- Как и в случае стандартных одиночных и дифференциальных импедансов, значения для каждой переменной автоматически рассчитываются на основе заданных пользователем Target Impedance и Target Tolerance и физических свойств слоев платы. Эти автоматически рассчитанные значения можно скорректировать, введя новые значения в поля редактирования режима Layer Stack Manager панели Properties.

- Чтобы указать сигнальные цепи, которые должны трассироваться с копланарной структурой, настройте правило проектирования Routing Width (или Differential Pairs Routing) с включенной опцией Use Impedance Profile и выбранным требуемым профилем копланарного импеданса.

- Копланарные структуры требуют опорной плоскости по обеим сторонам сигнальной трассы; ее можно создать размещенным полигоном или, если добавляются stitching vias, с помощью команды Add Shielding to Net (подробнее ниже). Если вы размещаете полигон, зазор между этим полигоном и сигнальной трассой определяется значением Clearance (S), рассчитанным калькулятором импеданса Simbeor (отображается на панели Properties, показанной на изображениях выше и ниже). Настройте правило проектирования Clearance design rule, чтобы управлять зазором между опорным полигоном и сигнальной трассой (show image).

-

Обычной практикой является добавление ограждения из переходных отверстий вдоль каждой стороны сигнальной дорожки, когда копланарная структура заземлена. Для этого используйте команду Tools » Via Stitching/Shielding » Add Shielding to Net в редакторе PCB. Помимо размещения переходных отверстий, при включении опции Add shielding copper эта команда также может разместить полигон вокруг сигнальной трассировки, чтобы охватить ограждение из переходных отверстий, как показано на изображении справа внизу.

► Подробнее о Via Shielding

Калькулятор импеданса определяет свойства сигнала и зазоры (первое изображение); используйте этот зазор в настройке Distance для via shielding.

Калькулятор импеданса определяет свойства сигнала и зазоры (первое изображение); используйте этот зазор в настройке Distance для via shielding.

Выбор материала слоя

В проекте с контролируемым импедансом выбор материалов, используемых в стеке слоев, очень важен.

Например, наиболее распространенный материал для изготовления PCB — это эпоксидная смола, армированная стекловолокном (fiberglass), с медной фольгой, приклеенной с каждой стороны. Плотность плетения стеклоткани влияет на значение и стабильность диэлектрической постоянной Dk (проницаемости) и тангенса угла потерь Df. Вокруг тканого стекловолокна находится смола — процентное содержание смолы также важно для характеристик материала.

Существует широкий диапазон типов плетения стекловолокна. Чтобы повысить предсказуемость и характеристики материалов на основе стекловолокна, используемых при изготовлении PCB, IPC разработал стандарт для типов плетения:

IPC standard IPC-4412B: Specification for Finished Fabric Woven from "E" Glass for Printed Boards

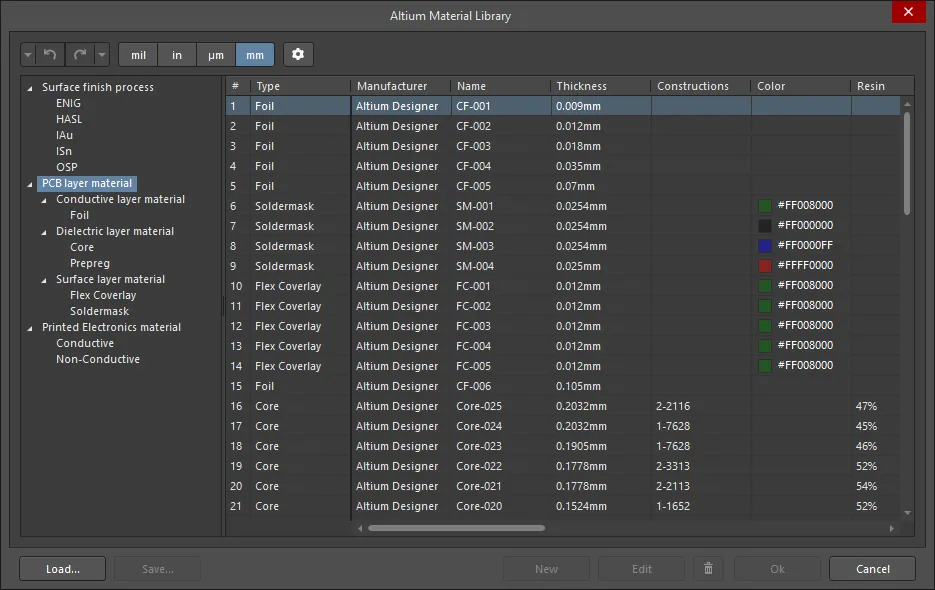

Библиотека материалов

Как разработчик, вы можете либо редактировать свойства материала непосредственно в Layer Stack Manager либо выбирать материалы из Altium Material Library.

Всю библиотеку можно просмотреть (и дополнить) в диалоговом окне Altium Material Library dialog (Tools » Material Library).

Материалы организованы по категориям использования, доступ к которым осуществляется через древовидную структуру в левой части диалогового окна. Ниже этого уровня каждая категория использования разбита на функциональные категории, такие как Conductive layer material, Dielectric layer material, и Surface Layer Material i в категории PCB layer material.

Добавление, сохранение и загрузка материала

Новый материал можно добавить в библиотеку, когда в дереве выбрана определенная категория материала. Материалы, определенные во внешней библиотеке материалов, можно загрузить (кнопка Load), а пользовательский материал, добавленный в диалоговом окне Altium Material Library, также можно сохранить в пользовательскую библиотеку (кнопка Save). Сохраняется только пользовательский материал.

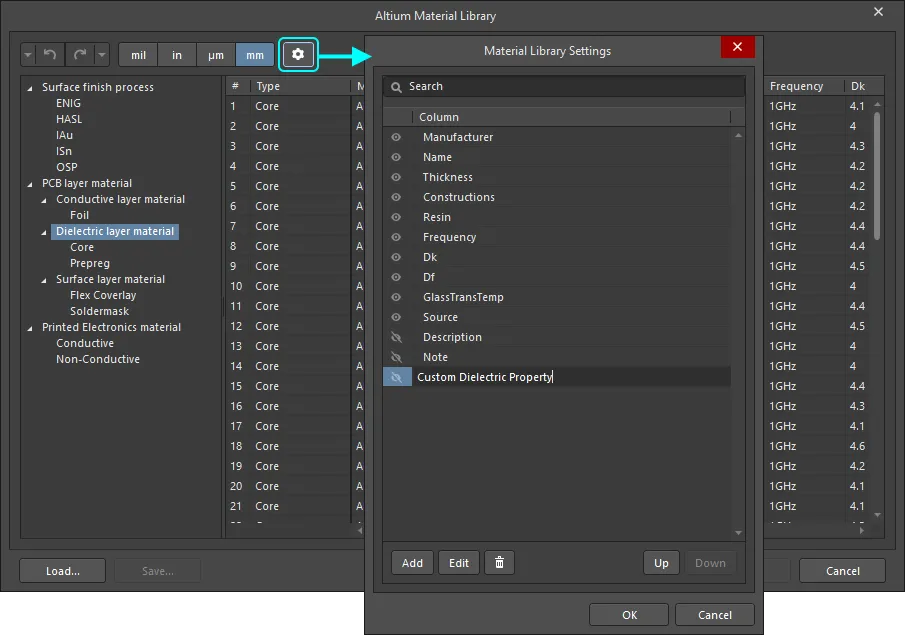

Добавление пользовательских свойств к материалу

К материалам, описанным в библиотеке (стандартным и пользовательским), можно добавлять пользовательские свойства. Чтобы добавить пользовательское свойство, сначала выберите правильный узел в дереве слева, чтобы определить материал(ы), к которым оно будет добавлено, затем нажмите кнопку ![]() , чтобы открыть диалоговое окно Material Library Settings.

, чтобы открыть диалоговое окно Material Library Settings.

Затем требуемое значение можно добавить к выбранному материалу в диалоговом окне Altium Material Library; выберите строку и нажмите кнопку Edit.

Панель Properties

Когда активна вкладка Impedance документа Layer Stack, панель Properties позволяет настроить требования к профилю импеданса. Затем нужный профиль импеданса можно выбрать в правилах проектирования Routing Width или Differential Pairs Routing.

-

Impedance Profile

- Description – введите понятное описание. Это поле необязательное и будет отображаться везде, где отображается имя профиля импеданса.

- Type – используйте раскрывающийся список, чтобы выбрать тип импеданса. Доступны варианты Single, Differential, Single-Coplanar и Differential-Coplanar.

- Target Impedance – введите импеданс, которого вы хотите достичь.

- Target Tolerance – введите допуск, которого вы хотите достичь. Следует проконсультироваться с изготовителем платы, чтобы определить реалистичное значение допуска, которое он может обеспечить.

-

Transmission Line

- Trace inverted – включите эту опцию, чтобы инвертировать дорожку, как показано на панели Properties. Эта опция совпадает с опцией Copper Orientation, отображаемой, когда активна вкладка Stackup, и определяет направление, в котором медь ламинируется на сердечник. Ориентация меди определяет направление, в котором медь выступает от этой подложки. Также это можно понимать как направление, с которого медь травится — сверху или снизу.

-

Etch – Etch Factor равен

= T/[(W1-W2)/2], что уменьшает общую площадь поперечного сечения дорожки на величину, равную квадрату толщины меди. Обратитесь к изготовителю платы за информацией о Etch, создаваемом его технологическими процессами.

-

Width (W1) / (W2) – W1 — это ширина трассируемой дорожки, W2 — ширина верхней поверхности этой дорожки после травления с учетом коэффициента Etch. Для ширины дорожки доступна функция прямого/обратного расчета. По умолчанию ширина рассчитывается на основе введенного вами Target Impedance (прямой расчет). Эта ширина может оказаться значением, которое изготовитель не сможет обеспечить, например 5.978, и ему потребуется более разумное значение, например 6.0. Вы можете ввести 6.0 в поле Width и нажать Enter на клавиатуре, чтобы пересчитать вычисляемые значения (Impedance, Deviation и т. д.). Кнопка

станет серой (неактивной), и вы перейдете в режим обратного расчета. Если нажать кнопку и снова сделать ее активной, вы вернетесь в прямой режим, а Width (W1) вернется к вычисленному значению. Эта функция позволяет исследовать реалистичные варианты ширины, пригодные для изготовления. При ручном вводе значения для W2 коэффициент травления будет обновлен соответствующим образом.

станет серой (неактивной), и вы перейдете в режим обратного расчета. Если нажать кнопку и снова сделать ее активной, вы вернетесь в прямой режим, а Width (W1) вернется к вычисленному значению. Эта функция позволяет исследовать реалистичные варианты ширины, пригодные для изготовления. При ручном вводе значения для W2 коэффициент травления будет обновлен соответствующим образом.

- Impedance – программное обеспечение рассчитывает импеданс на основе свойств материалов, используемых для изготовления платы (медь, core и prepreg), и площади поперечного сечения дорожки (определяемой шириной, толщиной и коэффициентом травления дорожки).

- Deviation – это мера различия между тем, что вы хотели получить (целевой импеданс), и тем, что получили (рассчитанный импеданс). Программное обеспечение рассчитывает отклонение импеданса (то, что вы фактически получите на основе введенных материалов и размеров) на основе свойств материалов, используемых для изготовления платы (медь, core и prepreg), и площади поперечного сечения дорожки (определяемой шириной, толщиной и коэффициентом травления дорожки).

- Delay – это время, необходимое сигналу для прохождения от передатчика к приемнику.

- Inductance – калькулятор импеданса использует значение Impedance для расчета индуктивности на единицу длины.

- Capacitance – калькулятор импеданса использует значение Impedance для расчета емкости на единицу длины.

-

Board

- Stack Symmetry – включите, чтобы добавлять слои согласованными парами, центрированными относительно среднего диэлектрического слоя. При включении стек слоев немедленно проверяется на симметрию относительно центрального диэлектрического слоя. Если какая-либо пара слоев, равноудаленных от центрального опорного диэлектрического слоя, не идентична, откроется диалоговое окно Stack is not symmetric dialog.

- Library Compliance – если включено, для каждого слоя, выбранного из Material Library, текущие свойства слоя проверяются на соответствие значениям определения этого материала в библиотеке.

- Substack – эта информация относится к текущему выбранному подстеку (слои, диэлектрик, толщины и т. д.). При переключении с одного подстека на другой эта информация будет соответствующим образом обновляться (для текущего выбранного подстека).

- Stack Name – введите понятное имя подстека. Это поле полезно, когда области стека X/Y назначается подстек слоев.

- Is Flex – включите, если подстек является гибким.

- Layers – общее количество слоев.

- Dielectrics – общее количество диэлектриков.

- Conductive Thickness – толщина проводящего(их) слоя(ев). Медные сигнальные слои называются проводящими слоями.

- Dielectric Thickness – толщина диэлектрического(их) слоя(ев).

- Total Thickness – общая толщина платы.

- Other

-

Roughness – показывает шероховатость проводящих слоев.

- Model Type – предпочтительная модель для расчета влияния шероховатости поверхности (дополнительные сведения о различных моделях см. в статьях ниже). Применяется ко всем медным слоям в стеке (возможно, должно быть к подстеку?).

- Surface Roughness – значение шероховатости поверхности (можно получить у вашего производителя). Введите значение от 0 до 10 мкм, по умолчанию — 0,1 мкм

- Roughness Factor – характеризует ожидаемое максимальное увеличение потерь в проводнике из-за эффекта шероховатости. Введите значение от 1 до 100; значение по умолчанию — 2.

Настройка правил проектирования

Импеданс трассировки определяется шириной и высотой трассы, а также свойствами окружающих диэлектрических материалов. На основе свойств материалов, заданных в Layer Stack Manager, требуемая ширина трассировки рассчитывается при создании каждого профиля импеданса. В зависимости от свойств материалов ширина может изменяться при смене слоя трассировки. Это требование, при котором ширина меняется при смене слоев трассировки, автоматически обрабатывается соответствующим правилом проектирования трассировки, настроенным в PCB Rules and Constraints Editor (Design » Rules).

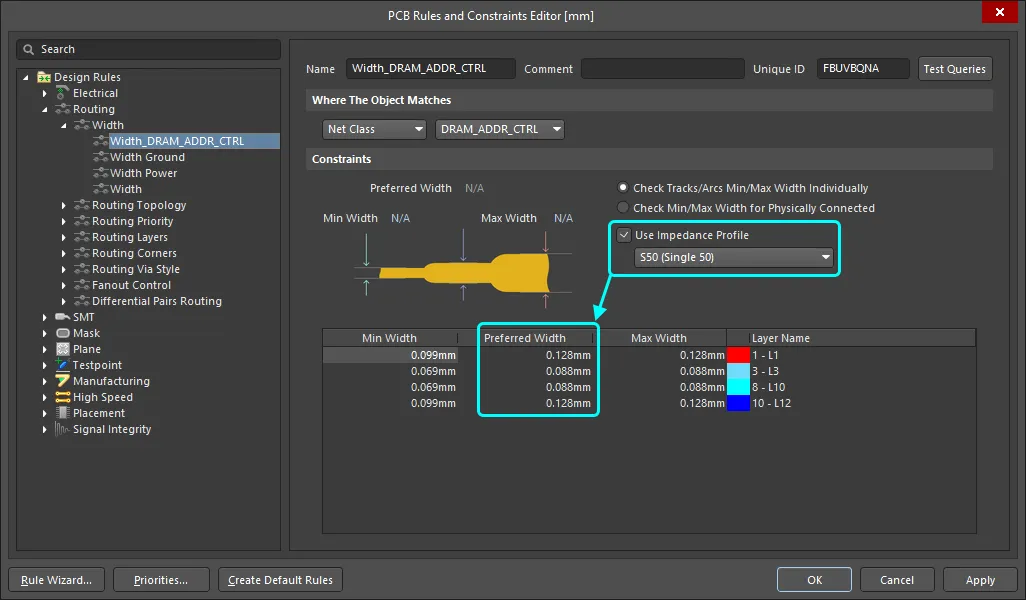

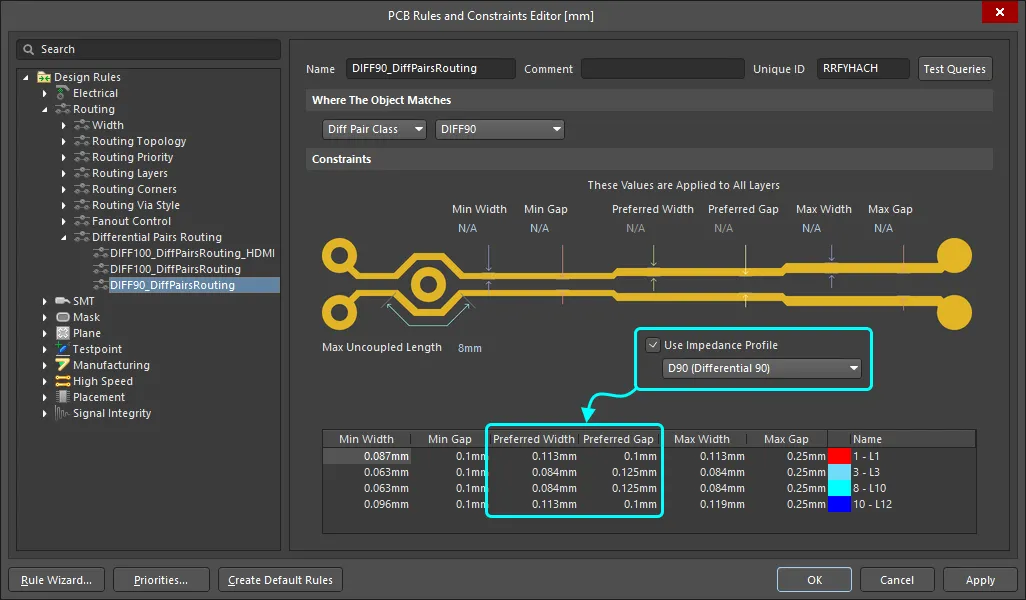

Для большинства проектов плат определенный набор цепей трассируется с контролируемым импедансом. Распространенный подход — создать класс цепей или класс дифференциальных пар, включающий эти цепи, а затем создать правило трассировки, нацеленное на этот класс, как показано на изображениях ниже.

Обычно вы вручную задаете Min, Max и Preferred Widths либо в верхних настройках ограничений, чтобы применить их ко всем слоям, либо отдельно для каждого слоя в сетке слоев. Для трассировки с контролируемым импедансом вместо этого включите параметр Use Impedance Profile, затем выберите требуемый профиль импеданса из раскрывающегося списка. После этого область Constraints правила изменится. Первое, что вы заметите, — область доступных слоев больше не будет показывать все сигнальные слои платы. Теперь будут отображаться только слои, включенные в выбранный профиль импеданса. Значения Preferred Width (и зазор дифференциальной пары) обновятся в соответствии с ширинами (и зазорами), рассчитанными для каждого слоя. Эти предпочтительные значения нельзя редактировать, но значения Min и Max можно. Установите для них подходящие меньшие/большие значения. После этого цепи можно интерактивно трассировать обычным способом.

Правило проектирования ширины трассировки

Для одиночных цепей ширина трассировки определяется правилом проектирования Routing Width.

Если вы выбираете Use an Impedance Profile, доступные слои и предпочтительные ширины управляются выбранным профилем.

Если вы выбираете Use an Impedance Profile, доступные слои и предпочтительные ширины управляются выбранным профилем.

Правило проектирования трассировки дифференциальных пар

Трассировка дифференциальных пар управляется правилом проектирования Differential Pair Routing.

Для дифференциальной пары доступные слои, предпочтительная ширина и предпочтительный зазор управляются выбранным профилем.

Для дифференциальной пары доступные слои, предпочтительная ширина и предпочтительный зазор управляются выбранным профилем.

► Подробнее о Differential Pair Routing

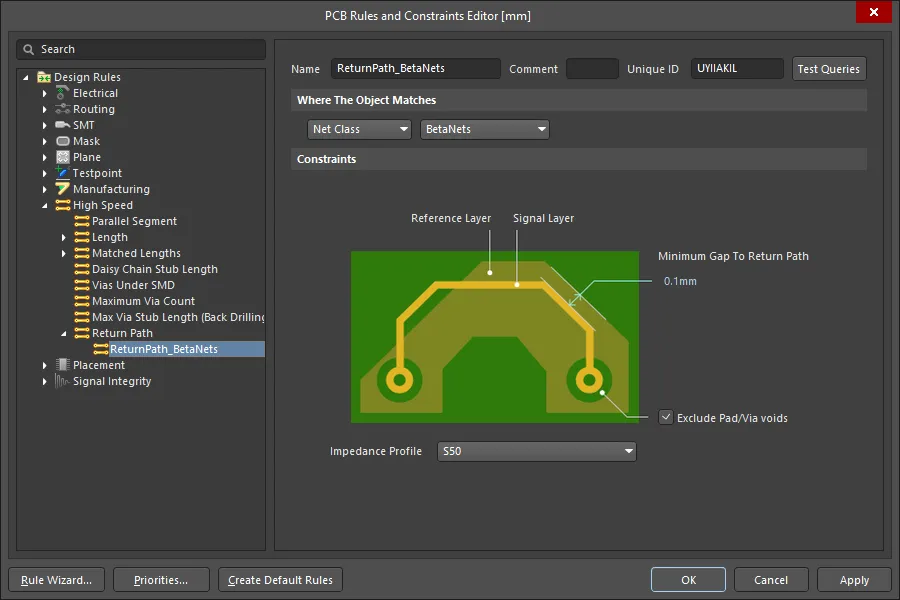

Правило проектирования обратного пути

Разрывы или сужения в обратном пути могут быть обнаружены правилом проектирования Return Path design rule. Правило Return Path проверяет наличие непрерывного обратного пути сигнала на назначенном(ых) опорном(ых) слое(ях) выше или ниже сигнала(ов), на которые нацелено правило. Обратный путь может быть создан заливками, областями и полигональными заливками, размещенными на опорном сигнальном слое или слое-плоскости.

Слои обратного пути — это опорные слои, определенные в Impedance Profile, выбранном в правиле проектирования Return Path. Эти слои проверяются, чтобы убедиться, что вдоль пути сигнала существует указанный Minimum Gap (ширина за пределами края сигнала). Добавьте новое правило проектирования Return Path в категории правил High Speed.

Слои обратного пути определяются в выбранном Impedance Profile, а ширина пути (за пределами края сигнала) задается параметром Minimum Gap.

Слои обратного пути определяются в выбранном Impedance Profile, а ширина пути (за пределами края сигнала) задается параметром Minimum Gap.

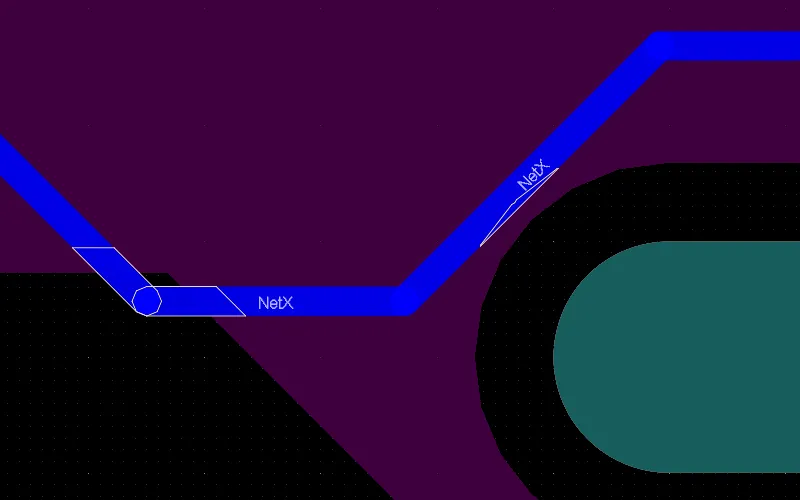

На изображении ниже показаны ошибки обратного пути, обнаруженные для сигнала NetX при значении параметра Minimum Gap, равном 0.1mm. Ошибки Return Path может быть проще находить, если настроить DRC Violation Display Style на отображение Violation Details, но не Violation Overlay ( show image) в диалоговом окне Preferences. Это позволяет выделять точные места, где правило не выполнено, а не весь объект(ы) с нарушением.

► Подробнее о High Speed Design in Altium Designer

Трассировка цепей с требуемым импедансом

По мере трассировки платы и смены слоев программное обеспечение будет автоматически подстраивать ширину дорожки до размера, необходимого для достижения заданного импеданса. Такая интерактивная трассировка с контролируемым импедансом значительно упрощает задачу проектирования печатной платы с контролируемым импедансом.

Подстройка длины трасс

Две основные задачи при трассировке высокоскоростного проекта — это контроль импеданса трасс и согласование длин критически важных цепей. Трассировка с контролем импеданса гарантирует, что сигнал, выходящий с выходного вывода, будет корректно принят целевыми входными выводами. Согласование длин трасс гарантирует, что критичные по времени сигналы прибудут на свои целевые выводы одновременно. Подстройка и согласование длин трасс также являются важнейшей составляющей трассировки дифференциальных пар.

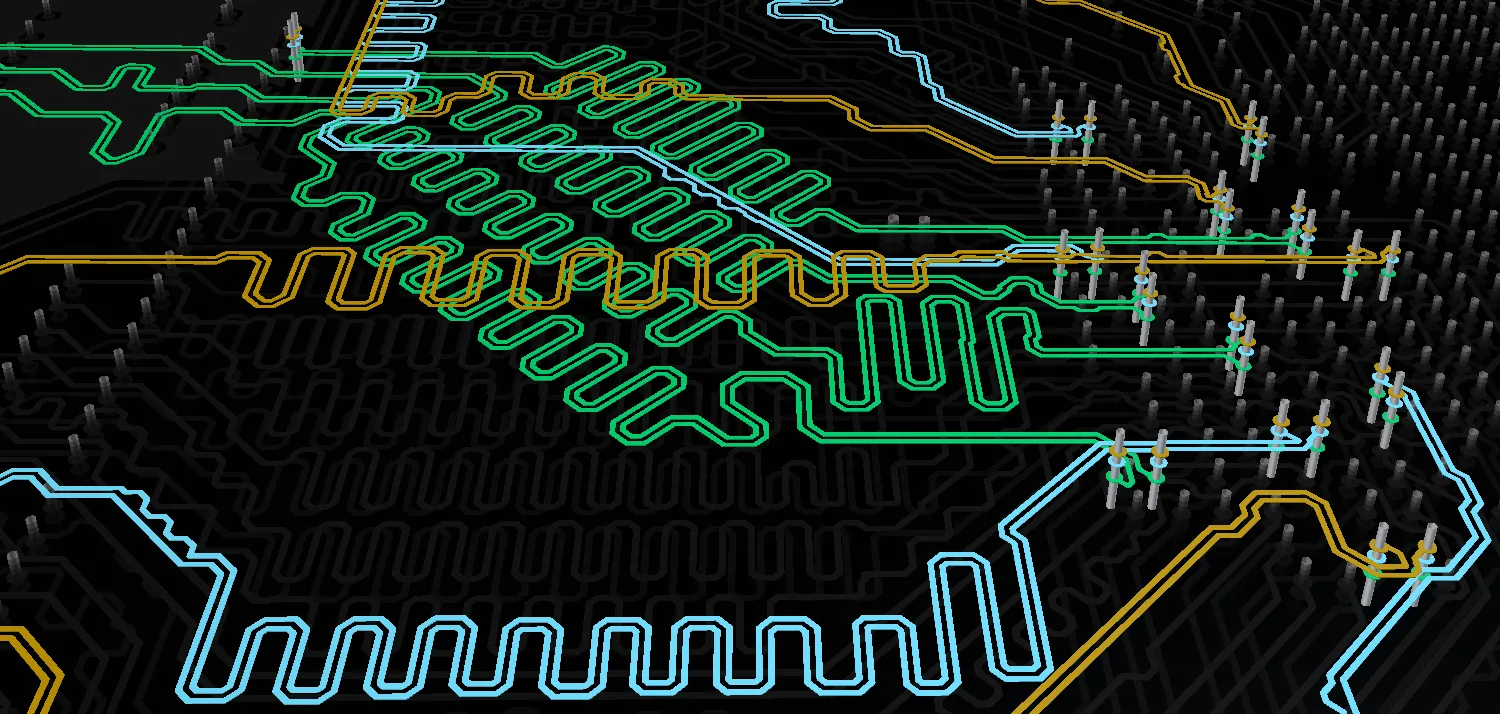

В трассировку были добавлены шаблоны типа «аккордеон», чтобы обеспечить согласование длин дифференциальных пар.

В трассировку были добавлены шаблоны типа «аккордеон», чтобы обеспечить согласование длин дифференциальных пар.

Команды Interactive Length Tuning и Interactive Diff Pair Length Tuning (меню Route) предоставляют динамический способ оптимизации и управления длинами цепей или дифференциальных пар, позволяя вставлять волнообразные шаблоны переменной амплитуды («аккордеоны») в соответствии с доступным пространством, правилами и препятствиями в вашем проекте.

► Подробнее о Length Tuning

Проверка целостности сигнала на разведенной плате

Точно так же, как вы проверяли цепи во время захвата схемы, используя предполагаемую длину трассировки и импеданс трассировки, после завершения трассировки следует повторить этот процесс на плате, чтобы проверить возможные несоответствия импеданса и проблемы с отражениями. Запустите команду Signal Integrity из меню Tools редактора PCB. Поскольку PCB является частью проекта, свойства материалов и размеры, определенные в Layer Stack Manager, а также фактические ширины трасс на плате будут использоваться для расчета импедансов, применяемых при тестах целостности сигнала.

Достижение заданных импедансов

Помимо итеративного процесса подбора размеров, через который вы проходите для достижения правильных импедансов, существуют и другие факторы, влияющие на итоговый импеданс, который будет достигнут на изготовленной печатной плате. К ним относятся однородность и стабильность диэлектрического материала, используемого в PCB, а также стабильность и качество процесса травления. Если вам требуется PCB с контролируемым импедансом, вам следует обсудить это с вашим производителем печатных плат. Некоторые производители могут дать рекомендации по геометрии дорожек, если вы предоставите им предпочитаемый стек слоев. Многие также смогут включить в каждую изготавливаемую панель тестовый купон импеданса — его можно использовать для измерения реальных импедансов, достигнутых на плате.

Дополнительное чтение и ресурсы

Эта статья дает введение в тему целостности сигнала и проектирования печатных плат с контролируемым импедансом. Воспользуйтесь следующими ссылками, чтобы узнать больше и получить доступ к ресурсам, разработанным признанными отраслевыми экспертами.

Локализовано с помощью ИИ

Локализовано с помощью ИИ