Siemens EDA® PADS™ 소프트웨어 설계(예: PADS Logic 회로도, PADS Layout PCB 파일, 라이브러리 파일)는 모두 Altium Designer의 Import Wizard로 처리할 수 있습니다. Import Wizard는 가져온 파일을 분석하고 프로젝트 구조, 레이어 매핑, PCB 풋프린트 명명 등과 관련된 기본값 및 권장 설정을 제안함으로써, 설계 변환 시 흔히 겪는 번거로움을 크게 줄여줍니다. Wizard 단계에서 제공되는 유연성을 통해 실제 변환을 실행하기 전에 파일 변환 설정을 사용자가 제어할 수 있습니다.

PADS 파일 가져오기

PADS 설계 파일 가져오기 도구는 Altium Designer의 Import Wizard (File » Import Wizard)에서 Wizard의 PADS ASCII Design and Library Files 옵션을 Select Type of Files to Import 페이지에서 선택하여 사용할 수 있습니다. Wizard는 회로도/PCB 설계 파일과 라이브러리 파일을 모두 지정할 수 있는 옵션을 제공하며, PADS에서 Altium Designer로의 PCB 가져오기 옵션도 제공합니다.

PADS 설계 파일을 가져오려면 PADS ASCII Design and Library Files를 선택하십시오.

PADS 설계 파일을 가져오려면 PADS ASCII Design and Library Files를 선택하십시오.

Import Wizard - PADS ASCII Design and Library Files

PADS ASCII Design and Library Files

Wizard로 가져온 PADS 설계는 Altium Designer에서 변환 후 자동으로 생성되는 개별 PCB 프로젝트 내 문서로 저장됩니다. 변환 중 발생한 오류는 확장자가 *.LOG인 로그 파일에 보고됩니다.

Wizard는 PADS ASCII 버전 5.2 이상만 변환하며 PADS 바이너리 파일은 읽지 않습니다. 바이너리 PADS 파일만 있는 경우, PADS 애플리케이션에서 해당 바이너리 파일을 ASCII 형식으로 내보내야 하며, 가능하면 ASCII 2005.2 형식을 권장합니다.

Importing PADS Designs

Add을(를) 클릭하여 프로세스에 포함할 PADS 설계 파일을 선택하십시오. 선택한 파일은 Remove을(를) 클릭하여 삭제할 수 있습니다.

Importing PADS Libraries

Add을(를) 클릭하여 프로세스에 포함할 PADS 라이브러리 파일을 선택하십시오. 선택한 파일은 Remove을(를) 클릭하여 삭제할 수 있습니다.

Reporting Options

Reporting Options 페이지에서 일반 로그 보고 옵션을 설정하십시오.

General Settings에서 원하는 옵션(Log All Errors, Log All Warnings, Log All Events)을 활성화하십시오.

원하는 경우 Do not translate hidden net names을(를) 활성화하십시오.

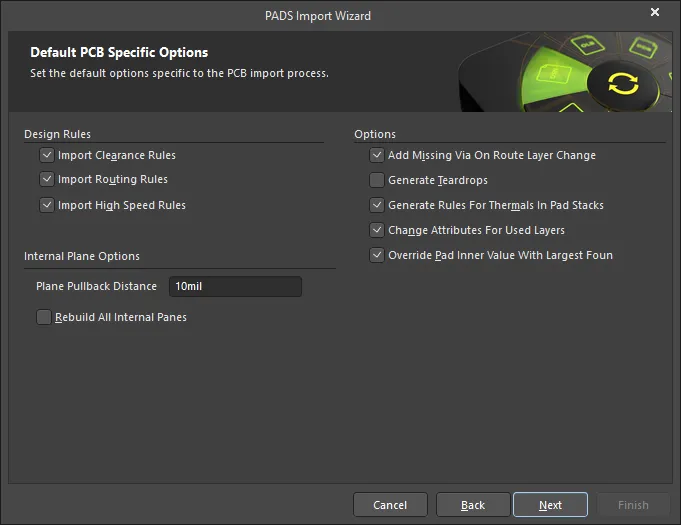

Default PCB Specific Options

Default PCB Specific Options 페이지는 PCB 및 PCB 라이브러리 가져오기 프로세스 모두에 적용되는 기본 옵션을 설정하는 데 사용됩니다.

Design Rules 아래의 옵션을 활성화하여 가져올(또는 가져오지 않을) 설계 규칙을 지정하십시오.

텍스트 상자에 원하는 Plane Pullback Distance을(를) 지정하십시오. 체크박스를 활성화하여 Rebuild All Internal Planes하십시오.

원하는 추가 Options의 체크박스를 활성화하십시오.

Current PCB and PCB Library Options

Wizard의 이 페이지에서 출력 프로젝트 구조를 검토하고 PADS PCB 및 PCB 라이브러리 파일을 가져올 출력 디렉터리를 지정하십시오. Browse Folder 아이콘을 사용하여 Project Output Directory을(를) 검색하고 선택하십시오.

Menu을(를) 클릭하여 프로젝트 구조를 편집하는 옵션에 접근하십시오:

PCB Projects 영역에서 마우스 오른쪽 버튼을 클릭하면 Menu 버튼을 클릭했을 때와 동일한 메뉴 및 하위 메뉴에 접근할 수 있습니다.

Output PCB Projects

Wizard의 이 페이지에서 출력 프로젝트 구조를 검토하고 파일을 가져올 출력 디렉터리를 지정하십시오. Browse Folder 아이콘을 사용하여 Library Output Directory을(를) 검색하고 선택하십시오.

Closing the Wizard

PADS Import Wizard가 완료되었습니다. Finish을(를) 클릭하여 Wizard를 닫으십시오.

Imported PADS Files:

Wizard는 하나의 logic 파일 내 각 PADS Logic 시트마다 Altium Designer 회로도 문서 1개를 생성합니다. 변환된 각 logic 파일은 *.PrjPCB 파일 확장자를 가진 자동 생성 Altium Designer PCB 프로젝트로 그룹화됩니다.

가져온 파일은 다음과 같이 변환됩니다:

-

확장자가

*.TXT인 Logic 파일 내 PADS ASCII Schematic Logic 시트는 확장자가 *.SchDoc인 Altium Designer 회로도 파일로 변환됩니다.

파일 변환

Import Wizard가 PADS Logic 회로도와 PADS Layout PCB 파일을 Altium Designer 형식 파일로 변환하려면, 두 파일 모두 ASCII 파일이어야 합니다.

가져온 PADS 파일은 다음과 같이 변환됩니다:

-

PADS Layout (*.ASC) ASCII PCB 파일은 Altium Designer PCB 파일(*.PcbDoc)로 변환됩니다.

-

PADS Logic (*.TXT) ASCII 회로도 파일은 Altium Designer 회로도 파일로 변환됩니다. .TXT 파일 내 각 회로도 페이지는 단일 Altium Designer 회로도 파일(*.SchDoc)로 가져와집니다.

-

PADS 라이브러리(*.c) 회로도 심볼 파일은 PADS (*.p) 파라메트릭 부품 데이터 파일과 결합되어 Altium Designer 회로도 라이브러리 파일(*.SchLib)로 변환됩니다.

-

PADS PCB 라이브러리(*.d) PCB 데칼 파일은 Altium Designer PCB 라이브러리 파일(*.PcbLib)로 변환됩니다.

-

변환된 PADS 회로도와 PCB 파일은 자동으로 하나의 PCB 프로젝트로 그룹화되지 않으며, 회로도용 프로젝트 1개와 PCB용 프로젝트 1개가 각각 생성됩니다.

► PADS에서 올바른 ASCII 파일 세트를 만드는 방법을 더 알아보려면 PADS Migrating Guide를 확인하십시오.

► Wizard는 PADS Logic 및 Layout 파일의 어떤 버전을 지원합니까?

한 도구에서 다른 도구로의 마이그레이션은, 원본 도구의 객체를 가져오기 도구로 변환하는 데 따르는 제약을 받습니다. 모든 객체 유형을 변환하는 것이 항상 가능한 것은 아닙니다. Altium은 Import Wizard's design file converters를 지속적으로 개선하므로, 가져오기 중 문제가 발생하면 Altium Designer가 최신 빌드로 업데이트되어 있는지 확인하십시오. 이는 더 나은 버전 호환성과 더 정확한 가져오기 결과로 이어질 수 있습니다.

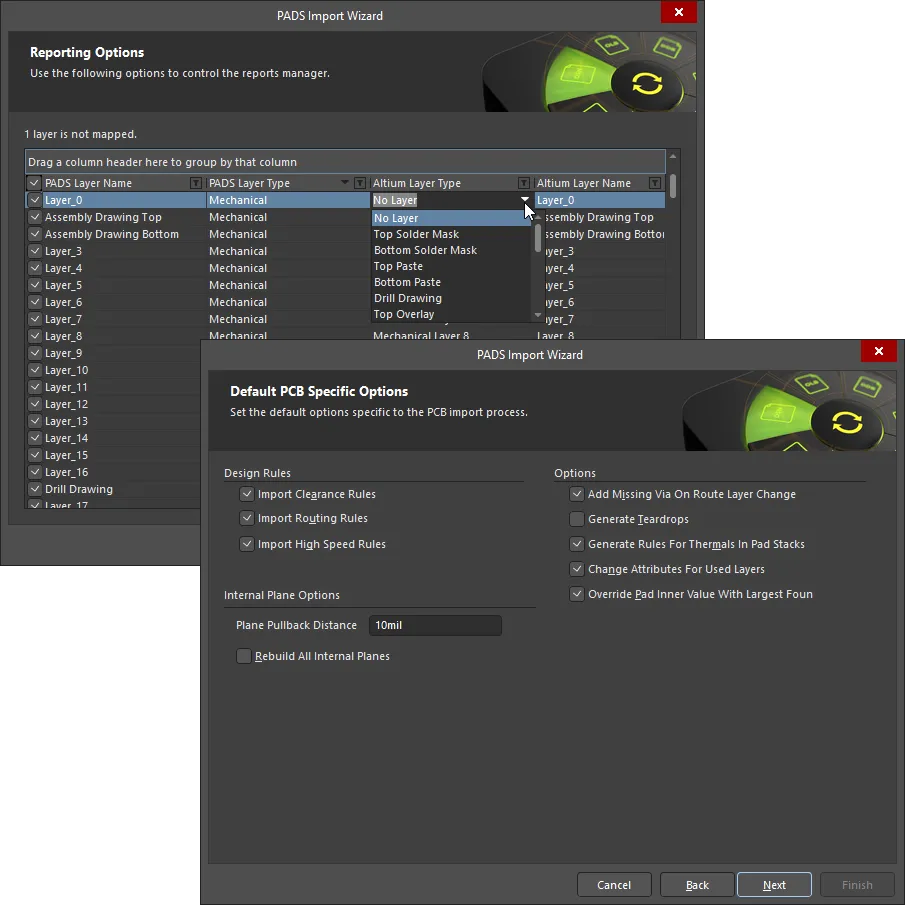

PADS PCB ASCII 파일의 레이어 매핑

Import Wizard을(를) 사용할 때는 가져오기 전에 사용된 모든 PADS PCB 레이어를 Altium Designer 레이어에 매핑해야 합니다. 또한 설계 규칙의 자동 생성, 누락된 비아, keep-out 변환을 제어하기 위한 추가 옵션도 제공됩니다.

Import Wizard의 레이어 매핑 옵션을 사용하여 PADS PCB 레이어를 Altium Designer 레이어에 연결하십시오.

PCB 설계를 가져올 때 레이어가 어떻게 매핑되는지에 유의해야 합니다. 레이어 매핑은 PADS PCB 레이어 이름과 Altium Designer PCB 레이어 간의 단순한 매핑입니다. 물론 제안된 기본 매핑만 제공되므로 원하는 만큼 매핑을 변경할 수 있습니다. 이 매핑은 Import Wizard에서 각 PCB에 대한 레이어 매핑을 구성하는 데 사용되며, 이후 개별적으로 사용자 지정할 수 있습니다. 예를 들어 PCB 설계 10개를 가져오면서 Assembly 1 레이어를 Mechanical Layer 1로 매핑하려는 경우, 올바른 레이어 매핑을 위해 10개 PCB 설계를 각각 따로 사용자 지정할 필요가 없도록 하기 위한 것입니다.

이 방식으로 가져오면 레이어 매핑을 일괄 관리할 수 있어 여러 설계를 가져올 때 시간을 크게 절약할 수 있습니다. 이 경우 기본 레이어 매핑은 Preferences에 저장됩니다. 단점은 설계마다 구조가 다를 때 Default Layer Mapping이 항상 지능적으로 동작하지는 않으므로, 이후 수동 변경이 필요할 수 있다는 점입니다. 상황에 맞는 최적의 방법을 선택해야 합니다.

넷 이름 옵션

PADS Logic에서는 넷 연결이 와이어의 속성인 넷 이름을 통해 이루어집니다. 사람이 지정한 넷 이름이 없는 와이어에는 $$$13654과 같은 시스템 생성 넷 이름이 부여됩니다. Altium Designer는 사람이 정의한 이름이 없는 넷을 식별하는 방식이 다르며, 예를 들어 NetC15_1처럼 넷 내 특정 핀을 기반으로 시스템 할당 이름을 생성합니다.

PADS 회로도를 가져오는 동안 Wizard에는 Do not translate hidden net names 옵션이 포함됩니다. 시스템 생성 이름이 그대로 가져와지지 않도록 이 옵션을 활성화된 상태로 유지하는 것을 권장합니다. 그러면 Altium Designer가 자체 시스템 생성 넷 식별자를 사용합니다.

Do not translate hidden net names를 그대로 두십시오. 그러면 Altium Designer가 대신 넷 이름을 생성할 수 있습니다.

Do not translate hidden net names를 그대로 두십시오. 그러면 Altium Designer가 대신 넷 이름을 생성할 수 있습니다.

가져온 문서 작업

PADS Logic에서는 모든 설계 작업이 페이지에서 시작되며, 페이지는 설계의 논리적 작업 영역입니다. 하나의 PADS 회로도 설계 파일 안에 여러 회로도 페이지가 있을 수 있습니다.

PADS Layout에서는 모든 설계 작업이 워크스페이스에서 시작되며, 이는 PCB 설계의 논리적 작업 영역입니다. 각 설계는 단일 설계 파일(*.PCB 파일)로 저장됩니다. 또한 물리적 설계 재사용 파일(*.REU)이 있어 PCB 설계의 일부/부분집합을 보존하여 동일 설계 내 또는 다른 설계에서 재사용할 수 있지만, 이러한 파일은 무시되며 변환되지 않습니다.

Altium Designer에서 논리 설계 영역은 ‘문서(document)’에서 시작하며, 각 문서마다 하드 드라이브에 저장되는 파일이 하나씩 존재합니다. 즉, Altium Designer의 각 회로도 시트(페이지)는 회로도 문서 파일로 표현되며, 이는 반드시 기억해야 할 중요한 개념적 차이입니다. 또한 Altium Designer 프로젝트에는 설계 프로젝트의 성격에 따라 (회로도 및 PCB 설계 문서 외에도) 다양한 유형의 문서가 여러 개 포함될 수 있습니다.

Object Translation Limitations

-

PADS Logic: 개별 핀 타입 커넥터는 지원되지 않습니다. 이는 다음 중 하나로 처리해야 합니다. PADS에서 모든 핀이 하나의 회로도 컴포넌트에 들어가도록 블록 스타일 커넥터로 변환하거나, 또는 변환 이후(translation 후) 해당 in-type 커넥터를 Altium 커넥터 컴포넌트로 변환해야 합니다.

-

PADS Layout: Physical Design Resuse 블록은 지원되지 않습니다. 내보내기/가져오기 전에 PADS에서 이를 개별 파트로 분해해야 합니다. PADS Layout에서 해당 블록을 마우스 오른쪽 버튼으로 클릭하고 Break Reuse을(를) 선택하여 수행합니다.

Panels

Altium Designer 환경의 핵심 기능 중 하나는 Projects panel과 같은 패널입니다. Altium Designer에서 Projects 패널은 회로도 설계 데이터에만 국한되지 않으며, PCB, 모든 라이브러리, 출력 파일, 그리고 비네이티브 파일(PDF, 텍스트 파일, 스프레드시트, 등)과 같은 기타 프로젝트 문서도 포함할 수 있습니다. Altium Designer 패널은 애플리케이션 오른쪽 하단에 있는  버튼을 사용해 표시할 수 있습니다.

버튼을 사용해 표시할 수 있습니다.

The Schematic Symbol is the Part

PADS Layout 숙련 사용자라면, PADS Layout에서 파트(parts)가 설계의 기본 구성 요소라는 것을 알고 있을 것입니다. 파트는 파트 타입, 로직 패밀리, 핀 수, 게이트 수, 신호 핀을 갖는 것으로 정의됩니다. ‘컴포넌트(component)’라는 용어는 해당 파트가 PCB 레이아웃 설계에서 물리 객체로 배치될 때에만 사용됩니다.

PADS Layout(PCB)에서 하나의 파트는 하나 이상의 물리 컴포넌트를 나타낼 수 있습니다. PCB 설계에서 파트는 보통 게이트, 칩, 커넥터처럼 패키지로 제공되는 물리 객체에 대응하며, 하나 이상의 파트로 구성된 패키지 형태의 객체도 있습니다. 다중 파트 패키지는 하나 이상의 파트로 구성된 물리 객체입니다.

설계 맥락에 따라 동일한 용어가 서로 다른 정의로 사용되기 때문에, ‘component’라는 용어를 사용하는 새로운 환경에서는 처음에 다소 혼란이 생길 수 있습니다. 하지만 Altium Designer에서도 동작 방식은 크게 다르지 않으며, 차이점은 회로도 심볼이 설계의 모든 단계에서 사실상 ‘파트’ 역할을 한다는 점입니다(PCB Layout 단계에서만이 아니라).

Altium Designer에서는 논리 심볼이 컴포넌트의 필수적인 시작점이라고 가정합니다. 처음에는 회로도 라이브러리에서 최소한 이름으로 정의할 수 있으며, 이후 구현에 필요한 핀과 그래픽 심볼, 또는 대체 표시 옵션 등을 추가할 수 있습니다. 이러한 유연성 덕분에 컴포넌트는 설계 및 캡처 과정에서 다양한 방식으로 표현될 수 있습니다. 이는 회로도 상의 논리 심볼뿐 아니라 PCB의 풋프린트, 심지어 시뮬레이션을 위한 SPICE 정의일 수도 있습니다.

Altium Designer Libraries

Altium Designer의 통합 라이브러리(integrated library)는 소스 심볼, 풋프린트, 그리고 기타 모든 정보(예: SPICE 및 기타 모델 파일)가 하나의 파일로 컴파일되어 포함된 라이브러리입니다. 컴파일 중에는 관계가 어떻게 정의되어 있는지 확인하고, 모델과 심볼 간의 관계를 검증한 뒤 이를 하나의 통합 라이브러리로 묶습니다. 이 파일은 컴파일 후에는 직접 편집할 수 없으므로, 이식성과 보안성이 제공됩니다.

PADS Object

|

Altium Designer Object

|

Comments

|

Decal

|

Footprint

|

PCB에 장착될 컴포넌트에 대해 정의된 형상의 그래픽 표현입니다. 이는 2차원 표현만을 의미하며, 실제 컴포넌트 자체와는 상당히 다를 수 있습니다.

|

Part

|

Part/Component

|

Altium Designer에서 Part라는 용어는 설계 캡처(회로도) 과정에서만 사용됩니다. PCB 파일에 풋프린트로 배치되면, 설계자(designator)와 값(value, comment)이 부여되며 컴포넌트가 됩니다.

|

Lines

|

Lines

|

그래픽 정보를 위한 프리미티브 객체입니다.

|

CAE Decal

|

Schematic symbol

|

NOR 게이트와 같은 회로도 파트의 그래픽 표현입니다.

|

더 자주 사용되는 PADS 라이브러리 용어와 이에 가장 가까운 Altium Designer 대응 용어를 정리한 표입니다.

Working with the Imported Schematic

Check for Net Shorts

PADS에서는 넷 이름이 와이어의 속성(attribute)인 반면, Altium Designer에서는 와이어에 닿도록 Net Label 객체를 배치하여 넷에 이름을 지정합니다. PADS는 사람이 정의한 넷 이름을 와이어의 중간 지점에 자동으로 표시합니다. 흔한 경우는 아니지만, PADS 회로도를 가져올 때 Altium Designer의 Net Label이 서로 다른 두 넷의 교차 지점(cross-over point)에 정확히 위치할 수 있습니다. Net Label의 접속점은 왼쪽 아래 모서리(핫스팟이라고도 함)이므로, Altium Designer에서는 이로 인해 두 넷이 서로 연결되어 버릴 수 있습니다.

가져온 회로도를 항상 육안으로 확인하고, 각 Net Label의 위치가 적절한지 확인하십시오. Net Label을 클릭하여 드래그해 적절한 위치로 옮기되, 왼쪽 아래 모서리가 이름을 지정하려는 넷의 와이어에 닿도록 하십시오.

► Creating Connectivity in your Schematics에 대해 더 알아보기.

Altium Designer에서는 Alt 키를 누른 채로 해당 넷의 어떤 요소든 마우스 왼쪽 버튼으로 클릭하면, 그 넷에 연결된 모든 요소를 하이라이트할 수 있습니다.

Validating the Schematic

Altium Designer는 회로도에서 컴포넌트 및 연결 정보를 자동으로 추출하여, 메모리 내에 설계의 포괄적인 모델을 구축하는데 이를 Unified Data Model라고 합니다. 이 데이터 모델은 회로도 검증, 회로도-보드 동기화, BOM 생성, 회로 시뮬레이션과 같은 분석 작업에 사용됩니다.

회로도를 PCB와 동기화하기 전에, 연결 문제(connective issues)가 없는지 확인하기 위해 회로도를 검증(Validate)하는 것이 중요합니다. 이를 위해 Project » Validate PCB Project <ProjectName> 명령을 실행하십시오. 검증 결과는 Messages 패널에 표시됩니다.

검증 옵션은 Options for PCB Project <ProjectName> 대화상자에서 설정합니다(Project » Project Options 선택). Error Reporting 및 Connection Matrix 탭의 설정을 검토하십시오.

► Validating Your Design Project에 대해 더 알아보기.

Schematic to PCB Synchronization

동일한 PCB 설계의 회로도와 보드를 모두 가져오는 경우, 이를 하나의 Altium Designer 프로젝트로 결합해야 합니다. Import Wizard는 가져온 회로도가 가져온 보드와 동일한 설계에 속한다고 가정하지 않으므로, 설계자가 이를 설정해야 합니다. Wizard는 가져온 회로도에 대해 하나의 Altium *.PrjPcb 프로젝트를 만들고, 가져온 PCB에 대해 또 다른 *.PrjPcb 프로젝트를 만듭니다. 각 프로젝트는 원본 PADS 파일과 같은 폴더에 있는 하위 폴더(child folder)에 생성됩니다. 회로도를 보드와 동기화하기 전에, 회로도(들)와 보드는 반드시 동일한 프로젝트에 속해야 합니다.

Creating a Single Project

모든 PADS 파일을 가져온 후에는, Altium Designer에서 두 프로젝트를 모두 닫고 Windows 파일 탐색기를 사용하여 회로도를 PCB와 같은 폴더로 옮기거나, PCB를 회로도와 같은 폴더로 옮기는 것을 권장합니다. 그런 다음 완전한 프로젝트가 될 프로젝트를 다시 열고, Altium Designer Projects 패널에서 프로젝트 이름을 마우스 오른쪽 버튼으로 클릭한 뒤 컨텍스트 메뉴에서 Add Existing to Project 명령을 선택하십시오. 추가해야 할 파일을 찾아 선택하고 Open 버튼을 클릭하여 Choose Documents 대화상자를 닫습니다.

이제 프로젝트에는 회로도와 PCB가 모두 포함됩니다.

► Managing Project Documents에 대해 더 알아보기.

Configuring the Project Options

회로도 시트와 PCB는 프로젝트에 속합니다. 프로젝트 옵션은 Options for PCB Project <ProjectName> dialog에서 설정합니다(Project » Project Options).

이 대화상자의 다음 탭들은 회로도-PCB 동기화 중에 사용됩니다.

-

Class Generation - 자동 넷/컴포넌트 클래스 생성, 룸(room) 생성 등의 옵션을 설정하는 데 사용됩니다. 컴포넌트 배치 룸을 특별히 사용하려는 목적이 아니라면 Generate Rooms 체크박스를 비활성화하는 것을 권장합니다. 또한 각 회로도 시트의 컴포넌트 집합에 대해 Component Class을(를) 만들고 싶지 않을 수도 있습니다.

-

Comparator - 설계 동기화 중 어떤 차이를 검사할지 정의합니다. 일반적으로 이 탭의 옵션은 변경할 필요가 없습니다.

-

ECO Generation - 감지된 차이 중 어떤 항목에 대해 ECO(Engineering Change Order)를 생성할지 정의합니다. 일반적으로 이 탭의 옵션은 변경할 필요가 없습니다.

-

Options - 시트 간 연결 생성 방식(Net Identifier Scope), 넷리스트 옵션, 기본 프로젝트 출력 옵션 등을 설정하는 데 사용됩니다. Net Identifier Scope가 Automatic (Based on project contents)로 설정되어 있는지 확인하십시오. 자동 설계 컴파일러가 감지한 넷 식별자(Net Labels, Ports, Sheet Entries, 설계 계층 구조 등)를 기반으로 최적의 설정을 결정합니다.

Linking the Schematic Components to the PCB Components

Altium Designer는 회로도 컴포넌트와 PCB 대응 컴포넌트에 동일한 고유 식별자(UID)를 부여하여 서로 연결합니다. Altium Designer의 회로도 편집기에서 설계를 시작한 뒤 PCB 편집기로 전달하는 경우 UID는 자동으로 할당됩니다. 회로도와 PCB 설계를 Altium Designer로 가져온 경우에는, 이 과정을 사용자가 직접 관리해야 합니다.

각 회로도 컴포넌트를 해당 PCB 컴포넌트에 연결하려면 PCB를 열고 PCB 편집기에서 Project » Component Links 명령을 선택하여 Edit Component Links dialog를 여십시오. 매칭되지 않은 회로도 및 PCB 컴포넌트는 대화상자 왼쪽의 두 열에 나열되며, 이미 일치하는 UID가 할당된 컴포넌트는 대화상자 오른쪽에 나열됩니다. 대화상자 왼쪽 하단에서 적절한 옵션을 활성화한 다음 Add Pairs Matched By 버튼을 클릭하여 Designator, Comment, Footprint 기준으로 컴포넌트를 자동으로 확인하고 매칭합니다.

일치하지 않는 컴포넌트가 있고 그 이유를 알고 있다면(예: 회로도 컴포넌트의 Comment가 PCB 컴포넌트의 Comment와 일치하지 않는 경우) 컴포넌트가 일치하도록 필요한 옵션을 조정하십시오. 또한 각 열에서 매칭되지 않은 회로도 컴포넌트와 매칭되지 않은 PCB 컴포넌트를 선택한 뒤, 대화상자 가운데의 왼쪽→오른쪽 버튼을 클릭하여 수동으로 매칭할 수도 있습니다.

모든 컴포넌트가 매칭되면 Perform Update 버튼을 클릭하십시오. 그러면 Altium Designer가 PCB 컴포넌트 UID를 회로도 컴포넌트 UID와 일치하도록 업데이트합니다.

이 과정 후에도 매칭되지 않은 컴포넌트가 남을 수 있습니다(예: 회로도의 로고, PCB의 마운팅 홀). 이러한 항목은 Component Type 속성을 Graphical 또는 Mechanical 같은 적절한 값으로 설정하여 향후 비교에서 제외할 수 있습니다.

Synchronizing the Schematic to the PCB

회로도 컴포넌트를 PCB의 해당 항목과 매칭한 후에는 전체 설계 비교를 수행할 수 있습니다. 이를 위해 Altium Designer에서 회로도 시트 중 하나를 활성 문서로 만든 다음 Design » Update PCB Document <PcbName> 명령을 선택하십시오. 그러면 Engineering Change Order 대화상자가 열리고, PCB가 회로도와 일치하도록 만들기 위해 PCB에 적용해야 하는 변경 사항 목록이 표시됩니다.

변경 사항은 한 번의 작업으로 모두 적용할 필요가 없습니다. 변경이 많거나 확신이 없는 변경이 있다면 특정 ECO만 활성화하여 프로세스를 관리하는 것이 더 쉬울 수 있습니다. 체크박스 또는 우클릭 컨텍스트 메뉴를 사용해 하나 이상의 변경을 비활성화하십시오.

-

Component Type이 Graphical 또는 Mechanical로 변경되지 않은 매칭되지 않은 PCB 컴포넌트가 있다면, 이를 보드에서 제거하는 ECO가 생성됩니다. 이 ECO를 비활성화한 다음 ECO 프로세스가 완료되면 Component Type을 변경하십시오.

-

넷을 제거하는 ECO가 있다면, 이를 비활성화하고 회로도와 PCB를 비교하여 가져온 설계가 올바른지 확인하는 것을 권장합니다.

Engineering Change Order 대화상자의 버튼을 사용하여 활성화된 변경을 Validate 및 Execute하십시오. 프로세스가 완료되면 Close 버튼을 클릭하여 대화상자를 닫습니다.

► Schematic to PCB Synchronization에 대해 자세히 알아보기.

Working Between the Schematic and the PCB

Altium Designer에는 회로도와 PCB 사이에서 작업하는 데 도움이 되는 도구가 포함되어 있습니다. 예: Navigator panel, Cross Probing, Cross Selection. Navigator 패널은 전체 설계 전반에 걸쳐 컴포넌트, 핀, 넷을 탐색하는 데 사용할 수 있습니다(패널 상단에서 Flattened Hierarchy 선택).

회로도와 PCB에서 동시에 객체로 이동하려면 패널의 항목을 클릭할 때 Alt 키를 누른 채로 클릭하십시오. 두 편집기에서 동시에 탐색하는 경우 작업 공간 뷰를 세로 또는 가로로 분할하거나, PCB를 새 창에서 여는 것이 도움이 됩니다. 문서 탭을 우클릭하여 이러한 명령에 접근할 수 있습니다.

► Working Between the Schematic and the Board에 대해 자세히 알아보기.

Verifying the PCB Design

회로도와 PCB를 동기화한 후 마지막 단계는 PCB가 올바르게 가져와졌는지 검증하는 것입니다.

PCB 편집기의 PCB panel은 보드 설계의 객체를 탐색하는 훌륭한 방법입니다.

보드가 로드되면 설계 규칙과 폴리곤을 검토하고 Design Rule Check를 수행해야 합니다.

Review the Design Rules

Design Rules(Design » Rules)를 검토하되, 특히 Electrical Clearance 규칙과 Plane Connect 및 Clearance 규칙에 주의하십시오. Altium Designer에서 규칙은 객체와 독립적으로 존재합니다. 규칙이 적용되는 객체(타깃)는 규칙의 scope(규칙의 Where the Object Matches 섹션)로 정의됩니다.

Rules Scope(규칙 적용 범위)는 PADS Layout의 Rules Hierarchy를 대체합니다. Scope는 해당 규칙이 지배하는 모든 멤버 객체를 정의하기 위해 작성하는 쿼리라고 볼 수 있으며, 이를 통해 완전한 제어가 가능합니다. 기준 비교를 위해 PADS Layout의 Rules Hierarchy를 살펴보면, 이 규칙들은 미리 정의된 목록 형식에 의존하며 목록에서 숫자가 큰 항목이 더 낮은 항목보다 우선합니다:

-

Default

-

Class

-

Net

-

Group

-

Pin Pair

-

Decal/Component

PADS Layout 규칙 스키마에서 Default 규칙은 레벨 1로 가장 낮고, Decal 및 Component 규칙이 가장 높습니다. 조건부 레이어 규칙(conditional layer rules)을 적용하면 우선순위 레벨을 추가로 부여할 수 있습니다. 예를 들어 조건부 레이어 규칙이 있는 Default는 단순 Default 규칙보다 우선순위 계층에서 더 높습니다.

Altium Designer에서는 scoping을 통해 쿼리로 규칙의 우선순위와 타깃 객체에 적용되는 방식을 정확히 결정할 수 있습니다. 동일한 유형의 규칙을 여러 개 정의하되 각각 다른 객체를 타깃으로 지정할 수도 있습니다. 더 복잡한 쿼리를 직접 작성할 수 있도록 Custom Query 옵션도 제공됩니다.

현재는 설계 규칙을 사용하지 않지만 향후 사용할 가능성이 있다면 삭제하는 대신 비활성화하면 됩니다. 해당 규칙의 관련 목록에서 Enable 옵션을 전환하십시오.

모든 기본 설계 규칙의 scope는 All이며, 이는 보드 전체에 적용됨을 의미합니다. scoping 외에도 사용자가 정의하는 priority 설정이 있습니다. 규칙 scoping과 priority의 조합은 매우 강력하며, 보드의 설계 규칙을 정밀하게 타깃팅할 수 있는 전례 없는 수준의 제어를 제공합니다.

► Design Rules에 대해 자세히 알아보기.

Review the Polygons

Polygon Pour Manager(Tools » Polygon Pours » Polygon Manager)에서 Polygon Pour를 검토하십시오. Polygon Manager는 설계의 모든 폴리곤을 레이어별로 묶어 나열합니다.

Polygon Manager로 다음을 수행할 수 있습니다:

-

포어 순서 변경(큰 폴리곤 안에 작은 폴리곤이 포함된 경우 중요).

-

하나 이상의 폴리곤 리포어(상단 목록은 표준 Windows 다중 선택 방식을 지원).

-

임의 폴리곤의 속성 편집.

Perform a Design Rule Check

설계 규칙을 검사하기 전에 다음을 확인하십시오:

-

Rules are enabled - 설계 규칙은 PCB Rules and Constraints Editor에서 개별적으로 비활성화할 수 있습니다. 이는 개별 규칙 페이지가 아니라 트리의 규칙 유형(rule-type) 레벨에서 수행됩니다.

-

Rule priority is correct - 각 규칙 유형의 규칙 세트는 우선순위 순서대로 나열되며, 필요 시 순서를 변경할 수 있습니다.

-

Display of Violations is configured - 위반 사항은 오버레이로 강조 표시하거나, 상세 표시로 표시하거나, 둘 다 사용할 수 있습니다. 이는 Preferences 대화상자의 DRC Violations Display page에서 구성합니다. 체크박스 목록에서 우클릭하면 컨텍스트 메뉴가 표시되며, 여기서 필요한 Violation Display Style(s)을 빠르게 활성화할 수 있습니다.

-

Rules are enabled for testing - Design Rule Checker 대화상자를 열어 검사할 규칙을 활성화하십시오(우클릭 컨텍스트 메뉴로 사용 규칙을 토글하여 켤 수 있음).

Online DRC는 설계 편집 이벤트 후 자동으로 실행됩니다. Batch DRC는 Design Rule Checker dialog에서 Run Design Rule Check 버튼을 클릭하여 실행합니다.

PCB 편집기에는 PCB Rules and Violations panel이 포함되어 있습니다. 이 패널은 규칙을 검토하고 규칙 위반을 탐색하는 훌륭한 방법을 제공합니다. 규칙 위반을 한 번 클릭하면(패널 상단의 구성 옵션 기준) 해당 위반 위치로 이동하며, 더블클릭하면 Violation Details 대화상자가 열려 해당 위반에 대한 더 자세한 정보를 확인할 수 있습니다.

PCB Editor Tips

PCB 편집기에서 작업할 때 유용한 팁:

-

Ctrl+WheelRoll - 확대/축소

-

WheelRoll - 위/아래로 패닝

-

Shift+WheelRoll - 좌/우로 패닝

-

Ctrl+Shift+WheelRoll - 보드의 레이어를 순차적으로 이동

-

Right Mouse click and drag - 표시 창에서 보드를 슬라이드하여 이동

-

Shift+S - 단일 레이어 모드로 순환하려면 Preferences 대화상자의 Board Insight Display page에서 사용 가능한 Single Layer Modes를 구성하십시오.

-

Shift+C - 선택 및 표시 필터 지우기

-

2 또는 3 - 2D와 3D 표시 모드 전환.

Acknowledgments

PADS™는 Siemens Industry Software Inc.의 등록 상표입니다.

See Also

아래는 PADS 설계를 가져오는 것과 관련된 다른 문서 및 비디오에 대한 참조입니다. 또한 커서가 메뉴 항목, 패널 또는 객체 위에 있을 때 F1를 누르면 추가 정보를 확인할 수 있습니다.