좋은 보드 설계의 핵심 요소 중 하나는 부품 배치입니다. 대규모 설계에서는 보드에서의 부품 위치가 해당 설계자(Designator)와 아무 관련이 없을 수 있습니다. 예를 들어, R1가 R2의 보드 반대편에 배치될 수도 있습니다. 보드에서 부품을 더 쉽게 찾을 수 있도록, 위치 기준으로 설계자를 재할당(보드 재-어노테이션)할 수 있습니다.

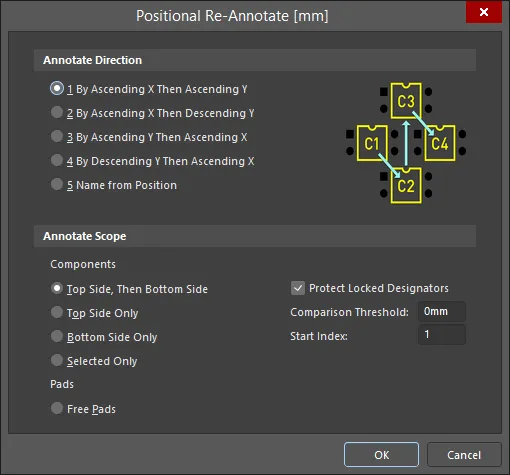

PCB Editor에서 대상 부품 또는 자유 패드(free pad)의 설계자를 위치에 따라 체계적으로 할당하려면, Tools » Re-Annotate을(를) 클릭하여 아래와 같이 Positional Re-Annotate 대화상자를 여십시오. 이 대화상자에서 어노테이션 범위(부품(추가로 면(side) 또는 선택(selection)으로 타깃팅), 또는 자유 패드), 어노테이션 방향(객체 위치 기반), 시작 인덱스 같은 추가 옵션, 그리고 잠긴 설계자를 보호할지 여부를 설정할 수 있습니다.

어노테이션 스타일을 선택하면, 어노테이션이 어떤 방식으로 진행되는지 시각적으로 보여주는 그래픽 묘사가 대화상자 안에 표시됩니다.

Positional Re-Annotate 대화상자에는 각 방법의 그래픽 표현이 포함되어 있습니다.

Options and Controls of the Positional Re-Annotate Dialog

부품 위치 식별

각 부품은 문자열(strings)을 제외한 바운딩 사각형(bounding rectangle)으로 식별됩니다. 부품은 목록으로 정렬되며, 그 순서대로 목록이 다시 번호가 매겨져 새 부품 설계자가 생성됩니다. X 방향에서 두 부품을 비교할 때는 바운딩 사각형의 왼쪽 변을 사용합니다. Y 방향에서 두 부품을 비교할 때는 번호 매김 방향에 따라 사용하는 변이 달라집니다. ascending-Y는 아래쪽 변을, descending-Y는 위쪽 변을 사용합니다.

Comparison Threshold 옵션은 두 변을 비교하여 동일한지 판단할 때 버퍼 값으로 사용할 수 있습니다. 예를 들어 두 왼쪽 변이 서로 75.0 mil 이내에 있고 비교 임계값이 100.0mil로 설정되어 있다면, 이 두 부품은 동일한 X 위치(왼쪽 변)에 있는 것으로 간주됩니다. 이를 통해 약간 정렬이 어긋난 부품도 아래 이미지처럼 논리적인 순서로 재번호를 매길 수 있습니다. 여기서는 R27가 인접한 저항들과 올바르게 어노테이션되도록 다른 저항들보다 더 아래에 배치되어 있습니다( Comparison Threshold 는 10mils로 설정됨).

위치 기준으로 재-어노테이션된 저항들의 연속. R27이 다른 저항들보다 아래에 있음에도 어노테이션 순서에 그대로 포함되어 있음을 확인할 수 있습니다.

위치 기준으로 재-어노테이션된 저항들의 연속. R27이 다른 저항들보다 아래에 있음에도 어노테이션 순서에 그대로 포함되어 있음을 확인할 수 있습니다.

Annotate Scope 옵션은 양면에 부품이 실장된 보드에서 어노테이션 프로세스를 제어하는 기능도 제공합니다. 보드의 Bottom Side에서는 보드를 뒤집어 바라보는 것처럼 부품이 재-어노테이션됩니다. 따라서 뒷면에서 X 방향 비교를 할 때 소프트웨어는 실제로 바운딩 사각형의 오른쪽 변을 사용하며, 뒷면에서 보면 이 변이 왼쪽처럼 보인다는 점을 반영합니다.

Selected Only 옵션이 활성화되어 있고, 재-어노테이션 결과 선택 집합(selection set) 내의 부품이 기존의 비선택 부품과 중복되는 설계자를 부여받게 되는 경우, 비선택 부품의 설계자에는 모든 설계자가 고유하게 유지되도록 _1가 추가로 붙습니다.

또한 회전된 부품은 아래 이미지에 보이는 것처럼, 회전된 새 방향에서 원래 바운딩 사각형을 포함하는 가장 작은 바운딩 사각형으로 식별된다는 점에 유의하십시오.

왼쪽 이미지는 R2의 바운딩 사각형을, 오른쪽 이미지는 R2가 회전했을 때의 새 바운딩 사각형을 보여줍니다.

왼쪽 이미지는 R2의 바운딩 사각형을, 오른쪽 이미지는 R2가 회전했을 때의 새 바운딩 사각형을 보여줍니다.

변경 사항을 회로도에 반영

PCB에서 Re-Annotate를 수행한 후에는 Design » Update 명령을 사용하여 이 변경 사항을 회로도(Schematic)로 다시 전달합니다. 명령을 실행하면 소프트웨어는 먼저 각 회로도 부품을 해당 부품의 고유 ID를 사용해 동등한 PCB 부품과 매칭한 다음, 각 회로도 설계자를 새 PCB 설계자로 업데이트합니다. 어노테이션 프로세스 마무리에 대해 더 알아보십시오.

Design » Update 명령을 실행하여 어노테이션 변경을 회로도로 푸시한 뒤 회로도로 전환하면, 각 새 설계자가 부품 옆에 표시되고, 해당 부품이 이전에 갖고 있던 설계자는 괄호 안의 희미한 위첨자 형태로 함께 표시됩니다. 이는 설계 컴파일러가 이전 값을 유지하기 때문에 발생합니다. Project » Validate PCB Project <ProjectName> 명령을 실행하여 컴파일러가 강제로 업데이트되도록 하면 이전 값이 제거됩니다(show image).

Was-Is 파일 생성

위치 기반 재-어노테이션을 수행할 때마다, 이전 설계자에서 새 설계자로의 매핑도 ASCII 텍스트 파일에 기록됩니다( DesignName[Date][Time].WAS, Projects 패널의 Generated\Text Documents 하위 폴더 아래). 이 파일들은 PCB 문서와 동일한 폴더에 저장됩니다.

컴퓨터 기반 회로도 및 PCB 설계 도구가 처음 개발되었을 때, Was-Is 파일은 PCB의 위치 기반 재-어노테이션을 회로도로 다시 전달하기 위해 개발된 방식이었습니다. 초기 설계자 값과 재-어노테이션된 설계자 값의 목록으로 이루어진 이 파일은, PCB와 회로도 파일이 서로 다른 위치에 있을 때에도 Annotate 대화상자의 Back Annotate 기능을 사용해 변경 사항을 회로도에 로드하는 데 여전히 사용할 수 있습니다. Was-Is 파일을 사용하여 백 어노테이션을 수행하는 방법에 대해 더 알아보십시오.

설계자가 재할당되지 않도록 방지

부품의 설계자가 재할당되지 않도록 하려면, Positional Re-Annotate 대화상자에서 Protect Locked Designators 체크박스를 활성화하고, 아래와 같이 보호할 설계자에 대해 Properties 패널에서 Locked 아이콘이 활성화되어 있는지 확인하십시오.