과제

디바이스의 스위칭 속도가 계속 빨라지면서 신호 무결성을 유지하고 신호의 타이밍 요구사항을 충족하는 것이 과제가 됩니다. 신호 무결성은 controlled impedance routing을 통해 관리할 수 있으며, 이는 PCB 스택업과 각 레이어에서 사용할 라우팅 폭을 신중하게 설계함으로써 달성됩니다.

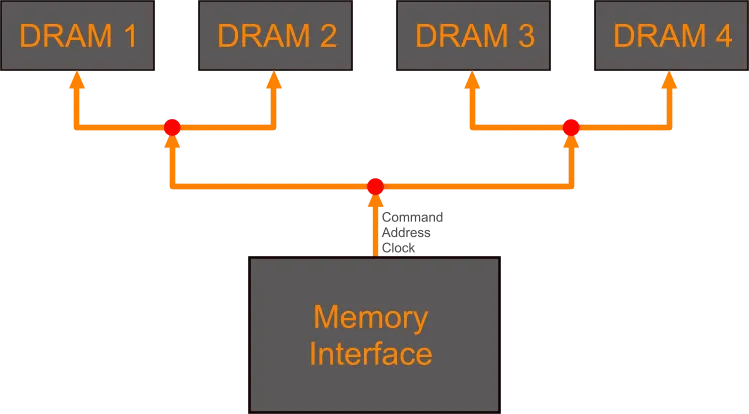

타이밍 요구사항은 신호 경로의 라우팅 길이를 매칭함으로써 충족됩니다. 출력 핀에서 단일 입력 핀으로 연결되는 2핀 신호 경로 집합의 경우, 길이를 계산하고 비교하는 것은 간단합니다. 하지만 일반적인 설계 솔루션에서는 신호 경로에 직렬 종단(termination) 부품이 들어가거나, 신호에 두 개를 초과하는 핀이 포함되어 아래 이미지와 같이 Balanced T 또는 Fly-By 라우팅 토폴로지로 배선될 수 있으므로 상황이 달라집니다.

Balanced T 토폴로지로 라우팅된 4개의 DDR2 RAM 칩. ##

해결책

설계자의 역할은 타이밍 버짓을 만족하기 위해 허용되는 최대 라우팅 길이 같은 설계 요구사항을, 타이밍을 보장하기 위한 Length 규칙과 잠재적인 타이밍 불일치를 감지하기 위한 Matched Length 규칙 같은 설계 규칙 세트로 변환하는 것입니다.

이제 설계자는 신호를 기능 관점에서 바라봅니다(예: “이 주소 신호는 이 커넥터에서 각 메모리 디바이스로 라우팅되어야 한다. 이를 위해 끝단에 종단 저항이 있는 fly-by 토폴로지로 라우팅할 것이다. 소스에 직렬 종단도 필요할 수 있다”). 주소 A0가 종단 저항을 통과하더라도, 설계자에게 그 신호는 저항 반대편에서도 여전히 A0입니다.

하지만 PCB 편집기는 각 신호를 단순히 연결된 핀들의 집합(일반적으로 net이라고 함)으로만 봅니다 — Net A0는 이 커넥터 핀에서 이 메모리 컴포넌트 핀으로, 그다음 이 메모리 컴포넌트 핀으로… 이런 식입니다. 직렬 종단 저항이 추가되는 순간, 그 주소 라인은 두 개의 분리된 net이 됩니다. 이로 인해 설계자가 Length 및 Matched Length 설계 규칙 같은 핵심 설계 요구사항을 지정하기가 어려워집니다.

이는 xSignals (or extended Signal)라는 기능으로 관리할 수 있습니다. 이 기능은 고속 신호 경로를, 종단 부품과 분기(branch)를 포함하더라도 소스와 목적지 사이를 신호가 이동하는 “경로”로 올바르게 취급할 수 있게 해줍니다.

xSignal은 본질적으로 두 노드 사이의 설계자 정의 신호 경로입니다. 이는 동일한 net 내의 두 노드일 수도 있고, 부품에 의해 분리된 연관 net들에 속한 두 노드일 수도 있습니다. 그런 다음 xSignal을 사용해 Length 및 Matched Length 같은 관련 설계 규칙의 범위를 지정할 수 있으며, 이러한 규칙은 인터랙티브 길이 튜닝 같은 설계 작업 중에 준수됩니다.

새 xSignal 생성

xSignal은 두 노드 사이의 설계자 정의 신호 경로이며, 동일한 net 내의 두 노드일 수도 있고 서로 다른 net에 있는 두 노드일 수도 있습니다.

xSignal은 다음 방법으로 정의합니다:

- xSignals Multi-Chip Wizard를 사용합니다. 이 방법이 xSignal을 생성하는 가장 일반적인 접근 방식이며 아래에 설명되어 있습니다.

또는, 먼저 관심 객체를 선택한 다음 적절한 명령을 선택하여 다음 방법을 사용할 수 있습니다:

-

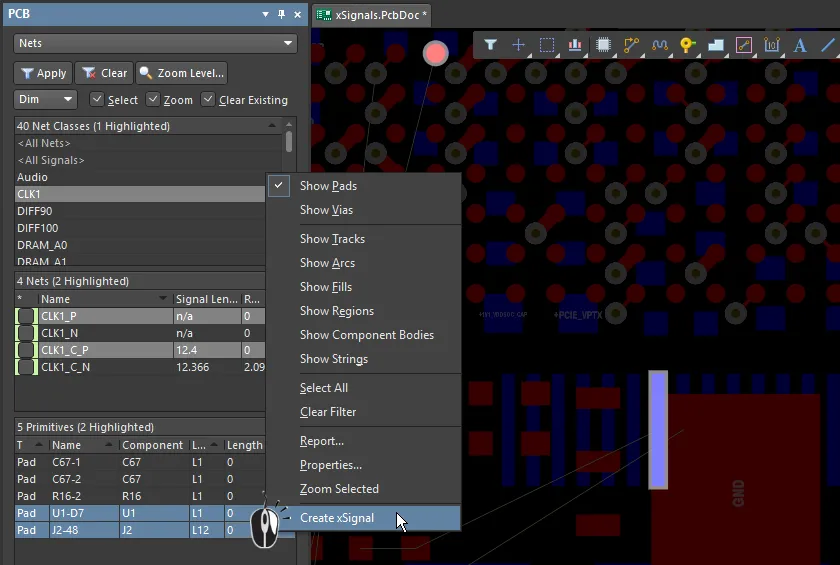

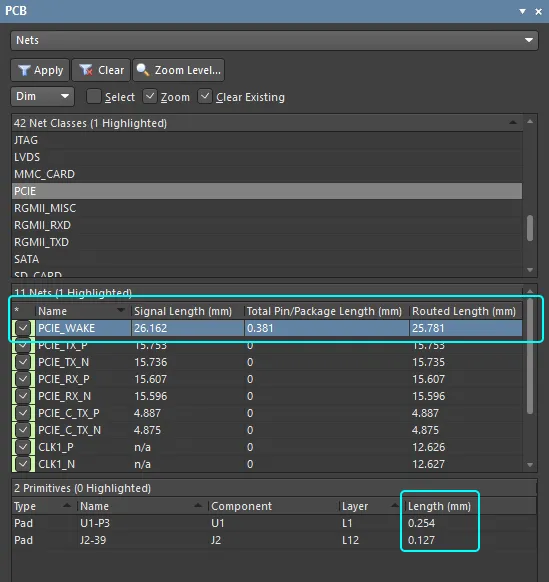

선택한 패드를 기반으로 단일 xSignal 생성. 필요한 시작 패드와 끝 패드를 선택합니다(직렬 종단 부품이 있는 경우 이 패드들은 서로 다른 net에 있을 수 있음). 패드는 설계 공간에서 직접 선택할 수도 있고, PCB 패널을 Nets 모드로 사용하여 패드를 찾아 선택할 수도 있습니다(아래 이미지 참조). 패드를 선택한 후, 설계 공간에서 선택된 패드 중 하나를 우클릭한 다음 xSignals » Create xSignal from Selected Pins 명령을 실행하거나, PCB 패널에서 선택된 패드 중 하나를 우클릭하고 Create xSignal 명령을 실행합니다. 새 xSignal은 xSignals mode of the PCB panel에 목록으로 표시됩니다.

선택한 핀(풋프린트 패드)을 기반으로 xSignal을 정의할 때는 Create 명령을 실행하기 전에 시작 패드와 끝 패드만 선택하십시오.

새 xSignal의 이름은 두 net 이름을 하이픈으로 연결한 조합이 됩니다. xSignal 이름은 PCB 패널의 xSignals 모드에서 편집할 수 있습니다.

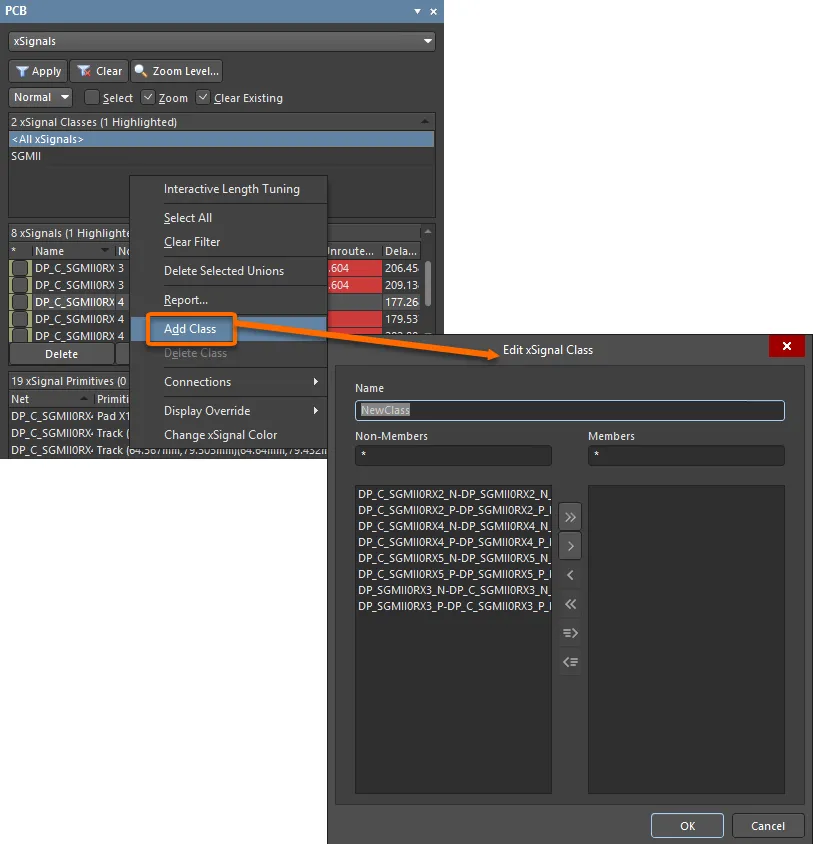

새 xSignal은 xSignal 클래스에 추가할 수 있으며, 패널의 xSignal Classes 영역에서 우클릭하여 새 클래스를 만들고 멤버를 추가할 수 있습니다.

- 소스 컴포넌트를 선택한 다음, 선택된 컴포넌트를 우클릭하고 컨텍스트 메뉴에서 xSignal » Create xSignals between Components command를 선택합니다. Create xSignals Between Components 대화상자가 열리며, 선택한 소스 컴포넌트가 선택된 상태로 표시됩니다. 이 대화상자는 아래에 설명되어 있습니다.

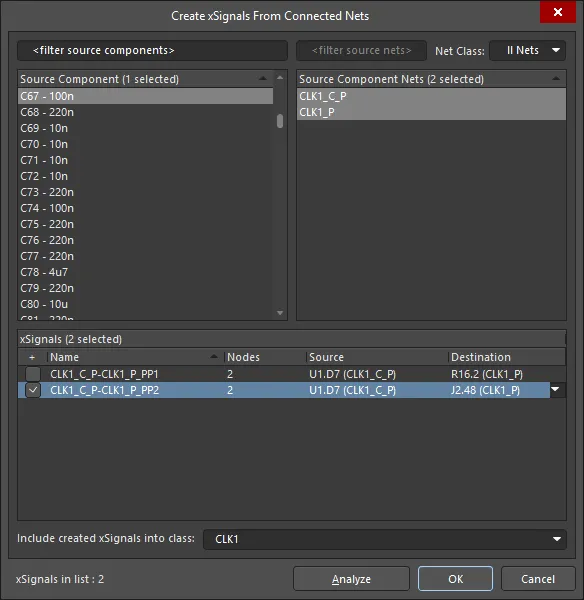

- 설계 공간에서 하나 이상의 직렬 컴포넌트를 선택한 다음, 선택된 컴포넌트 중 하나를 우클릭하고 컨텍스트 메뉴에서 xSignal » Create xSignals from Connected Nets command를 선택합니다. Create xSignals From Connected Nets 대화상자가 열립니다. 선택된 소스 컴포넌트와 그 컴포넌트에 연결된 net들이 선택됩니다. 이 대화상자는 아래에 설명되어 있습니다.

- 기존 xSignal 내부에 xSignal을 생성하고 싶은 경우도 있는데, 이때는 PCB 패널의 xSignal 모드를 사용할 수 있습니다. 패널 상단에서 Select 옵션이 활성화되어 있는지 확인하고, 현재 xSignal을 찾은 다음 패널의 xSignal Primitives 섹션에서 필요한 패드를 선택합니다. 그런 다음 설계 공간에서 선택된 패드 중 하나를 우클릭하고, 이 목록의 2단계에 설명된 방법을 사용해 과정을 완료합니다.

패널의 Nets 모드에서 두 패드를 선택하고, 선택된 패드 중 하나를 우클릭한 다음 Create xSignal를 선택합니다. 패드가 서로 다른 net에 있다는 점에 유의하십시오.

시작 패드와 끝 패드가 동일한 net에 있으면 xSignal은 <NetName>_PPn 형식의 이름을 가지며, 여기서 n 는 해당 net에 대해 정의된 여러 xSignal을 구분하기 위해 사용되는 다음 사용 가능 정수입니다. 시작 패드와 끝 패드가 서로 다른 net에 있으면 xSignal은 <StartNet>_<EndNet>_PPn 형식의 이름을 가지며, 여기서 n 는 해당 net 조합에 대해 정의된 여러 xSignal을 구분하기 위해 사용되는 다음 사용 가능 정수입니다.

xSignals Multi-Chip Wizard

xSignals Multi-Chip Wizard는 단일 소스 컴포넌트와 여러 타깃 컴포넌트 사이에 xSignal을 생성하는 데 사용됩니다. Wizard 는 잠재적 xSignal을 식별하기 위해 컴포넌트 중심 접근 방식을 사용합니다. 즉, 단일 소스 컴포넌트, 관심 net, 타깃 컴포넌트를 선택하면 Wizard 가 소스 컴포넌트에서 대상 컴포넌트까지의 모든 잠재 경로를 분석하며, 이때 직렬 수동 부품을 통과하고 모든 분기를 따라갑니다. 그런 다음 설계자는 생성하고 싶은 xSignal을 선택할 수 있고, 필요하다면 Matched Length 설계 규칙도 생성할 수 있습니다. Wizard 는 또한 다양한 일반 인터페이스 및 메모리 회로에 대해 xSignal과 xSignal 클래스를 자동으로 생성하는 데도 사용할 수 있습니다.

이 Wizard에서 출력 핀은 Source로, 타깃 입력 핀은 Destination로 지칭됩니다.

이 Wizard는 여러 번 실행할 수 있는 도구이기도 합니다. xSignal Routes 페이지에서 처음 생성한 xSignal의 전체 마스터 그룹에서 일부를 선택해 클래스와 규칙을 정의한 다음, 다시 마스터 그룹으로 돌아가 다른 일부를 선택해 클래스와 규칙을 정의하는 식으로 계속 진행할 수 있습니다.

Wizard 의 큰 장점 중 하나는 Wizard 와 PCB 편집기 사이를 쉽게 오가며 작업할 수 있다는 점입니다. Wizard의 어떤 페이지에서든 xSignal을 클릭하면 해당 패드와 모든 라우팅이 PCB에서 시각적으로 하이라이트됩니다.

현재 단계에서 Wizard는 T-접합 식별자(T-junction identifiers)를 자동으로 추가하는 기능을 지원하지 않습니다. 이는 흔히 tie-point 또는 branch-point라고도 합니다. 설계에 분기 라우팅이 포함되어 있다면 다음을 권장합니다:

- 직렬 종단 저항 같은 수동 부품이 있다면, 소스 컴포넌트에서 수동 부품까지의 길이를 튜닝합니다.

- 각 분기에서 T-접합부터 목적지 컴포넌트까지의 길이를 튜닝합니다.

- 필요하다면, 수동 부품에서(수동 부품이 없다면 소스에서) T-접합까지 남은 길이를 튜닝합니다.

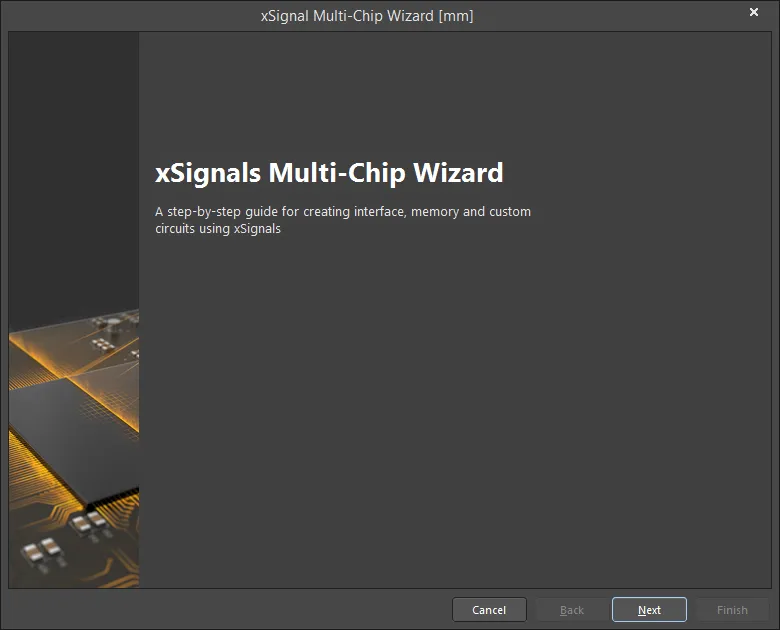

xSignals Multi-Chip Wizard에 접근하려면, 메인 메뉴에서 Design » xSignals » Run xSignals Wizard 명령을 선택하거나 PCB 레이아웃에서 우클릭한 다음 xSignals » Run xSignals Wizard를 선택합니다. Wizard의 시작 페이지가 표시됩니다.

xSignals Multi-Chip Wizard의 시작 페이지xSignals Multi-Chip Wizard

xSignals Multi-Chip Wizard 모드

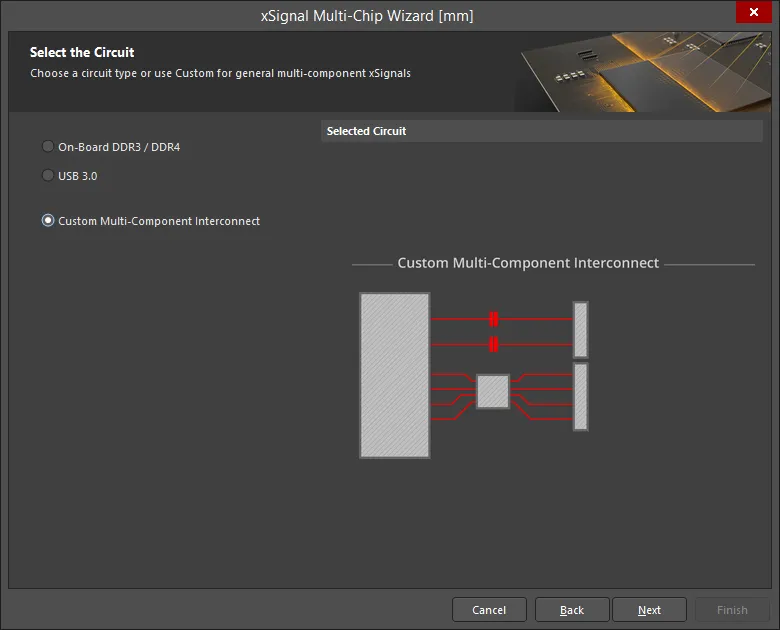

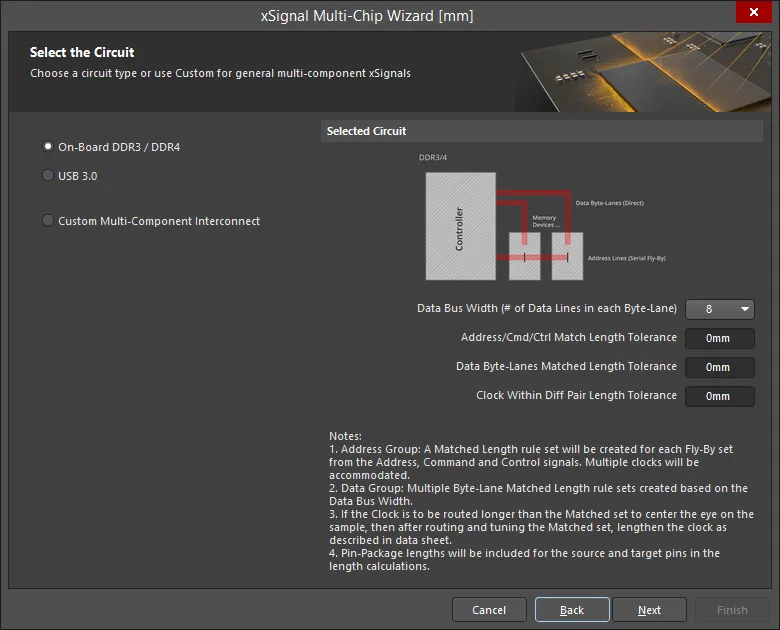

Wizard의 두 번째 페이지에서 Custom Multi-Component Interconnect, On-Board DDR3 / DDR4, 또는 USB 3.0 중 하나를 선택하라는 요청이 표시됩니다. Custom Multi-Component Interconnect 모드는 선택한 소스 컴포넌트와 여러 타깃 컴포넌트 사이에 다수의 xSignal을 정의하는 데 사용되며, On-Board DDR3 / DDR4 모드는 DDR3 또는 DDR4 메모리에 대한 xSignal을 생성하는 데 사용됩니다. USB 3.0 모드는 각 USB 3.0 채널에 대해 xSignal, xSignal 클래스, Matched Length 규칙을 생성합니다. 필요에 맞는 모드를 선택하십시오.

The Custom Multi-Component Interconnect Mode

이 모드에서는 선택한 소스 컴포넌트와 여러 타깃 컴포넌트 사이에 여러 xSignal을 정의하는 데 Wizard를 사용할 수 있습니다. Wizard는 잠재적인 xSignal을 식별하기 위해 컴포넌트 중심 접근 방식을 사용합니다. 즉, 단일 소스 컴포넌트, 관심 있는 넷, 그리고 목적지 컴포넌트를 선택하면, 직렬 수동 소자를 통과하고 모든 분기(브랜치)를 따라 소스 컴포넌트에서 목적지 컴포넌트까지의 모든 가능한 경로를 분석합니다. 그런 다음 설계자는 생성할 xSignal을 선택할 수 있습니다. Wizard는 컴포넌트 간 여러 넷에 대한 엔드-투-엔드(end-to-end) xSignal을 정의하는 것뿐 아니라, 해당 엔드-투-엔드 신호의 구간(소스 출력 핀→직렬 종단 컴포넌트, 직렬 종단 컴포넌트→목적지 입력 핀)에 대해서도 xSignal을 생성할 수 있게 해줍니다. 활성화한 설정에 따라 Wizard는 xSignal 클래스와 해당 xSignal을 대상으로 하는 Matched Net Lengths 설계 규칙도 생성할 수 있습니다. Wizard가 완료되면 길이 튜닝(length tuning) 프로세스를 시작할 수 있습니다.

Wizard는 여러 페이지에 걸쳐 구성됩니다. 페이지 수는 회로 구성에 따라 달라집니다. 예를 들어 직렬 종단 소자가 있으면 추가 페이지가 나타납니다. 각 페이지의 구성은 아래에 설명되어 있습니다.

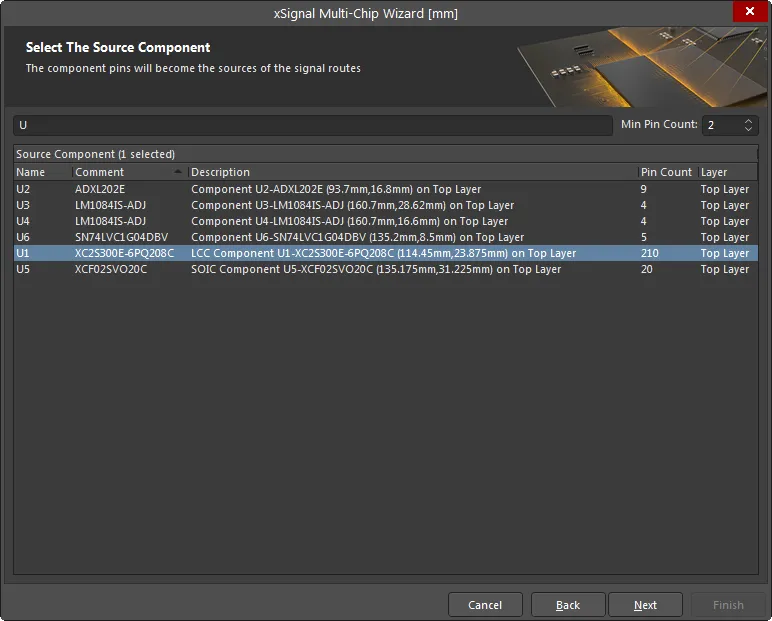

소스 컴포넌트 선택

이 페이지에서 단일 소스 컴포넌트를 선택합니다. 그리드 상단의 Filter 및 Min Pin Count 필드를 사용해 관심 컴포넌트를 찾을 수 있습니다. * 및 ? 와일드카드를 지원합니다.

이 Wizard의 그리드에는 우클릭 바로가기 메뉴가 있으며, 표준 Windows 다중 선택 키도 지원합니다. 또한 좌클릭 또는 Spacebar로 선택된 항목의 체크박스를 토글할 수 있습니다.

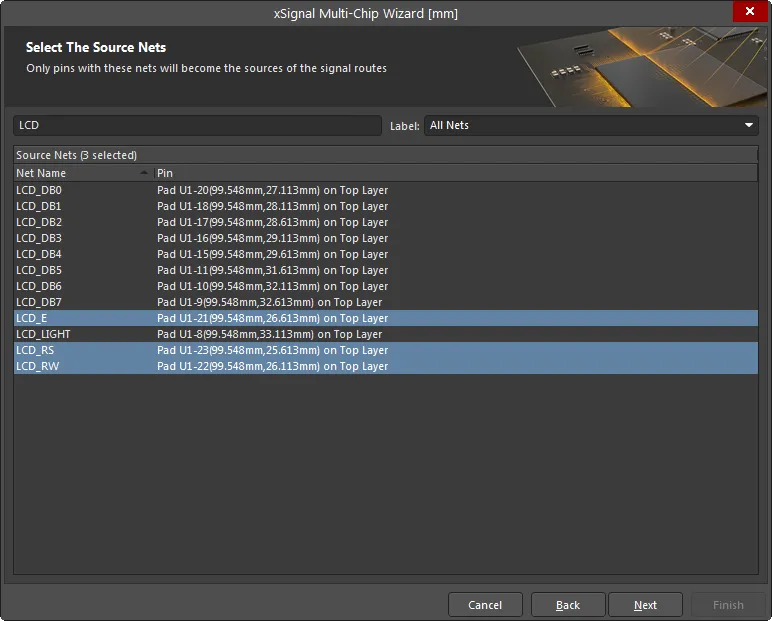

소스 넷 선택

선택한 소스 컴포넌트에 연결된 관심 넷을 선택합니다. 그리드 상단의 Filter 및 Label 필드를 사용해 관심 넷을 찾을 수 있습니다. 나열된 넷을 가진 핀만 신호 라우트의 소스가 됩니다.

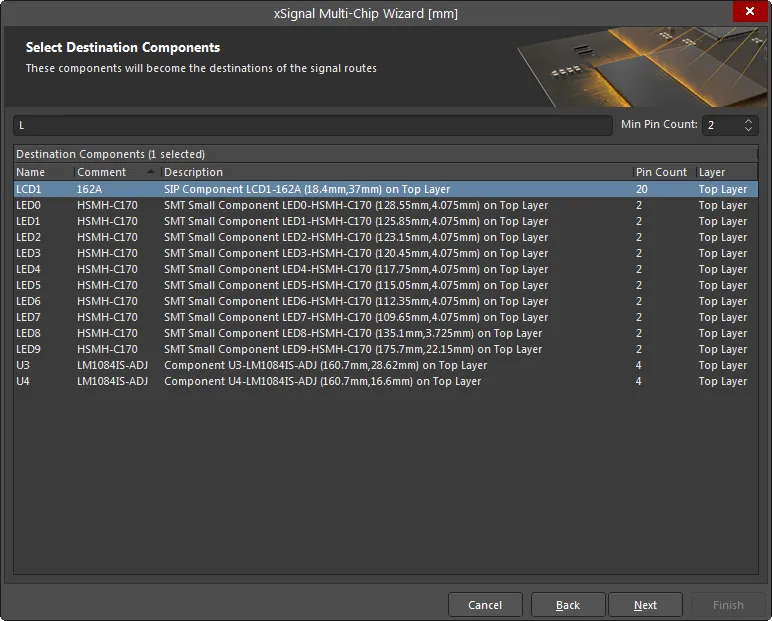

목적지 컴포넌트 선택

원하는 목적지 컴포넌트(들)를 선택합니다. 그리드 상단의 컴포넌트 Filter 및 Min Pin Count 필드를 사용해 관심 컴포넌트를 찾을 수 있습니다.

Next를 클릭하면 Wizard가 선택한 컴포넌트들 사이에서 선택된 넷 집합으로부터 생성 가능한 모든 xSignal을 식별합니다. Wizard가 두 핀이 모두 선택된 넷에 연결된 2핀 컴포넌트를 감지하면, 이를 직렬 종단 컴포넌트로 자동 식별하며 프로세스 후반에 추가 Wizard 페이지가 나타납니다.

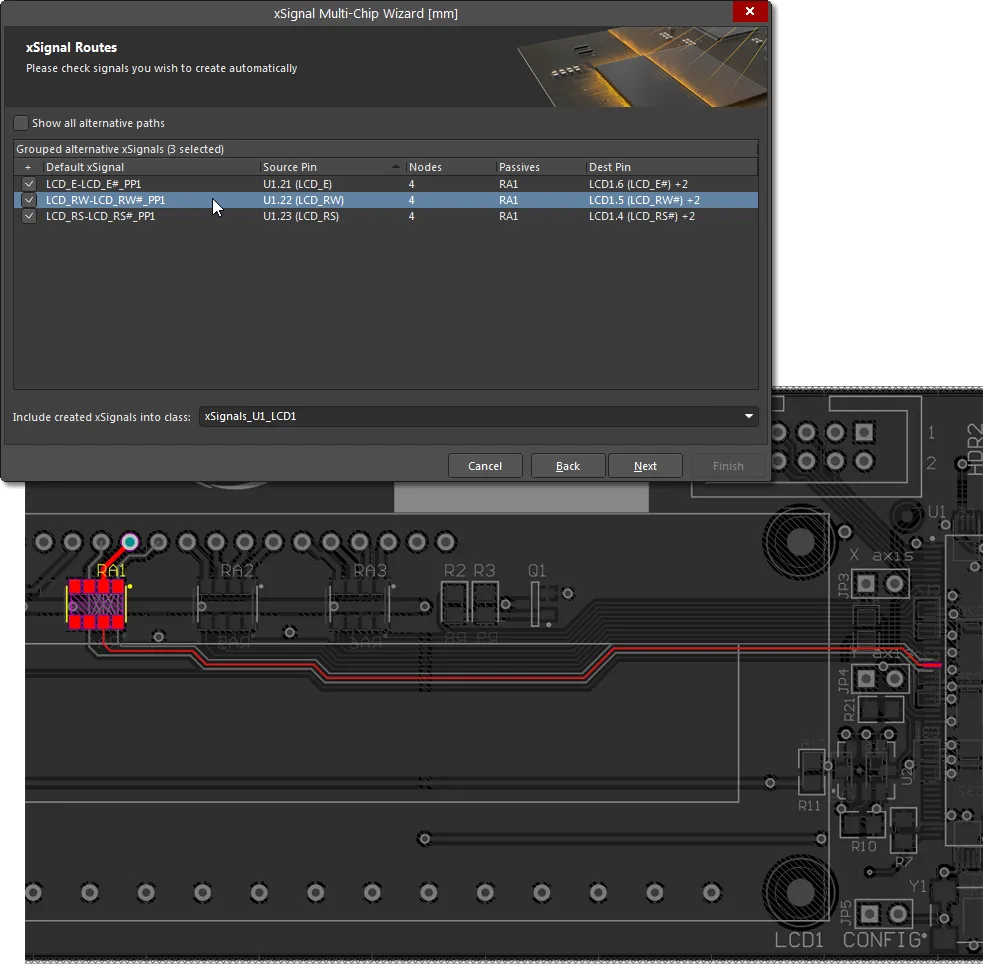

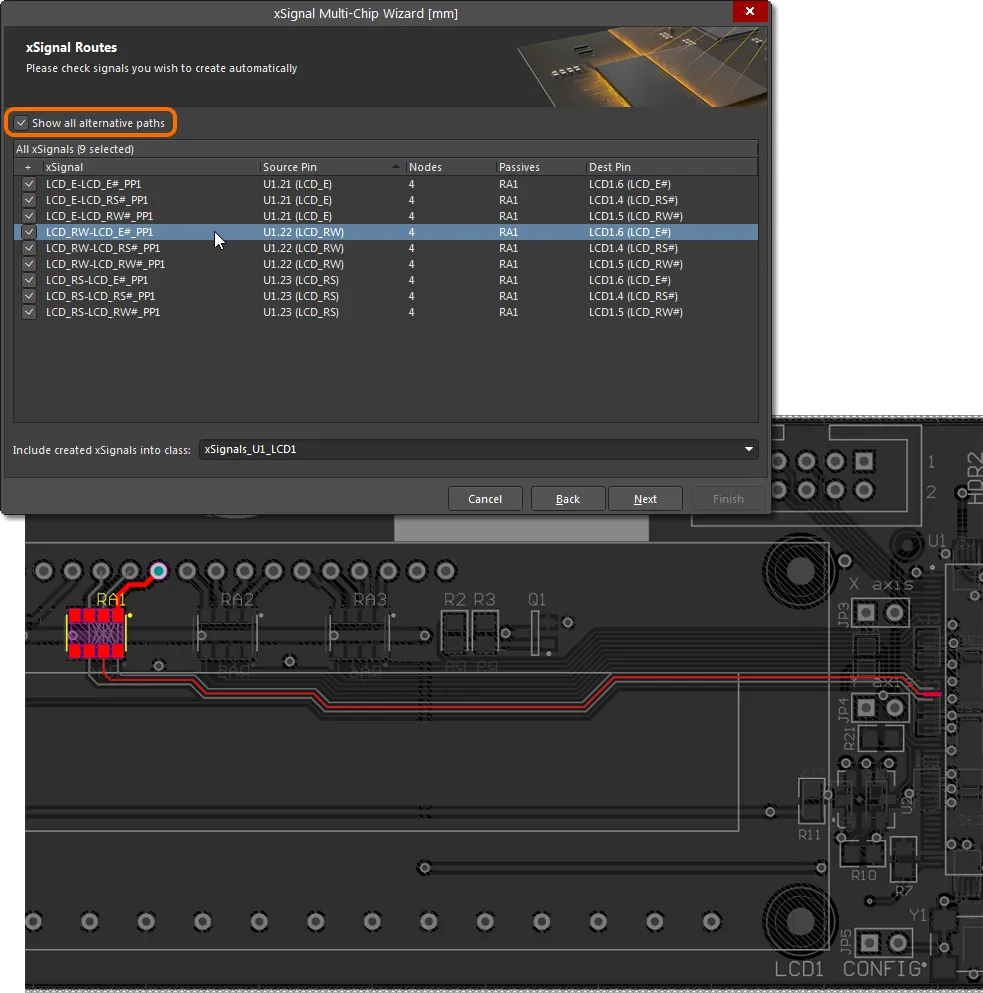

xSignal 라우트

이 Wizard 페이지에는 각 Source Pin에서 각 Destination Pin까지의 제안된 xSignal이 나열됩니다. 항목을 클릭하면 PCB에서 해당 xSignal이 하이라이트됩니다.

넷 경로를 분석해 잠재적 xSignal을 식별한 후, Wizard는 관심 있을 만한 조합만 나열하도록 목록을 줄이려고 시도합니다. 이것들이 엔드-투-엔드 xSignal이며, 위 이미지는 Wizard의 이전 페이지에서 선택한 소스 및 목적지 컴포넌트 사이의 xSignal을 보여줍니다. 또한 이미지에는 Wizard가 각 라우트에서 직렬 종단 컴포넌트 RA1을 감지했음을 보여줍니다. RA1은 실제로 4개 저항이 들어있는 저항 팩인데, 이 경우 Wizard는 각 저항이 팩을 가로질러 연결된다고 가정하여 논리적 연관을 자동으로 생성하고, 컴포넌트에서 서로 마주보는 핀에 연결된 넷을 페어링합니다.

각 저항의 핀이 서로 마주본다는 이 가정이 항상 맞는 것은 아니므로, Dest Pin 열의 드롭다운을 사용해 사용 가능한 다른 출력 넷을 선택할 수 있습니다. 또는 그리드 상단의 Show all alternative paths 옵션을 활성화하여 xSignal 생성에 사용할 수 있는 모든 잠재적 넷 조합을 표시할 수 있습니다. xSignal을 만들고 싶은 각 라인의 체크박스를 활성화하세요. 활성화된 xSignal은 이 페이지 하단의 Include created xSignals into class 필드에 표시된 클래스에 추가됩니다. 새 이름을 입력하거나 드롭다운에서 선택하세요.

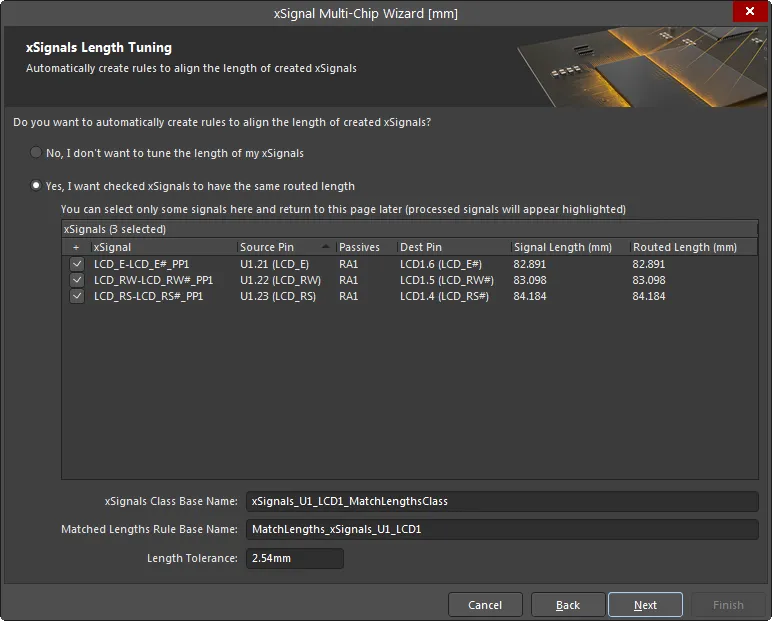

xSignals 길이 튜닝

이 페이지는 활성화된 xSignal에 대해 Matched Length 설계 규칙을 자동으로 생성하는 데 사용됩니다. 이 새 설계 규칙의 대상이 되길 원하는 xSignal을 only 활성화하세요. 설계에 서로 다른 요구사항을 가진 여러 규칙이 필요하다면, 프로세스 후반에 아직 규칙이 정의되지 않은 xSignal에 대해 추가 규칙을 정의할 기회가 제공됩니다. 이 첫 단계에서는 전체 엔드-투-엔드 xSignal도 표시됩니다. 이후 Wizard 페이지에서는 xSignal 내부 구간(예: 출력 핀→직렬 종단 저항 구간)에 대한 설계 규칙을 정의할 수 있습니다.

xSignal 길이를 튜닝하고 싶지 않다면 No, I don't want to tune the length of my xSignals를 활성화하세요. 이 옵션이 활성화되면 이 페이지의 다른 옵션은 사용할 수 없습니다. 다른 옵션을 편집하고 접근하려면 Yes, I want checked xSignals to have the same routed length를 활성화하세요.

xSignals Class Base Name 필드는 현재 선택된 xSignal의 이름을 정의하는 데 사용됩니다. 다른 xSignal에 대해서도 이 과정을 반복할 수 있음을 염두에 두고 의미 있는 이름을 입력하세요. 그러면 이 xSignal 세트는 Matched Lengths Rule Base Name 필드에 입력한 이름의 설계 규칙과 지정된 Length Tolerance에 의해 타깃팅됩니다.

어떤 객체가 타깃팅되는지 확실하지 않나요? 하나 이상의 항목을 클릭해 PCB 레이아웃에서 신호 경로를 하이라이트하세요.

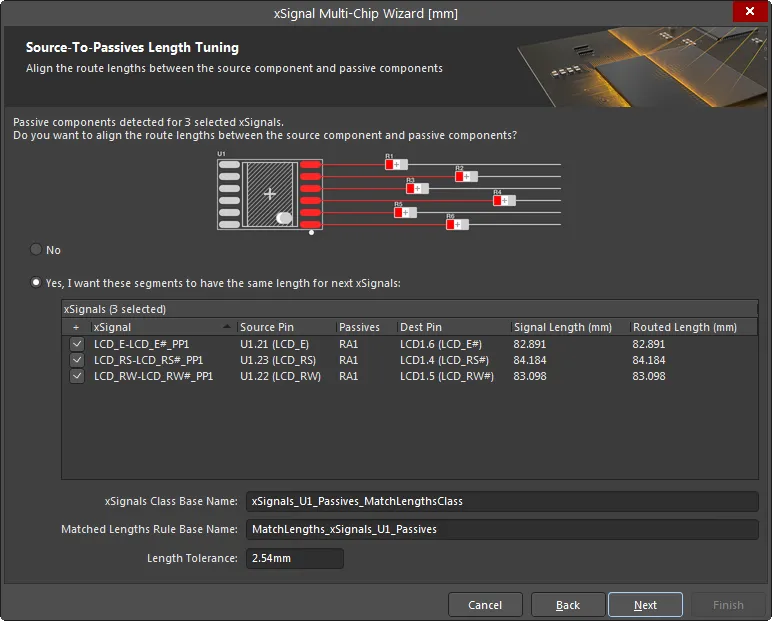

소스-수동소자 길이 튜닝

선택한 넷 집합에 직렬 종단 컴포넌트가 포함되어 있으면, 넷의 이러한 구간에 대해 추가 xSignal과 설계 규칙을 만들 수 있는 추가 Wizard 페이지가 나타납니다. 위 이미지에서는 Wizard의 이 페이지가 소스 핀에서 종단 컴포넌트까지 이어지는 선택된 xSignal에 대해 Matched Length 설계 규칙을 생성하는 데 사용되고 있음을 볼 수 있습니다. 이에 대한 xSignal / xSignal 클래스 / 설계 규칙이 필요하다면 Yes, I want these segments to have the same length for next xSignals 옵션을 활성화하고, 필요한 xSignal을 활성화한 다음 xSignals Class Base Name, Matched Lengths Rule Base Name, Length Tolerance을 정의하세요. 이 Matched Length 규칙에 사용할 추가 xSignal이 생성됩니다.

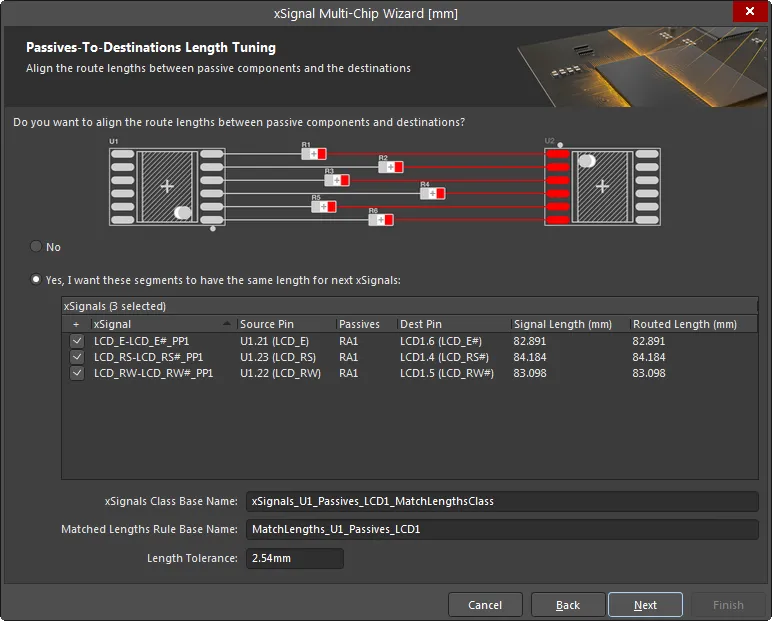

수동소자-목적지 길이 튜닝

이 페이지는 종단 컴포넌트에서 목적지 핀까지 이어지는 선택된 xSignal에 대해 Matched Length 설계 규칙을 생성하는 데 사용됩니다. 필요하다면 Yes, I want these segments to have the same length for next xSignals 옵션을 활성화하고, 필요한 xSignal을 활성화한 다음 xSignals Class Base Name, Matched Lengths Rule Base Name, Length Tolerance을 정의하세요. 이 Matched Length 규칙에 사용할 추가 xSignal이 생성됩니다.

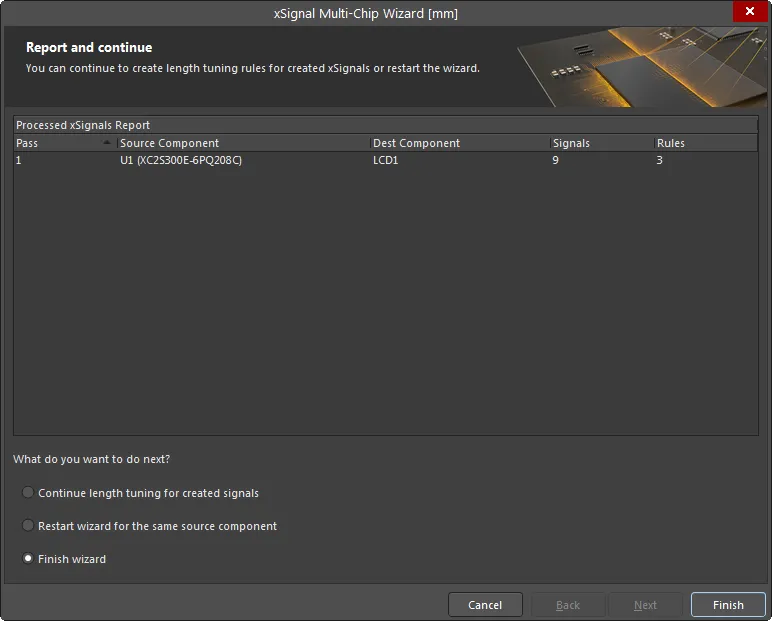

보고 및 계속

이 Wizard 페이지에는 생성될 xSignal 수와 생성될 설계 규칙 수가 자세히 표시됩니다.

페이지 하단에서 다음을 선택할 수 있습니다:

- Continue length tuning for created signals – 이전 페이지에서 특정 xSignal을 비활성화했고 이제 해당 xSignal에 대한 추가 규칙 정의 프로세스를 진행해야 하는 경우 선택합니다.

- Restart wizard for the same source component – 이 설정을 폐기하고 동일한 컴포넌트/넷 선택 상태로 Wizard를 다시 시작하려는 경우 선택합니다.

- Finish wizard – 이 소스 컴포넌트에 대한 xSignal 및 설계 규칙 생성이 완료된 경우 선택합니다.

xSignal은 PCB 패널의 xSignal 모드에서 확인할 수 있습니다. 패널에서 Delete 키를 눌러 선택된 xSignal 클래스 또는 선택된 xSignal을 제거합니다.

이 xSignal은 길이 튜닝을 할 준비가 되었습니다. 시작하려면 메인 Route 메뉴 또는 Active Bar에서 Interactive Length Tuning 옵션( )을 선택하세요.

)을 선택하세요.

길이 튜닝 아코디언(accordion)은 쉽게 제거할 수 있습니다. 아코디언의 어떤 세그먼트든 한 번 클릭해 선택한 다음 Delete를 누르세요.

아코디언을 배치하면 기존 트랙 세그먼트가 시작점과 끝점에서 분할됩니다. 따라서 이 튜닝-삭제 과정을 몇 번 반복하면, 직선 라우팅 구간이 실제로는 많은 짧은 트랙 세그먼트로 구성되는 상황이 발생할 수 있습니다. 여러 개의 작은 트랙 세그먼트를 다시 단일 세그먼트로 합치려면 메인 메뉴에서 Design » Netlist » Clean All Nets 명령을 실행하세요.

On-Board DDR3 / DDR4

이 모드에서는 Wizard가 온보드 DDR3/DDR4에 대해 xSignal, xSignal 클래스, Matched Length 그룹, Diff Pair Matched Lengths 규칙, 그리고 Fly-By 토폴로지를 자동으로 생성합니다. Wizard는 fly-by 라우팅 토폴로지가 사용될 것이라고 가정합니다.

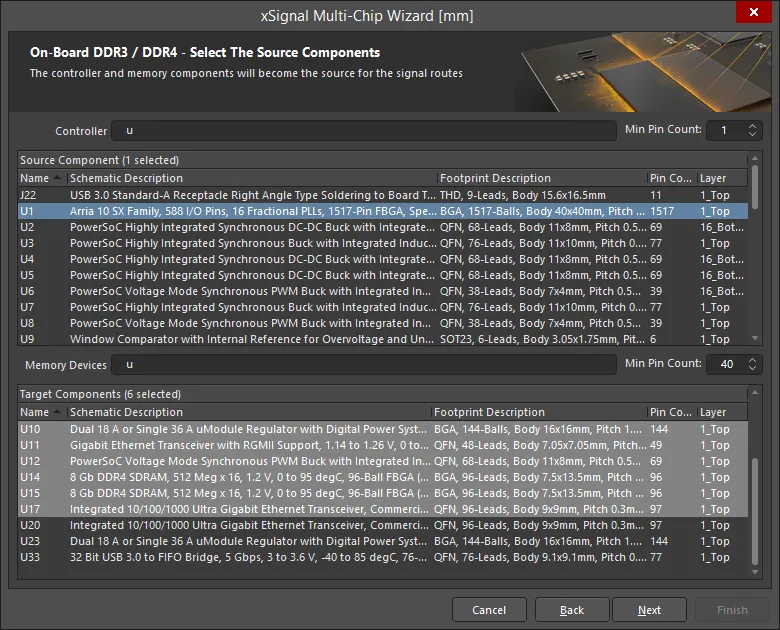

소스 컴포넌트 선택

이 페이지에서 Wizard 는 설계자 접두어(prefix)와 핀 수를 기반으로 모든 잠재적 소스 컴포넌트와 타깃 컴포넌트를 식별합니다. Controller/Memory Devices 필드를 사용해 컴포넌트/메모리 디바이스를 필터링하고, 위/아래 화살표로 Min Pin Count를 필요에 맞게 설정하세요( Source Component 및 Target Components 모두에 대해). 그런 다음 단일 소스 컴포넌트를 선택하고 타깃 컴포넌트(들)를 선택합니다.

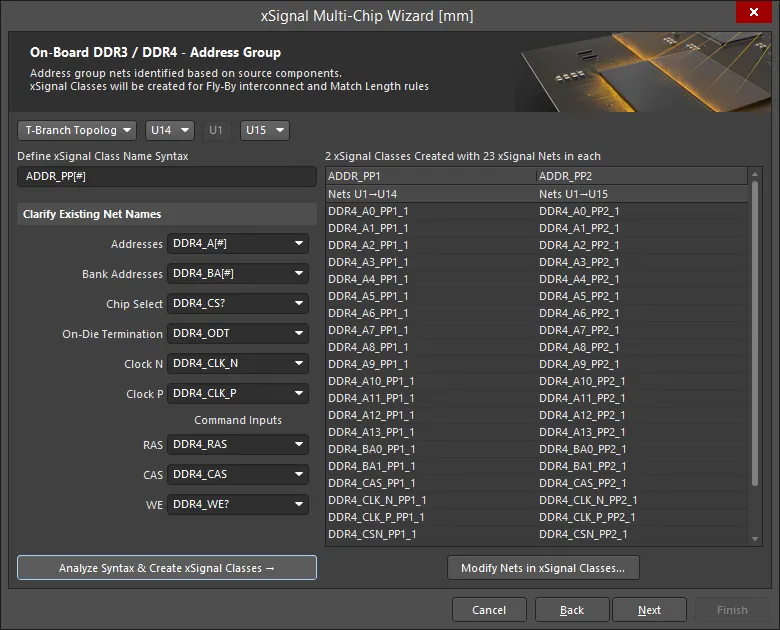

주소 그룹

이 페이지의 기능은 다음과 같습니다:

- Fly-By TopologyT-Branch Topology 및 T-Branch Topology 옵션이 지원됩니다. 드롭다운 목록에서 필요한 토폴로지를 선택하세요.

- Fly-By Topology를 선택하면 타깃 디바이스가 fly-by 라우팅의 포인트-투-포인트 순서로 나열됩니다. 소프트웨어가 순서를 자동으로 결정하려고 시도합니다. Wizard를 컴포넌트 배치 전에 실행한 경우에는 드롭다운 컨트롤을 사용해 포인트-투-포인트 순서를 수동으로 설정해야 합니다.

- T-Branch Topology를 선택하면(위에 표시된 것처럼) 타깃 디바이스의 절반은 소스 앞에, 나머지 절반은 소스 뒤에 표시됩니다. 드롭다운 컨트롤을 사용해 필요에 따라 타깃 컴포넌트의 순서를 지정하세요.

- Define xSignal Class Name Syntax:

- 시작 기본값은

ADDR_PP[#]

- 입니다.

[#]는 메모리 디바이스의 개수를 나타냅니다.

PP 접미사는 필요하면 변경할 수 있습니다.

- Wizard는 컴포넌트를 분석하여 설계에서 이러한 접미사를 찾고, 아래에 설명된 접근 방식을 사용해 전체 이름 구문을 표시합니다. 올바르지 않다면 이를 업데이트하세요.

- 여기서의 목표는 이러한 기능에 해당하는 넷을 자동으로 찾는 것입니다. 넷을 찾으면 해당 명명 구문을 필드에 입력합니다.

- 그런 다음 구성요소 사이의 넷을 검토하며, 접미사가 발견되면 접두사를 식별합니다. 예를 들어 Wizard는 주소 라인을 찾기 위해

_A[#]를 찾습니다.

- “_”로 시작하는 접미사를 가진 넷이 발견되지 않으면, “_” 뒤의 텍스트만을 대상으로 다시 검색합니다. 또한 “-” 또는 “.” 같은 대체 구분자도 확인합니다.

- 구문을 자동으로 결정할 수 없으면, 사용자가 이 필드를 정의해야 합니다. 드롭다운을 사용해 보드에 존재하는 넷 중에서 선택하십시오.

- 순서와 명명 구문을 정의한 후 Analyze Syntax & Create xSignal Classes 버튼을 클릭하여 xSignal 목록을 생성합니다. Wizard는 구문과 구성요소 연결 방식을 확인하여, 대화상자 오른쪽 그리드에 표시되는 xSignal Class를 구성합니다. Classes Created의 개수는 메모리 디바이스 개수와 일치합니다.

- 생성된 클래스 수(예: 4)와 각 클래스에 포함된 xSignal 넷 수(예: 26).

- xSignal은 각 xSignal class별로 하나의 열에 그룹화됩니다. 각 클래스마다 Matched Lengths 설계 규칙이 생성됩니다. 표의 하위 제목은 이러한 xSignal의 소스 및 타깃 구성요소를 나타냅니다.

- 자동 생성된 목록이 불완전하거나 올바르지 않으면 Modify Nets in xSignal Classes 버튼을 클릭하여 Edit xSignal Class 대화상자를 열고, 클래스에 넷을 수동으로 추가하거나 삭제하십시오. 단, 이후 Analyze Syntax & Create xSignal Classes 버튼을 다시 클릭하면 수동 변경 사항은 사라집니다.

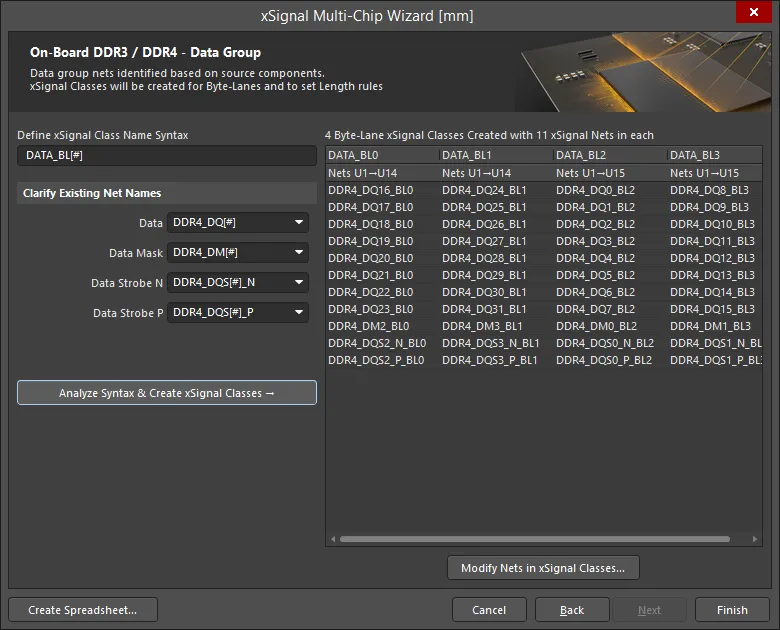

데이터 그룹 넷 식별

마지막 단계는 Data Group에 속하는 모든 넷을 식별하는 것입니다.

이 페이지의 기능은 다음과 같습니다.

- 사용자 정의 xSignal Class 이름 구문:

- 시작 기본값은

DATA_BL[#]

- 입니다.

[#]는 Byte-Lane 수를 의미하며, 이는 전체 데이터 라인 수를 앞서 정의한 Data Bus Width로 나눈 값으로 결정됩니다.

- 필요한 경우

BL 접미사를 변경할 수 있습니다.Wizard는 구성요소를 분석하고 설계에서 이러한 접미사를 찾은 다음 전체 이름 구문을 표시합니다. 올바르지 않다면 드롭다운을 사용해 업데이트하십시오.

- 명명 구문을 정의한 후 Analyze Syntax & Create xSignal Classes 버튼을 클릭하여 xSignal 목록을 생성합니다. Wizard는 구문과 구성요소 연결 방식을 확인하여, 대화상자 오른쪽 표에 표시되는 xSignal Class를 구성합니다. 생성되는 Class 수는 메모리 디바이스에 연결된 Byte-Lane 수와 일치합니다. 표 영역 위에는 생성된 클래스 수(예: 8)와 각 클래스에 포함된 xSignal 넷 수(예: 11)가 표시됩니다.

- 이러한 xSignal Class에 대해 Matched Lengths 설계 규칙이 생성됩니다. 표의 하위 제목은 Byte-Lane xSignal의 소스 및 타깃 구성요소를 나타냅니다.자동 생성된 목록이 불완전하거나 올바르지 않으면 Modify Nets in xSignal Classes 버튼을 클릭하여 Edit xSignal Class 대화상자를 열고, 클래스에 넷을 수동으로 추가하거나 삭제하십시오. 단, 이후 Analyze Syntax & Create xSignal Classes 버튼을 다시 클릭하면 수동 변경 사항은 사라집니다.

- Create Spreadsheet 버튼을 클릭하면 Wizard가 생성한 xSignal을 XLS 형식 스프레드시트로 생성합니다.

- xSignal 및 xSignal Class 생성됨Wizard는 다음에 대해 xSignal 및 xSignal Class를 자동으로 생성합니다.Address Group 페이지에 상세히 설명된 Address xSignal.Data Group 페이지에 상세히 설명된 Data xSignal.

-

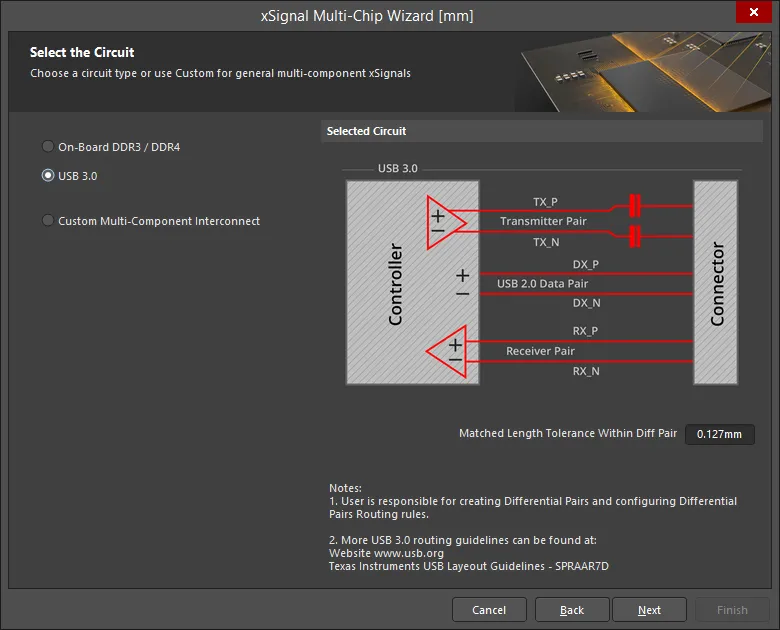

USB 3.0

Wizard는 사용자가 지정한 각 컨트롤러–커넥터 쌍 사이의 모든 USB 3.0 채널을 처리할 수 있습니다. Wizard는 컨트롤러에 연결된 Differential Pair 넷을 자동으로 평가하여 커넥터까지 이어지는(스팬되는) 넷을 감지합니다. 이 스팬에는 수동 소자와 여러 개의 넷이 포함될 수 있습니다. Wizard는 각 페어를 하나의 xSignal class로 식별하며, 페어의 각 레그(+) / (-)는 컨트롤러-커넥터 xSignal로 식별됩니다.

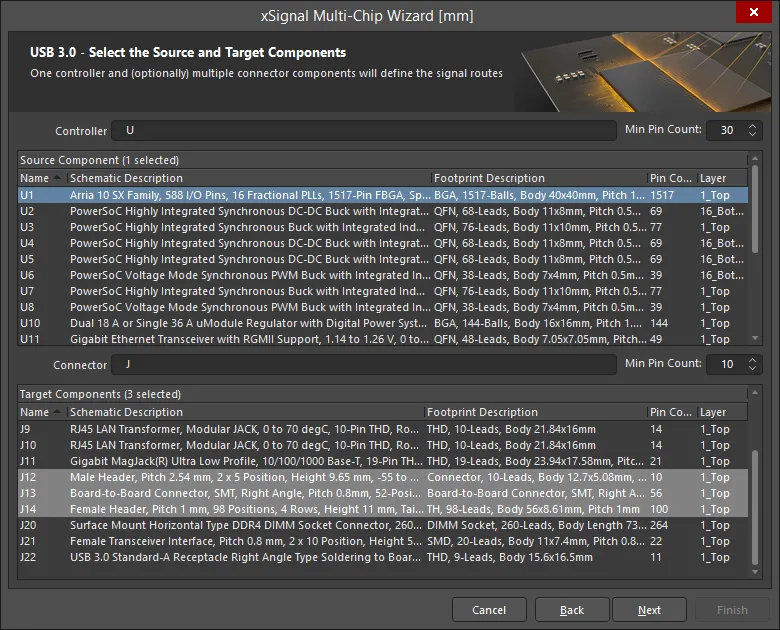

USB 3.0를 선택하면 페이지에 Matched Length Tolerance Within Diff Pair 설정이 포함됩니다. 적절한 값을 입력하십시오. 이 값은 Wizard가 생성하는 설계 규칙에 사용되며, PCB Rules and Constraints Editor에서 언제든지 변경할 수 있습니다. 이러한 사용자 정의 설정은 향후 사용을 위해 저장됩니다.USB 3.0에서 각 USB 사용자 포트는 channel라고 합니다. 이미지에서 보듯이 각 채널에는 Transmit, Receive, Data의 세 가지 차동 페어가 포함됩니다.USB 3.0에서 중요한 라우팅 설계 요구사항은 각 페어 내부에서 라우트 길이를 매칭하는 것이며, 페어 간 길이 매칭은 그만큼 중요하지 않습니다. 이러한 요구사항과 Matched Length 설계 규칙이 차동 페어에서 페어 내부 넷 길이를 확인해야 한다는 점 때문에, Wizard는 Differential Pair 정의가 있는지 확인하고 없으면 적절한 차동 페어를 자동으로 생성합니다. 이후 Wizard가 생성하는 Matched Length 설계 규칙은 Within Differential Pair Length에 대해 길이 매칭을 확인하도록 구성됩니다. 이 규칙은 전체 xSignal에 대해 페어 내 레그 길이를 비교하도록 구성되며, 각 차동 페어 내부의 레그 길이를 비교하는 것은 아닙니다.소스 및 타깃 구성요소 선택이 페이지에서 Wizard는 설계자(designator) 접두사와 핀 수를 기준으로 가능한 모든 소스 구성요소와 타깃 커넥터를 식별합니다.

Controller 설계자, Connector 설계자, 그리고 Min Pin Count 값에 대해 필요에 따라 필터 접두사를 설정하십시오.단일 소스 구성요소를 선택하십시오.

타깃 구성요소(들)를 선택하십시오.여러 타깃 구성요소를 선택한 경우, Wizard의 다음 페이지에서 드롭다운을 사용하여 각 구성요소의 xSignal 및 Net Naming Syntax를 확인해야 합니다.

채널: Differential Pair 그룹 정의

이 페이지에서는 Wizard가 관련 Transmitter, Receiver, Data 페어 넷을 식별하는 데 사용할 명명 구문을 정의하며, 이렇게 식별된 넷은 xSignal에 포함됩니다. 이후 각 xSignal 페어는 xSignal class로 클러스터링되며, 이 클래스는 Matched Length 설계 규칙의 스코프를 지정하는 데 사용됩니다.

- 이 페이지의 기능은 다음과 같습니다.컨트롤러의 설계자가 Components 레이블 옆에 표시됩니다. 그 옆의 드롭다운에는 Wizard의 이전 페이지에서 선택한 모든 Connectors가 포함됩니다.

- 표시되는 명명 구문 옵션은 드롭다운에 나열된 각 커넥터에 적용됩니다. 각 항목을 순서대로 선택하고, 선택된 명명 구문이 완전하며 적합한지 확인하십시오.

- 앞서 언급했듯이 USB 3.0에서 각 USB 사용자 포트는 channel라고 합니다. 채널 수(Channels Total)는 1~32로 설정할 수 있습니다. 일반적으로 각 커넥터는 단일 채널을 가집니다.각 USB 3.0 채널에는 Controller에서 Connector로 이어지는 Transmit, Receive, Data의 세 가지 차동 페어 경로가 있습니다. Wizard는 필요에 따라 직렬(Series) 구성요소를 가로질러 각 양(+) 넷에 대해 하나의 xSignal을, 각 음(-) 넷에 대해 또 하나의 xSignal을 생성한 다음, 해당 Controller-to-Connector 페어를 나타내는 xSignal class를 생성합니다. Define xSignal Class Name Syntax 그룹은 이러한 xSignal class의 이름을 지정하는 데 사용됩니다. 또한 Wizard는 기존에 정의된 것이 없다면 적절한 Differential Pair도 생성합니다.

- Define xSignal Class Name Syntax – 생성되는 xSignal class는 지정된 대로 이름이 붙으며, 각 채널에는

[#] 위치에 숫자 값이 할당됩니다. 필요에 따라 원하는 문자열을 입력하십시오. – 이 필드는 관련 Transmitter / Receiver / Data 넷 이름을 식별하는 데 사용되는 마스크를 정의합니다.

- Channel <N>Wizard에는 미리 정의된 명명 스킴 템플릿이 많이 포함되어 있어 보통 이 필드를 자동으로 채웁니다. 그렇지 않은 경우 드롭다운에서 올바른 이름을 선택하거나 적절한 넷 이름 구문을 직접 입력하십시오.

- 명명 필드를 구성한 후 Analyze Nets & Create xSignal Classes 버튼을 클릭하십시오.

- Wizard는 모든 채널에 대해 xSignal, xSignal Class, Matched Length 규칙을 생성합니다. 이는 Wizard를 다시 실행할 때마다 생성된다는 점에 유의하십시오. Wizard를 다시 실행할 계획이라면 기존 항목을 삭제하십시오.결과로 생성된 xSignal Class 이름과 그에 속한 xSignal이 그리드에 상세히 표시됩니다.

- Create Spreadsheet 버튼을 클릭하면 Wizard가 생성한 xSignal을 XLS 형식 스프레드시트로 생성합니다.

- Finish를 클릭하여 Wizard를 완료합니다.

-

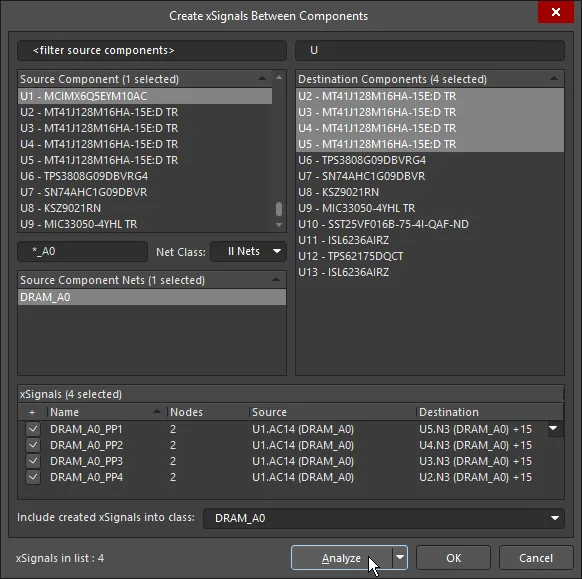

구성요소 간 xSignal 생성 대화상자

정의해야 할 xSignal이 많은 경우 Create xSignals Between Components 대화상자를 사용하는 것이 더 효율적입니다. Design » xSignals » Create xSignals 명령을 통해 접근할 수 있으며, 이 대화상자는 Source 및 Destination 구성요소를 제시하고 한 번의 작업으로 하나 또는 여러 개의 xSignal을 생성할 수 있게 해줍니다.이 대화상자를 사용하면 여러 xSignal을 빠르게 식별하고 생성한 뒤, 필요한 xSignal class에 추가할 수 있습니다.접근 방법은 다음과 같습니다.

단일 Source Component를 선택합니다.

필요한 Destination Components를 하나 이상 선택합니다.

- 관심 있는 Source Net(s)를 선택합니다. 선택한 소스 구성요소에 현재 연결된 모든 넷이 나열됩니다. 특정 클래스에 연관된 넷의 경우 Net Class 드롭다운에서 해당 클래스를 선택하십시오.Analyze 버튼을 클릭합니다. 소프트웨어는 선택한 넷에 대해, 선택한 소스와 대상 구성요소 사이에 존재할 수 있는 xSignal을 식별하려고 시도합니다. 선택한 넷을 포함하고 선택한 소스와 대상 구성요소 사이를 연결하는 가능한 모든 xSignal이 xSignals 필드에 나열됩니다. 분석 알고리즘은 선택한 넷의 현재 토폴로지를 따라가며, 이는 제안되는 xSignal에 영향을 줍니다.

필요한 경우, Analyze 드롭다운에서 적절한 옵션(Search for direct connections, Through 1 series component, Through 2 series components 또는 Multipath coupled nets)을 선택하여 소프트웨어가 직렬(Series) 부품까지 포함해 검색하도록 할 수도 있습니다.

- 분석이 수행되면, 잠재적 xSignal이 대화상자 하단 영역에 나열되며 모두 생성 가능 상태로 활성화됩니다. 제안된 xSignal 목록을 주의 깊게 확인하고, 필요한 것만 활성화하십시오. 여러 항목을 전환하려면 우클릭 컨텍스트 메뉴에서 제공되는 명령을 사용하십시오.

- 대화상자 하단에서 필요한 class을 선택하거나, 이름을 입력해 새 클래스를 생성하십시오. 클래스를 선택하지 않더라도 xSignal은 생성되며, 이후 Object Class Explorer 대화상자(Design » Classes)에서 어떤 xSignal 클래스에도 추가할 수 있습니다. 클래스를 사용하면 설계 규칙의 생성 및 구성을 크게 단순화할 수 있습니다.

- OK을(를) 클릭하여 xSignal을 생성합니다.

대화상자가 닫히고 설계 공간으로 돌아갑니다. 새 xSignal은 PCB 패널의 xSignals 모드에 나열됩니다.

각 목록 위의 필터를 사용하면 관심 있는 부품 또는 넷을 빠르게 찾을 수 있으며, 와일드카드가 지원됩니다.

연결된 넷에서 xSignal 생성(Create xSignals From Connected Nets) 대화상자

직렬 종단(Series termination) 부품을 포함하는 xSignal을 생성하는 경우, Create xSignals from connected nets 명령을 사용하는 것이 좋은 방법입니다. 이 명령은 부품이 선택되어 있을 때 언제든 사용할 수 있으며, 메인 메뉴의 Design » xSignals 하위 메뉴 또는 우클릭 xSignals 하위 메뉴에서 사용할 수 있습니다.

이 명령은 저항이나 커패시터 같은 선택된 직렬 종단 부품을 기준으로 바깥 방향으로 xSignal을 구성하도록 설계되었습니다. 하나 이상의 개별(Discrete) 부품뿐 아니라, 저항 네트워크와 같은 하나 이상의 멀티 인스턴스 팩(pack) 형태 부품도 지원합니다. 이 명령을 실행하면 Create xSignals From Connected Nets 대화상자가 열립니다.

대화상자를 사용하여 선택된 직렬 부품을 가로지르는 xSignal을 생성합니다. 이 예에서는 가능한 xSignal 두 개가 제안되었지만, 그중 하나만 생성됩니다.

절차는 다음과 같습니다.

- 단일 Source Component을 선택합니다.

- 관심 있는 Source Net(s)을 선택합니다. 현재 선택된 소스 부품에 연결된 모든 넷이 나열됩니다. 특정 클래스에 속한 넷의 경우 Net Class 드롭다운에서 해당 클래스를 선택하십시오.

- Analyze 버튼을 클릭합니다. 소프트웨어는 선택한 소스 부품과 선택된 넷에 대해 존재할 수 있는 잠재적 xSignal을 식별하려고 시도합니다. 가능한 모든 xSignal이 xSignals 필드에 나열됩니다.

- 분석이 수행되면, 잠재적 xSignal이 대화상자 하단 영역에 나열되며 모두 생성 가능 상태로 활성화됩니다. 제안된 xSignal 목록을 주의 깊게 확인하고, 필요한 것만 활성화하십시오. 여러 항목을 전환하려면 우클릭 컨텍스트 메뉴에서 제공되는 명령을 사용하십시오.

- 대화상자 하단에서 필요한 class을 선택하거나, 이름을 입력해 새 클래스를 생성하십시오. 클래스를 선택하지 않더라도 xSignal은 생성되며, 이후 Object Class Explorer 대화상자(Design » Classes)에서 어떤 xSignal 클래스에도 추가할 수 있습니다. 클래스를 사용하면 설계 규칙의 생성 및 구성을 크게 단순화할 수 있습니다.

- OK을(를) 클릭하여 xSignal을 생성합니다.

대화상자가 닫히고 설계 공간으로 돌아갑니다. 새 xSignal은 PCB 패널의 xSignals 모드에 나열됩니다.

각 목록 위의 필터를 사용하면 관심 있는 부품 또는 넷을 빠르게 찾을 수 있으며, 와일드카드가 지원됩니다.

넷 토폴로지의 역할

xSignal을 정의할 때는 두 노드 또는 패드 사이로 정의됩니다. 그러나 PCB 패널의 xSignals 모드에서 해당 xSignal을 선택하면, 실제로는 두 패드 사이를 연결하는 연결선 경로를 따라가며, 이는 소프트웨어가 xSignal이 라우팅될 경로로 가정하는 경로임을 나타냅니다. 이렇게 동작하는 이유는 해당 넷에 정의된 토폴로지를 따르기 때문입니다. 넷 토폴로지는 적용되는 Routing Topology 설계 규칙에 의해 정의되며, 기본 토폴로지는 Shortest입니다.

간단한 애니메이션은 CPU가 4개의 DDR3 메모리 칩에 연결되어 있고, 플라이바이(fly-by) 라우팅 전략으로 라우팅될 예정인 상황을 보여줍니다. DRAM_A2 xSignal 클래스에는 4개의 xSignal이 포함되어 있습니다. 먼저 클래스를 선택한 다음, 각 xSignal을 차례로 선택합니다. xSignal 경로가 현재 기본값인 Shortest로 설정된 넷 토폴로지를 어떻게 따라가는지 확인할 수 있습니다.

현재 넷 토폴로지가 Shortest로 설정되어 있기 때문에, xSignal이 프로세서에서 메모리 칩으로 가는 필요한 경로를 따르지 않습니다.

Create xSignals Between Components 대화상자를 사용할 계획이라면, xSignal 분석 알고리즘이 라우팅된 xSignal의 의도된 경로를 이해할 수 있도록 넷의 토폴로지를 구성해야 합니다.

xSignal 생성 명령

Design » xSignals » Create xSignals 명령 외에도, 특정 조건이 충족되면 xSignals 하위 메뉴에 다른 xSignal 생성 명령이 있습니다.

아래는 명령과 사용 가능 조건에 대한 요약입니다.

| 명령 |

설명 |

| Create xSignal from selected pins |

즉시 단일 xSignal을 생성합니다. 이 명령은 설계 공간에서 두 개 이상의 패드가 선택되어 있을 때 사용 가능하며, 선택된 패드 중 하나를 우클릭했을 때 표시되는 명령과 동일합니다.

|

| Create xSignals between components |

이 명령은 설계 공간에서 부품이 선택되어 있을 때 사용 가능합니다. 실행하면 Create xSignals Between Components 대화상자가 열리며, 부품이 미리 선택된 상태로 표시됩니다. 올바른 Source 및 Designation 부품이 선택되어 있는지 확인한 다음 분석/생성 과정을 완료하십시오.

명령을 실행하면 Create xSignals Between Components dialog가 열립니다. 대화상자를 사용하여 다음과 같이 xSignal을 생성합니다.

- 선택한 소스 부품이 Source Component 영역에서 선택된 상태로 표시됩니다.

- 작업 공간에서 선택된 다른 부품은 Destination Components 영역에서 선택된 상태로 표시됩니다. 그렇지 않다면 지금 선택하십시오.

- 기본적으로 소스 부품의 패드와 연관된 모든 넷이(Source Component Nets 영역에서) 선택됩니다. 필요에 따라 이 선택을 조정하십시오.

-

Analyze 버튼을 클릭합니다. 소프트웨어는 선택된 넷에 대해, 선택한 소스 부품과 대상 부품 사이에 존재할 수 있는 잠재적 xSignal을 식별하려고 시도합니다.

분석 알고리즘은 선택된 넷의 현재 토폴로지를 따른다는 점에 유의하십시오.

필요한 경우, 버튼에 연결된 드롭다운 메뉴에서 적절한 모드를 선택하여 소프트웨어가 직렬 부품까지 포함해 검색하도록 할 수도 있습니다. 사용 가능한 모드는 Search for direct connections, Through 1 series component, Through 2 series components, Multipath coupled nets입니다.

- 식별된 모든 xSignal은 대화상자의 xSignals 영역에 나열됩니다. 기본적으로 모두 생성 대상으로 선택되어 있으므로 필요에 따라 조정하십시오.

- 생성된 xSignal을 xSignal 클래스에 연결하도록 선택할 수 있습니다. 기존 xSignal 클래스를 선택하거나 새 클래스 이름을 입력하십시오. 원한다면 필드를 비워둘 수도 있으며, xSignal은 나중에 언제든 필요한 클래스의 멤버로 추가할 수 있습니다.

- OK 을(를) 클릭하여 xSignal을 생성합니다. 대화상자가 닫히고 설계 공간으로 돌아가며, 새로 생성된 xSignal을 보여주는 필터링된 뷰가 표시됩니다. xSignal 클래스가 지정되었다면(기존에 없을 경우) 생성되고, xSignal이 해당 클래스에 연결됩니다.

|

| Create xSignals from connected nets |

하나 이상의 직렬 종단 부품에 대해 xSignal을 생성해야 할 때 이 명령을 사용하십시오. 종단 부품을 선택한 다음 명령을 실행하여 Create xSignals from Connected Nets 대화상자를 열고, xSignal 세트를 생성하는 과정을 완료할 준비를 합니다. 대화상자를 사용하여 다음과 같이 xSignal을 생성합니다.

- 선택한 소스 부품이 Source Component 영역에서 선택된 상태로 표시됩니다.

- 기본적으로 소스 부품의 패드와 연관된 모든 넷이(Source Component Nets 영역에서) 선택됩니다. 필요에 따라 이 선택을 조정하십시오.

-

Analyze 버튼을 클릭합니다. 소프트웨어는 선택한 부품에서 뻗어나오는 선택된 넷에 대해 존재할 수 있는 잠재적 xSignal을 식별하려고 시도합니다.

분석 알고리즘은 선택된 넷의 현재 토폴로지를 따른다는 점에 유의하십시오.

- 식별된 모든 xSignal은 대화상자의 xSignals 영역에 나열됩니다. 기본적으로 모두 생성 대상으로 선택되어 있으므로 필요에 따라 조정하십시오.

- 생성된 xSignal을 xSignal 클래스에 연결하도록 선택할 수 있습니다. 기존 xSignal 클래스를 선택하거나 새 클래스 이름을 입력하십시오. 원한다면 필드를 비워둘 수도 있으며, xSignal은 나중에 언제든 필요한 클래스의 멤버로 추가할 수 있습니다.

- OK 을(를) 클릭하여 xSignal을 생성합니다. 대화상자가 닫히고 설계 공간으로 돌아가며, 새로 생성된 xSignal을 보여주는 필터링된 뷰가 표시됩니다. xSignal 클래스가 지정되었다면(기존에 없을 경우) 생성되고, xSignal이 해당 클래스에 연결됩니다.

|

| Create xSignals |

Create xSignals Between Components 대화상자를 엽니다. 이 명령은 항상 사용 가능합니다. 대화상자를 사용하여 다음과 같이 xSignal을 생성합니다.

- Source Component 영역에서 소스 부품을 선택합니다.

- Destination Components 영역에서 하나 이상의 대상 부품을 선택합니다.소스 부품의 패드와 연관된 모든 넷이 Source Component Nets 영역에 나열됩니다. 관심 있는 넷을 선택하십시오.

-

Analyze 버튼을 클릭합니다. 소프트웨어는 선택된 넷에 대해, 선택한 소스 부품과 대상 부품 사이에 존재할 수 있는 잠재적 xSignal을 식별하려고 시도합니다.

분석 알고리즘은 선택된 넷의 현재 토폴로지를 따른다는 점에 유의하십시오.

필요한 경우 버튼에 연결된 드롭다운 메뉴에서 적절한 모드를 선택하여 시리즈(Series) 컴포넌트까지 포함해 검색할 수도 있습니다. 사용 가능한 모드는 Search for direct connections, Through 1 series component, Through 2 series components, Multipath coupled nets입니다.

- 식별된 모든 xSignal은 대화상자의 xSignals 영역에 나열됩니다. 기본적으로 모두 생성 대상으로 선택되어 있으므로, 필요에 따라 조정하십시오.

- 생성된 xSignal을 xSignal 클래스에 연결하도록 선택할 수도 있습니다. 기존 xSignal 클래스를 선택하거나 새 클래스 이름을 입력하십시오. 원한다면 필드를 비워둘 수 있으며, xSignal은 나중에 언제든지 필요한 클래스의 멤버로 추가할 수 있습니다.

- OK 을(를) 클릭하여 xSignal을 생성합니다. 대화상자가 닫히고 설계 공간으로 돌아가며, 새로 생성된 xSignal만 표시되도록 필터링된 뷰가 나타납니다. xSignal 클래스가 지정되어 있었다면 해당 클래스가(없을 경우) 생성되고 xSignal이 그 클래스에 연결됩니다.

|

Balanced T 패턴에서 분기점 정의하기

Balanced T 라우팅 전략의 과제 중 하나는 T 지점 이후의 트렁크(trunk)와 브랜치(branch) 길이를 어떻게 동일하게 맞출 것인가입니다. 넷에서 사용 가능한 노드는 패드에만 있으므로, 트렁크용 xSignal과 분기점부터 각 브랜치 끝까지의 xSignal을 별도로 정의할 수 없습니다. 분기점은 아래 이미지의 빨간 점으로 표시되어 있습니다.

이 문제를 해결하는 한 가지 방법은 넷에 단일 핀 컴포넌트를 추가하는 것입니다. 설계에서 사용 중인 비아 크기와 동일한 단일 패드를 가진 컴포넌트를 생성하십시오. 분기점 컴포넌트 패드가 단일 레이어라면, 비아의 시작 또는 끝 레이어에 배치하여 블라인드/버리드 비아와 조합해 사용할 수도 있으므로 라우팅 생성 방식에 대한 완전한 유연성을 제공합니다. PCB에 분기점 컴포넌트만 포함하고 싶다면, 분기점 컴포넌트의 Type을(를) Mechanical(으)로 설정하여 BOM에서 제외하고 회로도와의 동기화 문제를 방지하십시오. 분기점 컴포넌트를 회로도에 포함할 계획이라면 컴포넌트 Type을(를) Standard (no BOM)(으)로 설정할 수 있습니다.

Balanced T 라우팅은 중간 분기점 간의 길이 매칭이 필요할 수 있습니다.

분기점이 넷의 노드가 되었으므로, 이제 트렁크만을 위한 xSignal, 각 주요 브랜치용 xSignal, 필요하다면 각 보조 브랜치용 xSignal까지 정의할 수 있습니다. 그런 다음 이를 사용해 매칭 길이 설계 규칙의 범위를 지정할 수 있어, 길이 매칭을 어느 정도 세밀하게 수행할지에 대해 설계자가 완전한 제어권을 갖게 됩니다.

xSignal 관리

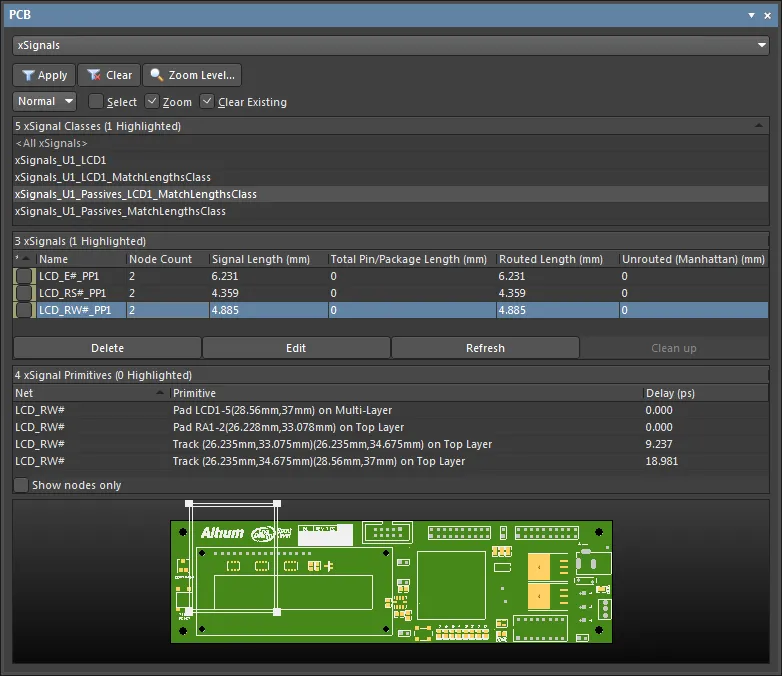

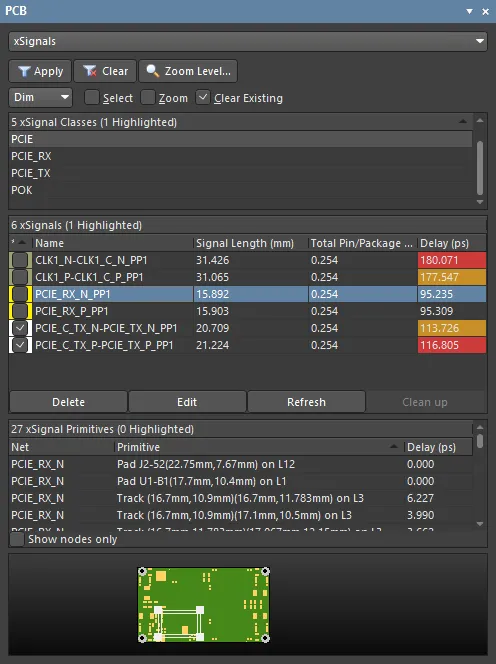

PCB 패널의 모드에서, 세 개의 주요 영역은 현재 PCB 설계의 xSignal 계층 구조를 반영하도록(위에서부터 순서대로) 변경됩니다.

- xSignal Classes

- 클래스

- 내의 개별 xSignalsxSignal을 구성하는 개별 xSignal Primitives (패드, 트랙, 비아)

xSignal 클래스 영역

xSignal Classes 영역에는 정의된 xSignal 클래스 컬렉션 또는 모든 사용 가능한 클래스(<All xSignals>)가 나열됩니다.

클래스를 선택하면 가운데 영역(xSignals)에 해당 xSignal 목록이 표시되고, PCB 설계 공간에도 표시됩니다.

기존 xSignal 컬렉션에서 새 xSignal 클래스를 만들려면 해당 영역에서 마우스 오른쪽 버튼을 클릭한 다음 컨텍스트 메뉴에서 Add Class을(를) 선택하여 Edit xSignal Class dialog를 엽니다. 이 대화상자에는 새 클래스에 멤버로 추가/제거할 수 있는 사용 가능한 xSignal이 나열되며, 관리 버튼을 통해 조정할 수 있습니다. Name 필드에서 새 xSignal 클래스에 적합한 이름을 정의하십시오.

Edit xSignal Class 대화상자에서 xSignal 멤버를 추가/제거하여 xSignal 클래스를 생성하거나 기존 클래스에 추가할 수 있습니다.

패널 영역의 오른쪽 클릭 컨텍스트 메뉴에서는 제거(Delete) 또는 PCB 설계 공간에서의 시각적 표현 변경(예: Change xSignal Color)도 제공합니다.

xSignals 영역

패널의 가운데 영역에는 위 영역에서 선택한 xSignal 클래스의 xSignal이 표시됩니다.

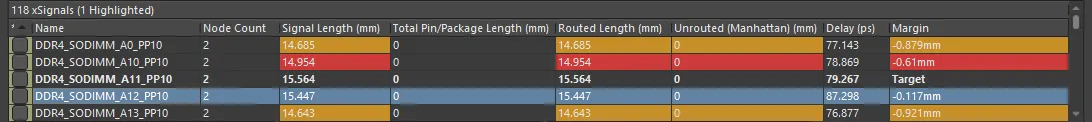

기본적으로 각 xSignal에는 다음 정보가 함께 표시됩니다.

-

– 이 기능은 두 가지 역할을 합니다:

– 이 기능은 두 가지 역할을 합니다:

- 색상 배경 – xSignal에 할당된 색상(설계 공간에서 xSignal을 나타내는 얇은 선). 마우스 오른쪽 버튼을 클릭하여 현재 선택된 모든 xSignal에 대해 Change xSignal Color 을(를) 수행합니다.

- 가시성 체크박스 – 현재 선택 여부와 관계없이 xSignal을 항상 표시하려면 사용합니다.

- Name – xSignal의 이름.

- Node Count – 이 xSignal에 포함된 패드의 총 개수.

- Routed Length – 라우팅을 구성하는 배치된 트랙 및 아크 세그먼트 길이의 합 + 비아를 통해 이동한 수직 거리(아래 참고). 라우팅 길이 계산기는 겹치는 트랙 세그먼트나 패드 내부의 라우팅 지그재그(wiggle)를 해석하려고 시도하지 않습니다.

- Signal Length – 노드-노드 총 거리의 정확한 계산. 신호 길이 계산에는 다음 사항이 적용됩니다:

- Total Pin/Package Length – 해당 xSignal의 모든 패드에 있는 모든 Pin Package Length 값의 합. 이 값은 PCB 패드의 속성으로 정의되며 회로도 핀에서도 지정할 수 있습니다.

- Unrouted (Manhattan) Length – 라우팅되지 않은 모든 구간의 수직 + 수평(X+Y) 거리.

- Margin – 실제 신호 길이와 적용 가능한 Length/Matched Length 설계 규칙에서 정의된 목표 신호 길이의 차이.

영역에서 마우스 오른쪽 버튼을 클릭한 다음 Columns 하위 메뉴를 사용하여 다음 열을 추가할 수 있습니다.

- Delay – 신호가 해당 경로를 따라 전파되는 데 걸리는 시간.

Columns 하위 메뉴를 사용하여 열을 표시/숨길 수 있습니다.

Vertical distance through a via – 비아를 통해 신호가 이동하는 수직 거리는 시작 레이어와 종료 레이어의 구리층 사이에 있는 모든 레이어 두께(구리 및 유전체)의 합에, 시작 레이어 두께의 절반과 종료 레이어 두께의 절반을 더한 값입니다. 레이어 두께는

Layer Stack에서 정의됩니다.

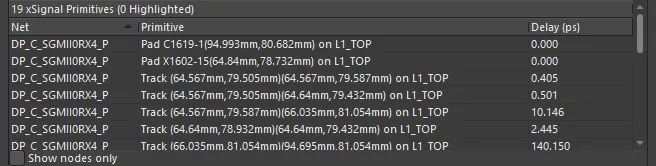

xSignal 프리미티브 영역

PCB 패널의 세 번째 영역인 xSignal Primitives에는 현재 선택된 xSignal을 구성하는 모든 요소(프리미티브)가 나열됩니다.

Show nodes only 체크박스를 선택하면 프리미티브 목록을 xSignal 시작/끝 지점 노드인 패드로 제한합니다. 이 모드에서는 선택된 xSignal이 PCB 설계 공간에서 xSignal 경로를 나타내는 얇은 트레이스(트랙이 아님)로 연결된 노드 패드로 표시됩니다.

아래쪽 xSignal Primitives 영역에는 패드, 비아, 트랙 등 선택된 xSignal의 모든 요소와 해당 지연이 나열됩니다.

설계 공간에서 xSignal 표시하기

xSignal은 설계 공간에서 얇은 선으로 표시됩니다. 이 선은 xSignal이 따라가는 경로를 나타냅니다. 선의 전체 길이는 해당 xSignal의 신호 길이에 대한 X/Y 기여분입니다. 전체 신호 길이에 대한 Z(수직) 기여분은 위에서 설명했습니다.

아래 이미지에서는 차동쌍의 xSignal이 표시되어 있습니다. 패널에서 해당 xSignal의 체크박스가 활성화되어 있으므로, 쌍의 선택되지 않은 멤버에 대한 xSignal도 계속 표시됩니다.

xSignal은 설계 공간에서 얇은 선으로 표현됩니다. 이 차동쌍에서 패널에서는 하나만 선택되어 있어도 가시성 체크박스가 활성화되어 있으므로 두 xSignal 모두 계속 표시됩니다.

xSignal 삭제하기

패널에서 xSignal을 선택한 다음 xSignal 목록 아래의 Delete 버튼을 클릭하십시오. 또는 마우스 오른쪽 버튼을 클릭하고 컨텍스트 메뉴에서 Delete을(를) 선택하거나, 키보드에서 Delete을(를) 누르십시오.

xSignal 쿼리 키워드

PCB 편집기에는 강력하고 정교한 filtering engine이(가) 포함되어 있습니다. 이 엔진은 설계 공간에서 객체를 검색할 때, 대화형 및 자동 설계 작업 중 규칙을 적용할 때, 그리고 규칙 준수 여부를 검사할 때 객체를 식별하는 데 사용됩니다. 설계자는 필터링 엔진이 인식하는 쿼리 키워드를 사용해 쿼리를 작성함으로써, 어떤 객체에 관심이 있는지 필터링 엔진에 알려줍니다.

설계 규칙 및 설계 공간 필터에서 사용하기 위해 다음 xSignal 유형 쿼리 키워드가 추가되었습니다.

멤버십 확인 유형 키워드

- InxSignal - 객체가 지정된 xSignal에 속하는가, 예:

InxSignal('DRAM_A0_PP1')

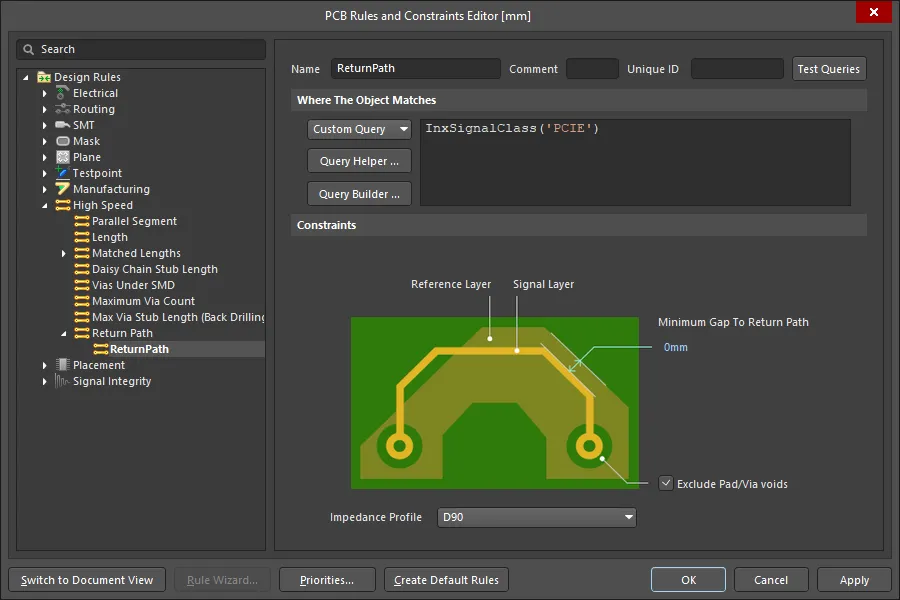

- InxSignalClass - 객체가 지정된 xSignal 클래스에 속하는가, 예:

InxSignalClass('PCIE')

- IsxSignal - 객체가 지정된 이름의 xSignal인가, 예:

IsxSignal('DRAM_A0_PP1')

속성 확인 유형 키워드

- InAnyxSignal - 객체가 어떤 xSignal에든 속하는가, 예:

InAnyxSignal

xSignal에 대한 설계 규칙 지원

설계 규칙은 요구사항을 PCB 편집기가 이해하고 준수할 수 있는 지침 집합으로 변환하는 방법입니다. 규칙은 객체 배치 중(Online DRC) 또는 후처리(Batch DRC)로 검사할 수 있습니다. xSignal은 설계 규칙을 적용해야 하는 객체를 정의하는 데 사용할 수 있습니다.

► Design Rules에 대해 더 알아보기

► Length Tuning에 대해 더 알아보기

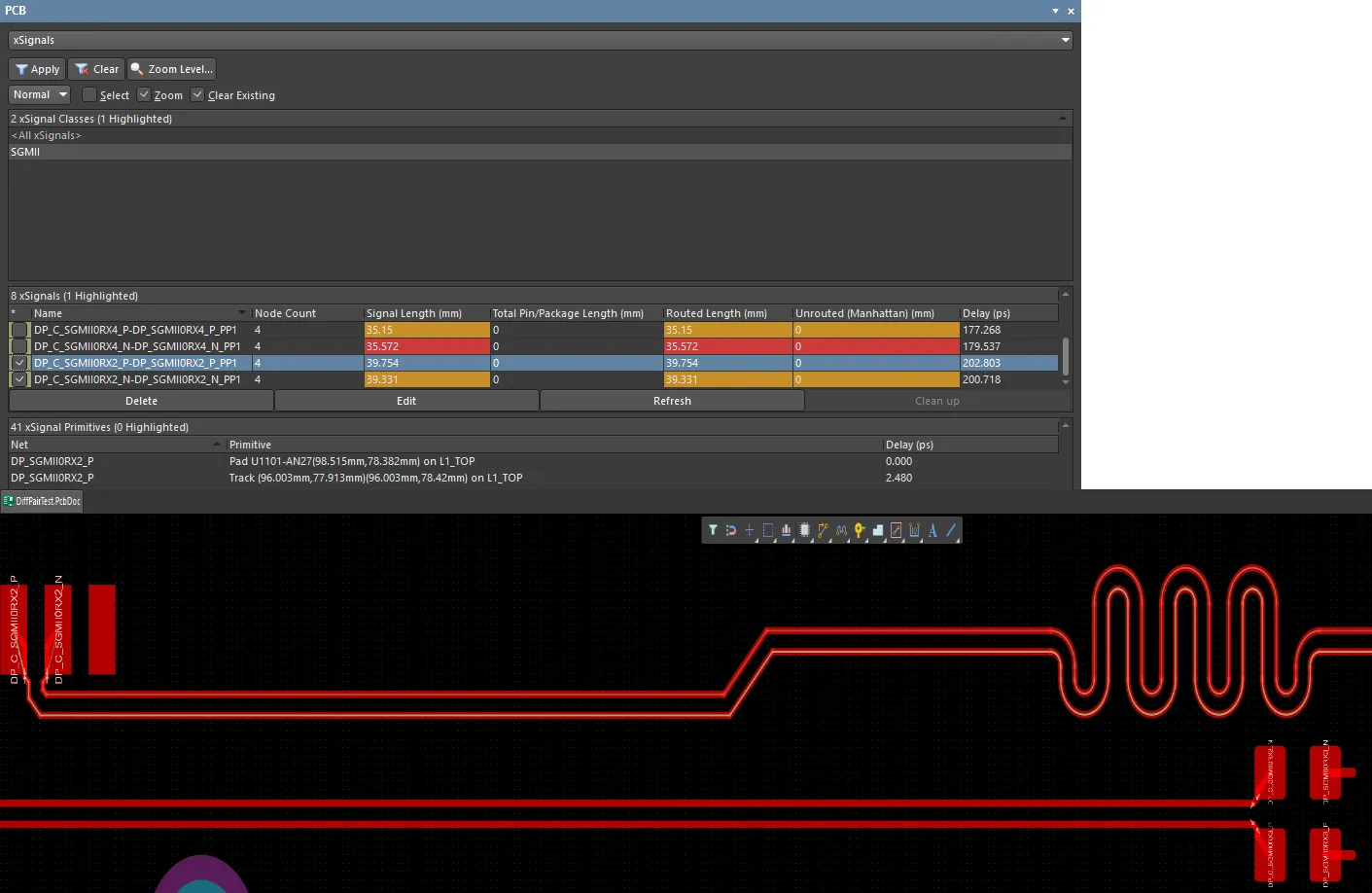

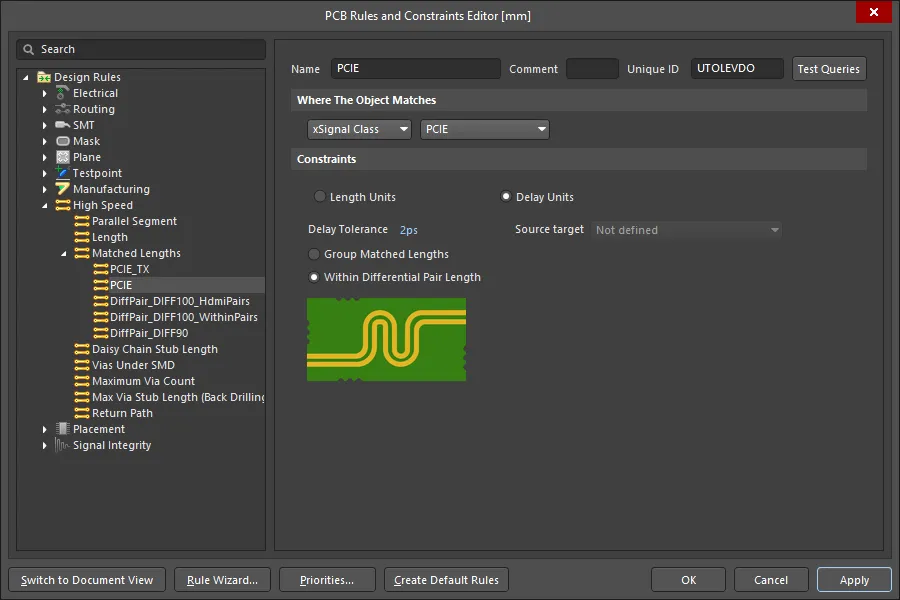

Matched Length Rule

Matched Length design rule은 지정된 넷의 길이가 지정된 범위 내에 있도록 보장하는 데 사용됩니다. 이 규칙은 고속 설계에서 필수적인데, 여기서의 과제는 신호가 도착하는 데 걸리는 시간(전체 길이에 의해 결정됨)만이 아니라, 지정된 신호들이 동일한 시점에 도착하는 것이 얼마나 중요한가에 있습니다. 신호 스위칭 속도, 신호의 기능, 보드에 사용된 재료에 따라 허용되는 차이는 500mils까지 클 수도 있고 1mil만큼 작을 수도 있습니다.

아래 이미지는 xSignal 클래스 PCIE에 있는 xSignals를 대상으로 하도록 Matched Length 설계 규칙을 구성하고, 해당 xSignals 클래스 내 각 차동 페어에서 길이 차이가 규정 범위 내인지 테스트하는 예를 보여줍니다. 클래스의 각 페어는 라우팅 길이가 해당 페어의 두 넷 간 Delay Tolerance이(가) 2ps 지연을 넘지 않도록 해야 합니다.

Matched Length 설계 규칙의 Constraints에서는, 대상이 된 모든 넷의 길이를 매칭할지(Group Matched Lengths) 또는 대상 넷에 포함된 각 diff pair 내부의 두 넷을 매칭할지 중에서 선택해야 합니다.

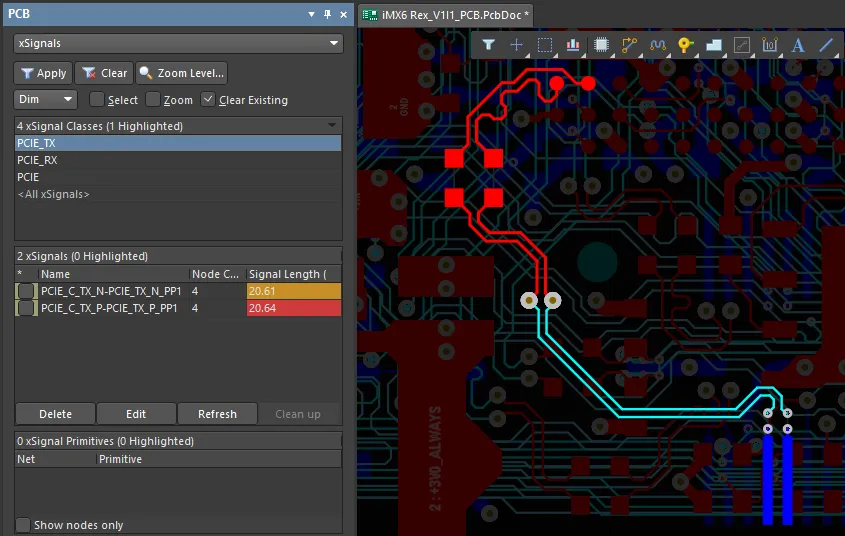

아래 이미지는 패널에서 PCIE_TX xSignal 클래스가 선택되어 있고, 설계 공간에서 해당 xSignals가 선택된 상태를 보여줍니다.

PCIE 클래스뿐 아니라 TX 및 RX 페어에 대한 클래스도 정의되어 있습니다. TX xSignals 중 하나가 적용되는 matched length 규칙을 위반한다는 점에 유의하세요. ##

단일 넷과 차동 페어를 모두 포함하는 xSignals를 길이 튜닝할 계획이라면, 다음 규칙을 생성하세요.

- 길이 매칭 요구사항을 정의하는 matched length 규칙 between nets and differential pairs in xSignals. 한 넷/페어의 길이를 다른 넷/페어의 길이와 비교해 테스트하도록 규칙을 구성하려면 Group Matched Lengths 옵션을 활성화합니다.

- 더 높은 우선순위를 갖고 within-pair 길이 매칭 요구사항을 정의하는 두 번째 matched length 규칙. 한 페어의 멤버를 다른 페어 멤버와 비교해 테스트하도록 규칙을 구성하려면 Within Differential Pair Length 옵션을 활성화합니다.

이러한 xSignals의 길이를 튜닝하는 좋은 방법은 다음과 같습니다.

- xSignal의 넷과 차동 페어를 라우팅합니다.

- Interactive Length Tuning 명령을 사용해 단일 넷을 길이 튜닝합니다.

- between 명령을 사용해 페어를 길이 튜닝합니다. 길이 튜닝은 가장 긴 페어에서 가장 긴 신호 길이를 Target Length로 사용하고, 페어 내에서 가장 긴 넷을 이 길이에 맞춰 튜닝합니다.

- within 명령을 사용해 각 페어에서 더 짧은 넷을 페어의 다른 넷에 대해 길이 튜닝합니다.

- 이제 PCB Rules and Violations 패널을 사용해 within-pair Matched Net Length 규칙을 확인할 수 있습니다. 이를 위해 패널의 Rule Classes 섹션에서 Matched Net Lengths 을(를) 선택한 다음, 필요한 Matched Length 규칙을 마우스 오른쪽 버튼으로 클릭하고 컨텍스트 메뉴에서 Run DRC Rule <RuleName> 명령을 선택합니다. 필요하다면 단일 넷 튜닝 아코디언을 조정합니다.

- 그런 다음 방금 설명한 프로세스를 사용해 PCB Rules and Violations 패널에서 between-pair Matched Net Length 규칙을 확인합니다. 필요하다면 차동 페어 튜닝 아코디언을 조정합니다.

Length Rule

Length design rule은 전체 라우팅 길이가 지정된 범위 내에 있도록 보장하는 데 사용됩니다. 이 규칙은 일반적으로 대상 넷이 지정된 길이보다 길지 않도록 보장하는 데 사용되며, 예를 들어 회로 타이밍 요구사항이 충족되도록 하기 위함입니다. Length 규칙은 위에 나열된 xSignal 타입 쿼리를 준수합니다.

Return Path Rule

Return Path design rule은 규칙이 대상으로 하는 신호의 위 또는 아래에 있는 지정된 기준 레퍼런스 레이어에서 연속적인 신호 리턴 경로가 존재하는지 확인합니다. 리턴 경로는 신호 레이어에 배치된 fill, region, polygon pour로 만들 수 있으며, 또는 plane 레이어일 수도 있습니다.

리턴 경로 레이어는 선택된 Impedance Profile에 정의된 레퍼런스 레이어입니다. High Speed 규칙 카테고리에서 새 Return Path 설계 규칙을 추가하세요.

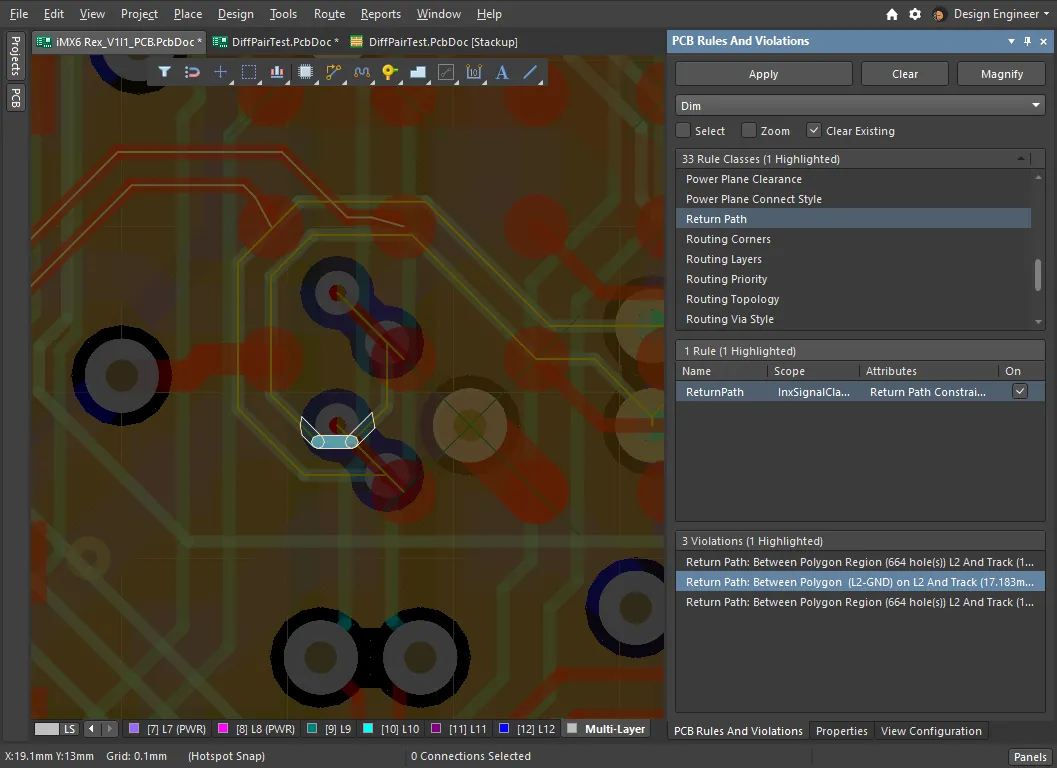

아래 이미지는 Return Path 규칙 위반의 예를 보여주며, xSignal 리턴 경로 폴리곤에 비아가 통과할 수 있도록 구멍이 있는 경우입니다.

PCB Rules and Violations 패널을 사용해 Return Path 규칙 위반을 찾는 모습. ##

PCB Rules and Violations 패널을 사용해 Return Path 규칙 위반을 찾는 모습. ##

Accurate Length Calculations

고속 설계 규칙을 정의하는 데 있어 핵심 요구사항은 라우트 길이를 정확하게 계산하는 것입니다. 신호 길이를 계산하는 전통적인 접근 방식은 라우트에 사용된 모든 세그먼트의 중심선 길이를 합산하고, 비아 높이로 인한 수직 거리(원래는 보드 두께로 결정됨)도 더하는 것입니다.

이 접근 방식은 다음을 포함한 여러 이유로 고속 설계에는 충분하지 않습니다.

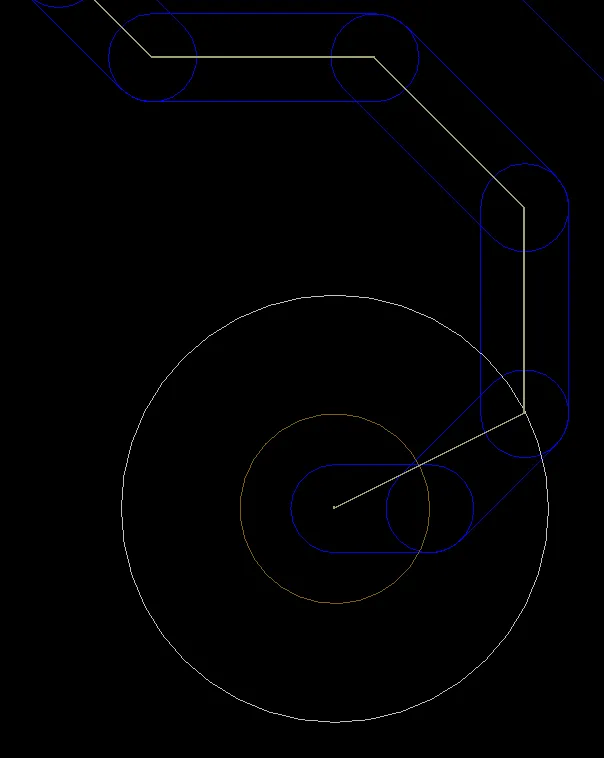

- 적층 및 중첩 객체 - 넷에 포함된 모든 객체의 중심선 길이를 단순히 더하는 알고리즘은 적층되거나 겹쳐진 객체를 처리하지 못합니다.

- 객체 내부에서의 굴곡진 라우트 경로 - 패드나 비아 내부에 완전히 포함된 라우팅 객체가 있는 경우가 많으며, 이는 아래 첫 번째 이미지에서 보듯이 길이에 잘못 더해질 수 있습니다. 두 번째 이미지는 fill 객체가 라우팅의 일부일 때 길이를 계산하는 올바른 방법을 보여줍니다.

- 비아 길이 - 블라인드/버리드 비아는 보드의 모든 레이어를 관통하지 않으므로, 보드 두께만으로는 수직 길이를 충분히 정확하게 결정할 수 없습니다. 비아가 통과하는 구리 및 절연 두께를 고려하여 실제 비아 높이를 사용해야 합니다.

PCB 편집기의 길이 계산기는 가능한 한 가장 정확한 라우트 길이를 반환합니다.

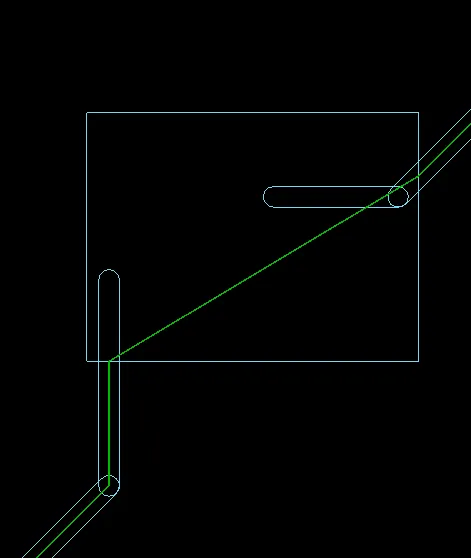

길이 계산은 아래 두 이미지에 보이는 것처럼 최단 경로의 중심선을 따라 정확하게 계산됩니다.

비아에 대해서는 통과하는 레이어와 스택업 치수에 기반한 정확한 길이가 계산됩니다. 이미지는 Nets 모드의 PCB 패널에서 가져온 것입니다.

Pin Package Delay

500 MHz를 초과하는 모든 고속 설계에서, 연결 매체(다이까지의 본드 와이어)는 신호에 지연을 유발합니다. 이러한 디바이스 내부 지연을 핀-패키지 지연(pin-package delay)이라고 합니다. 두 디바이스가 설계 및 PCB 관점에서 완전히 핀 호환이더라도, 패키지 비행 시간(flight time)은 디바이스마다 다르므로 이를 고려해야 합니다. 비행 시간 정보는 해당 디바이스의 IBIS 6 문서에서 찾을 수 있습니다. 패키지 핀 정보는 I/O 플래닝 단계에서, 또는 FPGA의 경우 합성(synthesis) 이후에 고려되어야 합니다. 모든 디바이스 제조사는 패키지 지연을 제공할 수 있어야 하며, 이는 피코초 지연 또는 길이로 지정됩니다.

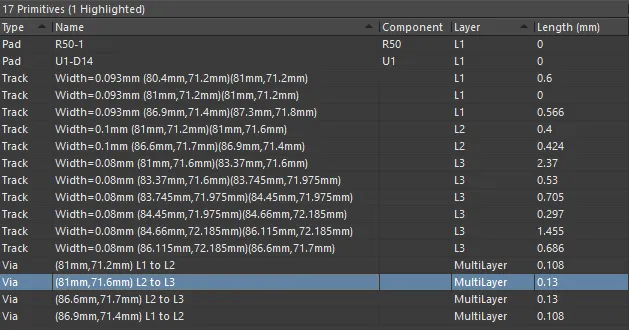

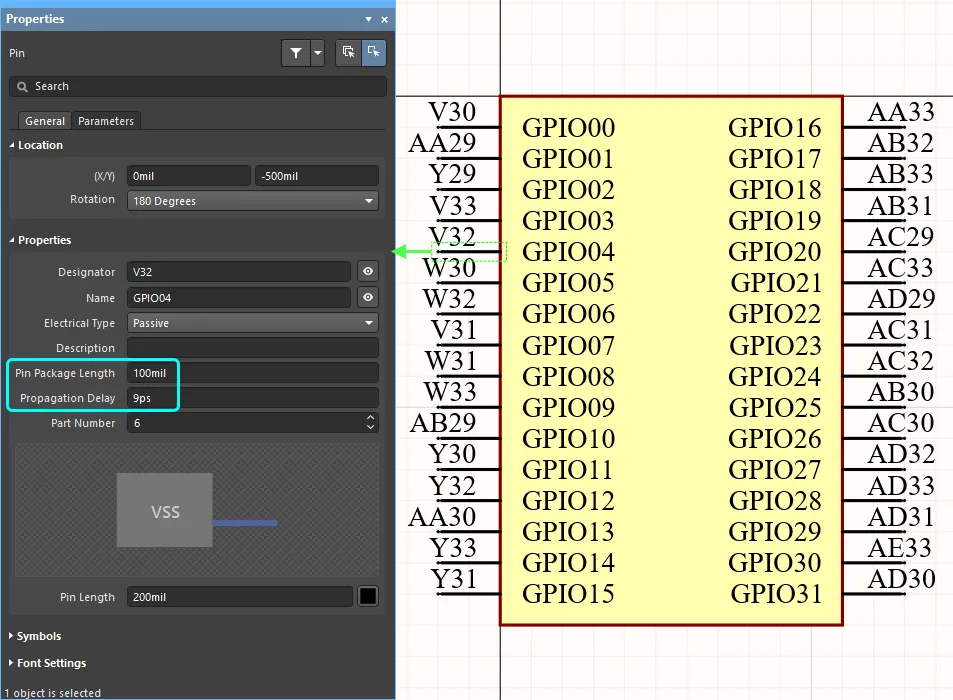

지연은 설계에 Pin Package Length 또는 Propagation Delay(으)로 포함할 수 있으며, 회로도 편집기에서는 핀에 대한 해당 필드를, PCB 편집기에서는 패드/비아에 대한 해당 필드를 사용합니다. 입력된 값은 다음과 같이 처리됩니다.

Pin Package Length - 각 넷 내의 모든 핀 패키지 길이는 PCB 편집기에서 합산되어 Total Pin/Package Length가 되며, 이는 해당 넷의 전체 Signal Length에 포함됩니다. PCB 패널의 Nets 모드를 참조하여 Signal Length에 대해 더 알아보세요.

Propagation Delay - 각 넷에서 핀/패드 및 비아에 대해 사용자가 정의한 모든 지연 값은 PCB 편집기에서 해당 넷의 라우팅 지연에 더해집니다. 라우팅 지연은 Layer Stack Manager에 내장된 Simbeor® 필드 솔버가 자동으로 계산합니다. 패드 및 비아 지연은 자동으로 계산되지 않지만 사용자가 정의할 수 있습니다.

- Length 및 Matched Length 설계 규칙은 Length 또는 Delay를 기준으로 구성할 수 있습니다.

- Signal Length, Total Pin/Package Length 및 Delay는 PCB 패널의 다양한 모드(예: Nets mode, Differential Pairs Editor mode, xSignals mode)에서 표시할 수 있습니다. PCB 패널에서 열 머리글을 마우스 오른쪽 버튼으로 클릭하여 열을 활성화/비활성화할 수 있습니다.

- Simberian®의 Simbeor SFS(준정적 필드 솔버)는 Layer Stack Manager에 정의된 물리적 특성을 기반으로 라우팅 지연을 계산하는 데 사용됩니다.

- 사용자 정의 Pin Package Length와 Propagation Delay 값은 서로 독립적이며, 앞서 설명한 대로 Signal Length 및 Delay 값에 더해집니다. 서로 상호작용하지 않기 때문에, 필요하다면 두 값 모두를 지정할 수 있습니다.

Including the Delay in the Schematic

핀 패키지 길이는 Pin 모드의 Properties 패널에서 회로도 컴포넌트 핀의 속성으로 정의할 수 있습니다. 소프트웨어는 기본적으로 기반 문서의 Units를 사용하며, 필요하다면 값과 함께 단위를 입력하세요.

필요한 단위로 핀-패키지 길이를 입력합니다.

- 컴포넌트 핀 속성은 라이브러리 편집기에서 또는 회로도 시트에서 Component 모드의 Properties 패널 Pins 탭에서 편집할 수도 있습니다. 패널의 해당 탭에서

을(를) 클릭하면 Component Pin Editor가 열리며, 그 컴포넌트의 모든 핀에 대한 모든 속성을 편집할 수 있습니다. 그리드에서 직접 값을 편집할 수 있고(셀을 선택한 뒤 새 값을 입력), 커서 키로 인접 셀로 이동할 수 있습니다. 단위를 입력하지 않으면 기본 단위가 자동으로 추가됩니다.

을(를) 클릭하면 Component Pin Editor가 열리며, 그 컴포넌트의 모든 핀에 대한 모든 속성을 편집할 수 있습니다. 그리드에서 직접 값을 편집할 수 있고(셀을 선택한 뒤 새 값을 입력), 커서 키로 인접 셀로 이동할 수 있습니다. 단위를 입력하지 않으면 기본 단위가 자동으로 추가됩니다.

- 또는 SCH List panel을 사용해 데이터시트의 여러 Pin/Pkg Lengths 또는 Propagation Delay 값을 복사/붙여넣기하여, 회로도 라이브러리 편집기에서 선택한 컴포넌트 핀 집합에 적용할 수 있습니다(show image

![]() ). 선택한 셀에 클립보드 내용을 직접 붙여넣는 것뿐 아니라, 패널에서 마우스 오른쪽 버튼을 클릭해 Smart Grid Paste dialog에 접근할 수도 있으며, 이를 통해 핀에 추가 데이터를 가져오는 과정을 더 세밀하게 제어할 수 있습니다.

). 선택한 셀에 클립보드 내용을 직접 붙여넣는 것뿐 아니라, 패널에서 마우스 오른쪽 버튼을 클릭해 Smart Grid Paste dialog에 접근할 수도 있으며, 이를 통해 핀에 추가 데이터를 가져오는 과정을 더 세밀하게 제어할 수 있습니다.

Defining the Delay in the PCB Editor

Pin Package Length 및 Propagation Delay 값은 Properties panel의 Pad mode에서 보이는 것처럼 PCB 레이아웃으로 전송됩니다.

Pin Package Length 및 Propagation Delay 값은 회로도에서 PCB로 전송되며, PCB에서 직접 정의할 수도 있습니다.

Examining the Pin/Package Length and the Propagation Delay in the PCB Panel

Pin/Pkg Length은(는) Signal Length 계산에 자동으로 포함되며, 이 계산 결과는 PCB panel의 다양한 모드에서 표시됩니다. 선택한 넷의 핀에 대한 Pin/Pkg Length 값을 확인(또는 편집)하려면 패널을 Nets mode로 설정하세요. Routed Length 열은 라우팅 길이를 반영하고, Signal Length 열은 라우팅 길이에 해당 넷의 Pin/Pkg Length를 더한 길이를 반영한다는 점에 유의하세요.

Pin/Pkg Length 및 이것이 Signal Length에 미치는 영향은 PCB panel의 Nets mode에 표시됩니다.

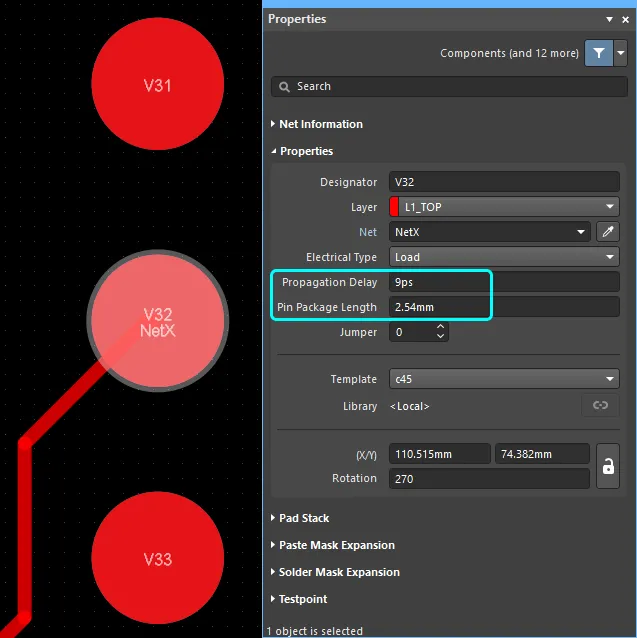

아래 이미지에서 propagation Delay 열은 Matched Length 설계 규칙을 위반하는 xSignals 쌍이 두 개 있음을 보여줍니다. 하이라이트가 Delay 열에 표시되므로, 해당 규칙이 Length Units가 아니라 Delay Units를 사용하도록 구성되어 있음을 의미합니다.

Delay 열은 Matched Length 설계 규칙을 위반하는 xSignals 쌍이 두 개 있음을 보여줍니다.

Delay 열은 Matched Length 설계 규칙을 위반하는 xSignals 쌍이 두 개 있음을 보여줍니다.

How the Length is Included in xSignals

다음 조건을 만족하면 Pin/Pkg Length은(는) 전체 xSignal 길이에 자동으로 포함됩니다.

-

해당 신호가 xSignal 정의의 일부인 경우

해당 패드가 플라이바이(fly-by) 라우팅 패턴으로 연결되어 있지 않은 경우(그 패드에 연결된 트레이스가 하나뿐인 경우)

플라이바이 라우팅 패턴(진입점과 이탈점이 있는 형태)으로 연결된 패드는 길이 계산에서 제외됩니다.

Net-related Terminology

PCB 편집기에서는 다음 용어를 사용합니다.

- Net

– 서로 연결된 컴포넌트 핀(노드)들의 집합. 이러한 노드들이 서로 연결되는 방식의 배치를 토폴로지(topology)라고 하며, 기본 토폴로지는 shortest입니다.

- From-To

– 개념적으로 From-To는 하나의 넷에서 두 노드 사이를 연결합니다. From-To는 해당 넷의 토폴로지 또는 노드 배치를 따르도록 생성할 수 있습니다. 예를 들어 넷 토폴로지가 R1-1 → U1-5 → U3-2 → R5-2라면, 이 넷에는 R1-1 → U1-5, U1-5 → U3-2, U3-2 → R5-2의 세 개 From-To가 있을 수 있습니다. 토폴로지가 변경되면 가능한 From-To도 변경됩니다. From-To는 PCB panel의 From-To mode에서, 토폴로지를 기반으로 생성하려면 Generate 버튼을 클릭하거나, 넷에서 두 패드를 선택한 다음 Add From To 버튼을 클릭하여 생성합니다.

- xSignal

– 사용자가 정의한 노드 집합으로, 일반적으로 넷의 부분 집합(이 노드에서 저 노드까지)이거나, 종단 저항과 같은 직렬 컴포넌트를 포함하는 두 넷의 조합입니다.