プリント基板上の接続を配線(ルーティング)する作業は複雑で時間がかかります。 大規模または高密度の基板では、配線プロセスに設計者が相当な時間を要することがあり、オートルータがその支援になります。

Altium Designer の Situs™ オートルータは、トポロジー解析手法を用いて基板空間をマッピングします。これは幾何学的/形状ベースのマッピングとは異なり、障害物の形状や座標に依存しません。トポロジー・マッピングにより、配線経路の決定における柔軟性が高まり、配線方向の制約も少なくなります。

Situs という名称は Situs Analysis に由来します。これは、図形や立体の性質のうち、通常は大きさや形の変化の影響を受けない性質を研究する数学の一分野で、今日では一般にトポロジー(位相幾何学)として知られています。

基板のオートルーティング

Situs Topological Router は、オートルーティングの課題に対して新しいアプローチをもたらします。まず高度なトポロジー・マッピングで配線経路を定義し、その後、実績のあるさまざまな配線アルゴリズムを呼び出して、この「人間のような」経路を高品質な配線へ変換します。PCB Editor の統合機能として、PCB の電気的ルールおよび配線ルール定義に従います。

基板セットアップ

Situs は設定と実行が容易ですが、最適な配線結果を得るために注意すべき点があります。

部品配置

最終的に、部品配置が配線性能に最も大きな影響を与えます。Altium Designer の PCB Editor には、動的に最適化される接続ラインなど、部品配置を微調整できるツールが多数用意されています。最適な部品配置とは、接続ラインができるだけ短く、かつ「絡み」が最小になる状態です。

その他の良い設計プラクティスとしては、パッドが規則的なグリッド上に来るように部品を配置する(配線のためにパッド間の空きスペースを最大化する)、両面基板では同程度のサイズの表面実装部品を正確に表裏で向かい合わせに配置する、デカップリング配置のガイドラインについてデバイスメーカーのデータシートを参照する、などがあります。これは配置検討事項の完全な一覧ではなく、いくつかの提案に過ぎません。

キープアウト

ルータには、配置されたキープアウト・オブジェクトで構成される閉じた境界が必要です。通常、この境界は基板外形に沿います。配置オブジェクトは、適用されるクリアランス・ルールに従い、この境界から適切な距離を保つことで、設計が要求する機械的/電気的クリアランス要件を満たします。ルータは、この外周境界内のキープアウト、およびレイヤ固有のキープアウトにも従います。

Line/Arc Primitives from Board Shape dialog を使用して、基板形状のエッジに沿う閉じた境界を作成できます。キープアウトの詳細は Object Specific Keepouts を参照してください。

ポリゴン・プア

ポリゴン(銅)プアは、ソリッド(1つ以上の銅領域で塗りつぶし)またはハッチ(トラックとアークで構成)のいずれかにできます。中~大サイズのハッチ・ポリゴン・プアには多数のトラックとアークが含まれます。ルータはこのようなポリゴン・プアを含む基板でも配線できますが、導入されるオブジェクト数が非常に多いため、配線プロセスの複雑さが増します。

通常、配線前にポリゴン・プアを配置するのは、それが必要な場合に限るべきです。たとえば、異形のプレルーティング構造を作るため、あるいは商用電源の引き込み配線や重要なGND領域などに使用する場合です。それ以外では、配線完了後にポリゴン・プアを設計へ追加する方が望ましいです。

配線可能か?

オートルータは、人間が配線プロセスを理解してモデル化し、そのプロセスを自動的に再現しようとする試みです。手配線で配線できない領域が基板に含まれている場合、オートルーティングでも配線できません。ルータが特定の部品や基板の一部で繰り返し失敗する場合は、対話的に配線してみてください。配置やルール設定に問題があり、そもそも配線不可能になっている可能性があります。

プレルーティング

重要なネットは事前に配線し、配線プロセスで変更されては困る場合は、Situs Routing Strategies dialog の Lock All Pre-routes オプションを有効にしてロックしてください。ただし不要なロックは避けてください。ロックされたオブジェクトが多いと、配線問題がはるかに難しくなります。

差動ペアのネットは、オートルータを使用する前に手動で配線してロックする必要があります。これを行わないと、配線が変更され、差動ペアの信号品質(シグナルインテグリティ)が損なわれる可能性が非常に高くなります。

デザインルールの設定

default rule という用語は、クエリ・スコープが All のルールを表すために使用されます。

ルールに Minimum、Preferred、Maximum の値が含まれる場合、オートルータは Preferred 値を使用します。

使用している基板技術に対して、配線デザインルールが適切であることを確認してください。狙いが不十分、または不適切なデザインルールは、オートルーティング性能を大きく低下させる可能性があります。なお、ルータは Routing Corners ルールを除き、すべての Electrical および Routing デザインルールに従います。

ルールは PCB Rules and Constraints Editor dialog(Design » Rules)で定義します。これは Situs Routing Strategies dialog から直接アクセスできます。

ルールに Minimum、Preferred、Maximum の値が含まれる場合、オートルータは Preferred 値を使用します。

Altium Designer のルールシステムは階層構造です。基本的な考え方は、まずすべてのオブジェクトに対するデフォルトルールを用意し、その後、異なる要件を持つ他のオブジェクトを選択的に対象とする追加ルールを作成することです。たとえば、基板で最も一般的に使用する配線幅をカバーする配線幅のデフォルトルールを用意し、その後、特定のネットやネットクラスなどを選択的に対象とするルールを追加します。

ルールが正しいオブジェクトを対象にしているか確認するには、ルールの Query を PCB Filter panel にコピーし、Apply してください。ルールの対象となるオブジェクトだけがフィルタを通過し、強調表示されたままになります。別の方法として、PCB Rules And Violations panel を使用すると、現在の基板に定義された任意のルールについて、ルール適用状況を素早く確認できます。

最も重要なルールは Width と Clearance ルールです。これらの配線技術設定は、配線をどれだけ「詰めて」配置できるかを定義します。選定はトレードオフで、トラックが太くクリアランスが大きいほど基板製造は容易になりますが、トラックとクリアランスが細いほど配線は容易になります。配線幅とクリアランスについて、どの値を下回ると歩留まり低下や基板価格上昇につながるかという「価格の分岐点」を把握するため、製造業者に相談することを推奨します。設計の電気要件を満たすだけでなく、各ピンへ配線できるよう、部品技術に適した配線技術を選定する必要もあります。

配線技術の一部となる3つ目のルールは Routing Via Style です。使用するトラック幅とクリアランスに適合するように選定しつつ、選択した穴径とアニュラリング(ランド環)の製造コストも考慮してください。

過剰または不要なルールも避けてください。ルールが多いほど処理時間が増え、配線が遅くなります。オートルーティングに不要なルールは無効化できます。

配線幅

Query が All(デフォルトルール)である Width rule が存在し、Preferred 設定が必要とする最も一般的な配線幅に適していることを確認してください。また、この幅が適切なクリアランス・ルールと組み合わさったときに、すべてのパッドへ配線できることを確認してください。より太い/細い配線が必要なネットには、追加の配線幅ルールを設定します。

ファインピッチ部品に、より太い配線幅のネット(例:電源ネット)が接続されている場合は、電源ピンからの試験配線を行い、さらにその両隣のピンも配線して、物理的に配線可能であることを確認してください。

クリアランス制約

ファインピッチ部品など、パッド間隔が標準の基板クリアランスより狭いといった特別なクリアランス要件がないか確認してください。これは、適切にスコープ設定し優先度を付けたデザインルールで対応できます。なお、フットプリントを対象にするルールを定義しても、そのフットプリントに接続する配線自体は対象になりません。配線幅のセクションで述べたとおり、試験配線を行って部品ピンが配線可能であることを確認してください。

ビアスタイル(配線ビア)

Query が All の Routing Via Style rule が存在し、Preferred 設定が適切であることを確認してください。デフォルトルールとは異なるビアスタイルが必要なネットには、より高い優先度のルールを含めてください。

Altium Designer はブラインドビアおよびベリードビアをサポートしており、これらを使用するかどうかは Layer Stack Manager(Design » Layer Stack Manager)で定義される Via Types によって決まります。対話的配線と同様に、オートルータが2つのレイヤ間を切り替える際、現在の Via Type 定義を確認します。これらのレイヤがブラインド/ベリードのレイヤペアとして定義されている場合、配置されるビアはそれらのレイヤを開始/終了レイヤとして持ちます。ブラインド/ベリードビアの使用制約を理解することが重要です。これらは製造業者と相談の上でのみ使用すべきです。製造スタックアップ技術による制約に加え、信頼性やテストアクセス性の観点もあります。ブラインド/ベリードビアを使うより、配線レイヤ数を増やす方が良いと考える設計者もいます。

配線レイヤ

クエリが All の Routing Layers rule が存在することを確認してください。有効な信号レイヤ(レイヤスタックで定義)がすべて一覧表示されます。必要に応じて、配線を許可したいレイヤを有効にしてください。特定のレイヤのみに配線したいネットには、より高い優先度のルールを含めてください。

特定のネット(またはネットクラス)をオートルータで配線させたくない場合は、そのネット/ネットクラスを対象とする Routing Layer ルールを定義し、そのルールの Constraints 領域で、有効な各信号レイヤの Allow Routing オプションが無効になっていることを確認してください。ルールの優先度は、クエリが All のデフォルトルールより高くする必要があります。

レイヤ方向

推奨配線方向は Layer Directions ダイアログで指定します。このダイアログは Situs Routing Strategies dialog からアクセスします。レイヤースタックで定義されている有効な信号レイヤーがすべて一覧表示されます。

接続ラインの流れに合うように、各レイヤーの方向を適切に選択してください。Situs はトポロジカルマッピングを使用して配線パスを定義するため、水平・垂直のみに制約されません。一般的には、外層を水平と垂直にするのが最適です。ただし、多層基板で「2時方向」の角度の接続が多数ある場合は、内部レイヤーの1つ以上をその角度を推奨配線方向として設定してください。特に Layer Patterns パスはこの情報を活用するため、適切な方向を選ぶことで、時間と品質の両面で配線性能が大きく向上する可能性があります。なお、角度付きレイヤーを使用する場合、そのレイヤーに対して90度の相方レイヤーを用意する必要はありません。角度付きレイヤー上で障害物を回避する必要がある場合、ルータは通常、水平または垂直に配線するためです。

Any 方向の使用は避けてください。接続をどのレイヤーで配線するかは、接続がレイヤー方向にどれだけ整列しているかに基づいて決まるため、このレイヤーは「最後の手段」のレイヤーになってしまいます。Any 方向は通常、片面基板でのみ使用します。

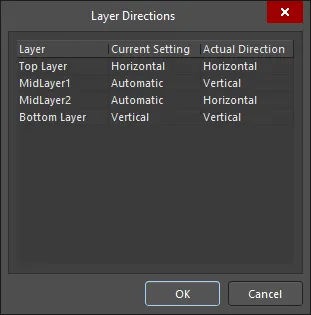

Layer Directions ダイアログ

Options and Controls of the Layer Directions Dialog

このダイアログには、レイヤースタックで定義された各信号レイヤーを一覧表示するグリッドが表示されます。各レイヤーは次の内容で示されます。

- Layer - 信号レイヤー名。

- Current Setting - 現在選択されている、そのレイヤーの推奨配線方向。このフィールドは編集可能です。ドロップダウンから次のオプションを選択します: Not Used、Horizontal、Vertical、Any、1 O'Clock、2 O'Clock、4 O'Clock、5 O'Clock、45 Up、45 Down、Fan Out、Automatic。

- Actual Direction - Situs が実際に使用している配線方向。このフィールドは読み取り専用です。通常は Current Setting フィールドで選択した推奨配線方向に従いますが、Automatic を選択した場合は、他レイヤーに定義された配線方向に基づいて使用すべき最適な方向を計算します。

配線優先度

Routing Priority rules を使用して、配線が難しいネット、または最もきれいな配線にしたいネットに高い優先度を設定します。

SMD ファンアウト制御

クエリシステムには、表面実装部品の各パッケージを特に対象とするキーワードが含まれており、IsLCC(Leadless Chip Carrier)、IsSOIC(Small Outline IC)、IsBGA(Ball Grid Array)などがあります。最も一般的なパッケージについてはデフォルトルールが自動作成され、またファンアウトパスはオートルーティング処理の早い段階で実行されるため、どの部品にも適用されないルールを残しておいても不利益はほとんどありません。基板上に表面実装部品がある場合は、少なくとも1つの SMD ファンアウト制御デザインルールを用意してください。すべての表面実装部品を対象とする単一ルールの適切なクエリは IsSMTComponent です。各クエリキーワードがどのように部品パッケージを識別するかについては、Query Helper を開き、必要なキーワードを入力して F1 を押してください。

ファンアウトルールには、パッドを内側にファンインするか外側にファンアウトするか、またはその混在にするかを制御する設定が含まれます。Fanout Control ルール属性の挙動に慣れるために、ネットが割り当てられていない任意の表面実装部品に対して Route » Fanout » Component コマンドを実行できます。これにより、基板で定義されている現在の配線テクノロジで部品がどの程度うまくファンアウトできるかを確認できるだけでなく、ライブラリに「事前ファンアウト済みフットプリント」として保持したい部品をファンアウトする用途にも使えます。PCB ワークスペースでファンアウトしたら、部品とファンアウト配線およびビアをコピー&ペーストしてライブラリに取り込みます。

ルール優先度

ルールの優先順位(プライオリティ)は設計者が定義します。ルール優先度は、1つのオブジェクトが複数のルールに該当する場合に、どのルールを適用するかを決定するために使用されます。優先度が正しく設定されていないと、ルールがまったく適用されないことがあります。

たとえば、InNet('VCC') というクエリのルールが、All というクエリのルールよりも優先度が低い場合、VCC ネットには All ルールが適用されます。PCB Rules and Constraints Editor dialog の Priorities ボタンを使用して Edit Rule Priorities dialog にアクセスし、必要に応じて優先度を調整してください。なお、2つのルールスコープが重ならない(同じオブジェクトを対象にしない)場合、優先度は重要ではありません。たとえば、InNet('VCC') と InNet('GND') のどちらのスコープが高優先度でも結果は変わりません。

黄金律

最も重要なステップは、オートルータを開始する前にデザインルールチェック(DRC)を実行することです。Route » Auto Route » Setup または Route » Auto Route » All コマンドを使用すると、Situs は独自の事前配線解析を行い、その結果を Situs Routing Strategies dialog にレポートとして表示します。ダイアログから設計のレポートを確認し、配線に使用するストラテジを選択できます。配線ストラテジはルータの「知能」に相当し、トポロジマップで特定された「仮想」配線パスを、基板上の高品質かつ高効率な実配線へ変換するために、どの配線アルゴリズムをいつ使用するかを定義します。

オートルータを開始する前に、Routing Setup Report がクリーンであることを確認してください。

オートルータを開始する前に、Routing Setup Report がクリーンであることを確認してください。

レポートには次のような情報が含まれます。

- オートルータが遵守する、設計で現在定義されているデザインルール(および各ルールの影響を受ける設計オブジェクト数(ネット、部品、パッド))

- すべての信号配線レイヤーに定義された配線方向

- ドリルレイヤーペア定義

また、ルータ性能に影響し得る潜在的な問題も一覧表示されます。可能な場合は、オートルーティングに向けた設計準備をより良くするためのヒントも提示されます。表示されたエラー/警告/ヒントは精査し、必要に応じて該当する配線ルールを調整してから、配線を進めてください。

すべてのエラー、警告、ヒントを確認し、オートルータが直面する潜在的な問題を理解してください。

すべてのエラー、警告、ヒントを確認し、オートルータが直面する潜在的な問題を理解してください。

配線に関連するルール違反は、オートルータ開始前に必ず解消する必要があります。違反はその箇所での配線を妨げるだけでなく、ルータが配線不能領域を繰り返し配線しようとして大幅に遅くなる原因にもなります。

Situs AutoRouter 実行時の注意点

配線パスと配線ストラテジーの概要

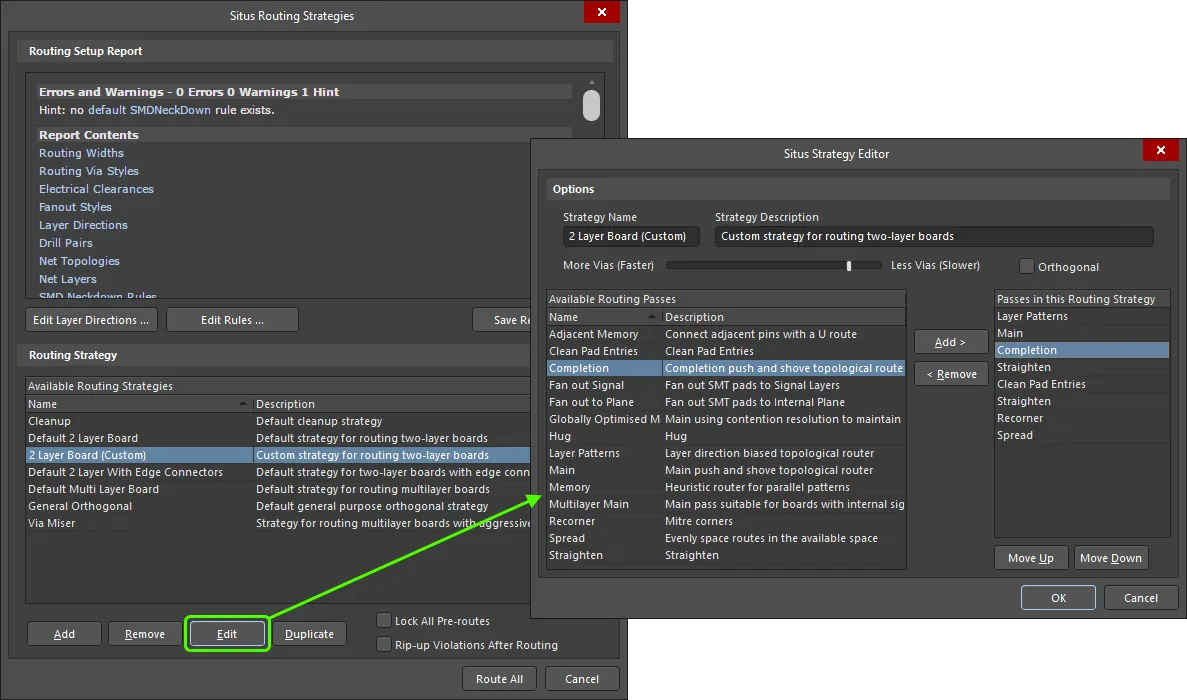

現在定義されている配線ストラテジーは、Situs Routing Strategies ダイアログの下部領域に一覧表示されます。Add ボタンをクリックして Situs Strategy Editor ダイアログにアクセスすると、新しいストラテジーに含めるパスを指定できます。あるいは、Duplicate ボタンを使用して既存のストラテジーを複製し、必要に応じて編集します。さまざまな配線パスの組み込みと、その使用順序がオートルーターの「知能」を構成します。これらのパスは、トポロジカルマップで特定された仮想配線パスを、ボード上の高品質な配線へと変換するために使用されます。

定義済みの配線ストラテジーと、その中に含まれる構成要素である配線パスは、ボード全体を配線する場合にのみ適用されます。

複製したストラテジーを編集する例。

Options and Controls of the Situs Routing Strategies Dialog

ダイアログのコントロールは2つの主要領域に分かれています。2つのアクセス方法の間でコントロールの違いは、ダイアログ下部の Cancel ボタンの左側にあるボタンだけです。設定のみ(配線はしない)を行うためにアクセスした場合、ここは標準の OK ボタンとして表示されます。これをクリックすると、ユーザー定義の配線ストラテジーへの変更が保存されます。ボード全体を配線するためにアクセスした場合は、Route All ボタンとして表示されます。これをクリックすると、現在選択されている配線ストラテジーに従ってボードの配線が試行されます。

Routing Setup Report

- Report Window - この領域には、配線前解析に基づくレポートが表示されます。ここでは、オートルーターが遵守する(そして各ルールの影響を受けるデザインオブジェクト数(ネット、コンポーネント、パッド)を含む)現在定義されているデザインルール、すべての信号配線レイヤーに定義された配線方向、ドリルレイヤーペア定義などの情報がまとめられます。

このレポートには、ルーターの性能に影響し得る潜在的な問題が列挙されます。これらの警告には、配線方向が Any に設定されている配線レイヤーが含まれる場合があります。可能な場合は、自動配線に向けて設計をより適切に準備するためのヒントが提示されます。リストされたエラー/警告/ヒントは精査し、必要に応じて、設計の配線を進める前に対応する配線ルールを調整してください。

オートルーターを開始する前に、配線関連のルール違反をすべて解消しておくことが不可欠です。違反はその箇所での配線を妨げるだけでなく、配線不可能な領域を配線しようと繰り返し試みることで、オートルーターを大幅に低速化させる可能性があります。

レポート内のハイパーリンク項目を使用すると、特定のルール定義に対する Edit PCB Rule ダイアログへ素早くアクセスでき、必要に応じてそのルールの適用範囲や制約を調整できます。配線不可能なパッドについては、レポート内の該当ハイパーリンク項目をクリックすると、問題のパッドがデザインスペースでズームされ、中央に表示されます。

- Edit Layer Directions - このボタンをクリックすると Layer Directions dialog にアクセスでき、必要に応じて信号レイヤーの配線方向を変更できます。

- Edit Rules - このボタンをクリックするとメインの PCB Rules and Constraints Editor dialog にアクセスできます。あるいは、既存の配線ルールを直接変更したい場合は、レポート本文内の該当ルールのハイパーリンクをクリックします。

- Save Report As - このボタンをクリックすると、レポートをHTMLドキュメントとして保存できます。標準の Save As ダイアログが表示されます。デフォルトでは、レポートはPCB設計ファイル(DesignName.htm)と同じ場所に、同じ名前で保存されます。必要に応じて、ダイアログで名前と保存場所を変更してください。

Routing Strategy

- Available Routing Strategies - この領域には、オートルーターが設計を配線するために使用できる、現在利用可能な配線ストラテジーがすべて一覧表示されます。各ストラテジーは、名前と説明で示されます。次の6つの配線ストラテジーが定義されており、デフォルトで利用可能です:

- Cleanup - デフォルトのクリーンアップストラテジー。

- Default 2 Layer Board - 2層ボード配線用のデフォルトストラテジー。

- Default 2 Layer With Edge Connectors - エッジコネクタ付き2層ボード配線用のデフォルトストラテジー。

- Default Multi Layer Board - 多層ボード配線用のデフォルトストラテジー。

- General Orthogonal - デフォルトの汎用直交ストラテジー。

- Via Miser - ビア最小化を積極的に行う多層ボード配線用のデフォルトストラテジー。

一般に、2層および多層ボード向けのデフォルト配線ストラテジーは、ほとんどの配線状況で十分に機能します。ただし、オートルーターを実行する前に、関連する配線デザインルールが設定されていることを確認することが重要です。

- Add - このボタンをクリックすると、新しいユーザー定義の配線ストラテジーを一覧に追加できます。Situs Strategy Editor ダイアログが開き、特に重要な構成要素である配線パスを含め、ストラテジーを完全に定義できます。

- Remove - このボタンをクリックすると、現在選択されているユーザー定義の配線ストラテジーを、利用可能な配線ストラテジーの一覧から削除できます。

6つのデフォルト配線ストラテジーは削除できません。

- Edit - このボタンをクリックすると、現在選択されているユーザー定義の配線ストラテジーを編集できます。Situs Strategy Editor ダイアログが開き、必要に応じて構成要素である配線パスを含め、ストラテジーに変更を加えられます。

6つのデフォルト配線ストラテジーは編集できません。

- Duplicate - このボタンをクリックすると、現在選択されている配線ストラテジーの複製を作成できます。Situs Strategy Editor ダイアログが開きます。新しいストラテジーに、より意味のある名前と説明を付け、必要に応じて設定を変更してください。

- Lock All Pre-routes - このオプションを有効にすると、事前配線済みのネットがオートルーターによって削除(「リップアップ」)され、再配線されるのを防ぎます。多くの場合、特定のネットは手動で配線し、残りを自動配線します。

- Rip-up Violations After Routing - このオプションを有効にすると、オートルーターが配線セッションを完了した後、定義済み(かつ適用対象)のデザインルールに違反する配線がリップアップされます。

Options and Controls of the Situs Strategy Editor Dialog

Options

- Strategy Name - ストラテジーの現在の名前です。新しい配線ストラテジーを作成する場合、このフィールドにはデフォルトのエントリ New Strategy が入ります。必要に応じて、このフィールドを編集してより意味のある名前を付けてください。

- Strategy Description - ストラテジーの現在の説明です。ストラテジーの目的または適用範囲を要約する、意味のある説明を入力してください。

- More/Less Vias- このスライダーバーを使用して、オートルータが許可されるビア使用量を定義します。これは、配線速度の向上とビア数の削減のトレードオフです。バーを右に動かすと、オートルータが配置するビア数が少なくなるよう制約されますが、基板の配線に要する時間は長くなります。バーを左に動かすと、配線完了までの時間は短くなりますが、その代償としてオートルータがPCB上に追加のビアを配置します。

- Orthogonal - このオプションを有効にすると、オートルータを直交(90°)経路のみに制約します。このオプションを無効にすると、オートルータは必要に応じて直交または非直交(45°)で配線できます。

Routing Passes

- Available Routing Passes - この領域には、配線ストラテジで使用できる利用可能なルーティングパス(アルゴリズム)が一覧表示されます。以下のパスが利用可能です。

- Adjacent Memory - これは接続レベルのルーティングパスです。単純なU字パターンで、ファンアウトが必要な隣接する同一ネットのピンを配線するために使用します。

- Clean Pad Entries - これは接続レベルのルーティングパスです。各パッド中心から、パッドの長軸方向に沿って引き出すように再配線します。

X寸法とY寸法が異なるパッドを持つコンポーネントを含む設計では、Memory pass の後に必ず Clean Pad Entries pass を含めてください。

- Completion - これは接続レベルのルーティングパスです。基本的には Main pass と同じですが、競合を解消して難しい接続を完了させるために、コスト付けが異なります。コスト付けの違いの例としては、ビアがより安価、逆方向の配線がより高価になる、などがあります。

- Fan out Signal - これはコンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮した上で、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先は信号層のみです。

- Fan out to Plane - これはコンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮した上で、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先は内部プレーン層のみです。

- Globally Optimised Main - これは接続レベルのルーティングパスです。最適な配線を提供します。最初の反復では競合/違反を無視します。その後、競合コストを増加させながら接続を再配線し、違反がなくなるまで繰り返します。このパスは、Orthogonal option を有効にした状態で併用すると、見栄えの良い配線パターンを生成できます。コーナーをマイター処理するには、ストラテジに Recorner pass を追加してください。

- Hug - これは接続レベルのルーティングパスで、既存配線に可能な限り最小のクリアランスで追従するように、各接続を再配線します。Hug パスは、自由な配線スペースを最大化するために使用します。なお、このパスは非常に遅いです。

- Layer Patterns - これは接続レベルのルーティングパスです。層方向(許容範囲内)に一致する接続のみを配線します。自由スペースを最大化するため、既存配線に密着(hug)または追従するようにコスト付けされています。

- Main - これは接続レベルのルーティングパスです。トポロジカルマップを使用して配線経路を見つけ、その後 push and shove ルータを使用して提案経路を実際の配線に変換します。

- Memory - これは接続レベルのルーティングパスです。同一層上で、異なるコンポーネント上の2つのピンがXまたはY座標を共有しているかをチェックします。

- Multilayer Main - これは接続レベルのルーティングパスです。Main pass に似ていますが、多層基板向けにコストが最適化されています。

- Recorner - これは接続レベルのルーティングパスで、配線コーナーのマイター処理を行うために使用します。このパスは、ストラテジで Orthogonal option が有効な場合に使用されます。つまり、その設定を実質的に上書きし、各配線のコーナーをマイター処理します。使用中のストラテジで Orthogonal option が無効の場合、オートルータはデフォルトでコーナーをマイター処理するため、Recorner pass を含める必要はありません。

- Spread - これは接続レベルのルーティングパスで、自由スペースを活用するように配線を広げ、固定物(コンポーネントパッドなど)の間を通過する際に配線間隔が均等になるように、各接続を再配線します。なお、このパスは非常に遅いです。

- Straighten - これは接続レベルのルーティングパスで、コーナー数の削減を試みます。ルートに沿ってコーナーまで辿り、そのコーナーから(水平/垂直/45up/45down)のプローブを行い、同一ネット上の別の配線点を探索します。見つかった場合、その新しい経路が配線長を短縮するかをチェックします。

配線ストラテジには、メインタイプのパスは1つだけ指定してください。Main、Multilayer Main または Globally Optimized Main のいずれかです。

- Passes in this Routing Strategy - この領域には、ストラテジに含まれる実際のルーティングパス(アルゴリズム)が一覧表示されます。利用可能なパスのリストから任意のパスを追加でき、同じパスを複数回、ストラテジ全体の中に追加して特定の結果を得ることもできます。パスは上から下の順に実行されます。この順序は Move Up および Move Down ボタンで変更できます。

- Add - このボタンをクリックすると、Available Routing Passes リストで現在選択されているパスを Passes in this Routing Strategy リストに追加します。パスは後者のリストで現在選択されているパスの上に追加されます。

- Remove - このボタンをクリックすると、Passes in this Routing Strategy リストで現在選択されているパスをストラテジから削除します。

- Move Up - このボタンをクリックすると、Passes in this Routing Strategy リストで現在選択されているパスをリスト内で上へ移動します。つまり、配線ストラテジの中でより早い段階で使用されます。

- Move Down - このボタンをクリックすると、Passes in this Routing Strategy リストで現在選択されているパスをリスト内で下へ移動します。つまり、配線ストラテジの中でより後の段階で使用されます。

ユーザー定義ストラテジはいつでも編集できますが、デフォルトストラテジ(Cleanup、Default 2 Layer Board、Default 2 Layer With Edge Connectors、Default Multi Layer Board、General Orthogonal、Via Miser)は変更できません。

以下のルーティングパスが利用可能です。パスは任意の順序で使用できます。目安として、既存のストラテジを確認してパスの順序を参照してください。

| PAss |

Function |

| Adjacent Memory |

接続レベルのルーティングパスです。単純なU字パターンで、ファンアウトが必要な隣接する同一ネットのピンを配線するために使用します。 |

| Clean Pad Entries |

接続レベルのルーティングパスです。各パッド中心から、パッドの長軸方向に沿って引き出すように再配線します。X寸法とY寸法が異なるパッドを持つコンポーネントがある場合は、Memory パスの後に必ず Clean Pad Entries パスを含めてください。 |

| Completion |

接続レベルのルーティングパスです。基本的には Main パスと同じですが、競合を解消して難しい接続を完了させるために、コスト付けが異なります。コスト付けの違いの例としては、ビアがより安価、逆方向の配線がより高価になる、などがあります。 |

| Fan Out Signal |

コンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮した上で、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先は信号層のみです。 |

| Fan out to Plane |

コンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮した上で、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先は内部プレーン層のみです。 |

| Globally Optimized Main |

接続レベルのルーティングパスです。最適な配線を提供します。最初の反復では競合/違反を無視します。その後、競合コストを増加させながら接続を再配線し、違反がなくなるまで繰り返します。このパスは、Orthogonal オプションを有効にした状態で併用すると、見栄えの良い配線パターンを生成できます。コーナーをマイター処理するには、ストラテジに Recorner パスを追加してください。 |

| Hug |

接続レベルのルーティングパスで、既存配線に可能な限り最小のクリアランスで追従するように、各接続を再配線します。Hug パスは、自由な配線スペースを最大化するために使用します。なお、このパスは非常に遅いです。 |

| Layer Patterns |

接続レベルのルーティングパスです。層方向(許容範囲内)に一致する接続のみを配線します。自由スペースを最大化するため、既存配線に密着(hug)または追従するようにコスト付けされています。 |

| Main |

接続レベルのルーティングパスです。トポロジカルマップを使用して配線経路を見つけ、その後 push and shove ルータを使用して提案経路を実際の配線に変換します。配線ストラテジには、メインタイプのパスは1つだけ指定してください。Main、Multilayer Main、または Globally Optimized Main のいずれかです。 |

| Memory |

接続レベルのルーティングパスです。同一層上で、異なるコンポーネント上の2つのピンがXまたはY座標を共有しているかをチェックします。 |

| Multilayer Main |

接続レベルのルーティングパスです。Main パスに似ていますが、多層基板向けにコストが最適化されています。 |

| Recorner |

接続レベルのルーティングパスで、配線コーナーのマイター処理を行うために使用します。このパスは、ストラテジで Orthogonal オプションが有効な場合に使用されます。つまり、その設定を実質的に上書きし、各配線のコーナーをマイター処理します。使用中のストラテジで Orthogonal オプションが無効の場合、オートルータはデフォルトでコーナーをマイター処理するため、Recorner パスを含める必要はありません。 |

| Spread |

接続レベルのルーティングパスで、自由スペースを活用するように配線を広げ、固定物(コンポーネントパッドなど)の間を通過する際に配線間隔が均等になるように、各接続を再配線します。なお、このパスは非常に遅いです。 |

| Straighten |

コーナー数を減らすことを目的とした、接続レベルの配線ルーティング・パスです。配線に沿ってコーナーまでたどり、そのコーナーから(水平方向/垂直方向/45度上/45度下)のプローブを実行して、同一ネット上の別の配線済みポイントを探索します。見つかった場合、その新しい経路によって配線長が短くなるかどうかを確認します。 |

See Also