このルールは、使用されているビアタイプが現在定義されているビアタイプと一致していることを確認します。使用されているビアタイプは、基板内のビアとパッドから決定されます。許可されるビアタイプは、レイヤースタックマネージャーのVia Typesタブで定義されます。

デフォルトルール:必要 i

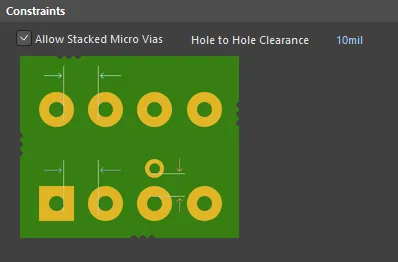

このルールは、ドリルされた穴の製造互換性をチェックします。有効にすると、同じ位置にある複数のビア/パッド、または重なっているパッド/ビアの穴をフラグします。また、スタックされたマイクロビアが許可されているかどうかを決定するオプションもあります。

制約

穴と穴のクリアランスルールのデフォルト制約

ルール適用

オンラインDRCおよびバッチDRC。

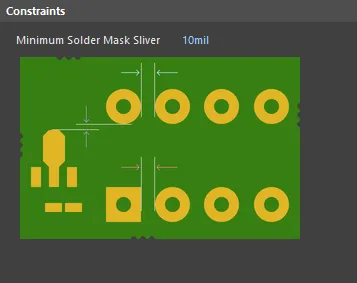

最小はんだマスクスリバー

デフォルトルール:必要i

このルールは、後の段階で製造上の問題を引き起こす可能性のあるはんだマスクの狭い部分を特定するのに役立ちます。基板全体にわたってはんだマスクの最小幅があることを確認し、はんだマスク層に存在するパッド、ビア、およびプリミティブ間の距離が、ユーザー指定の最小値以上であることをチェックします。これは、トップとボトムの両面を独立してチェックします。

制約

最小はんだマスクスリバールールのデフォルト制約

Minimum Solder Mask Sliver - はんだマスクの最小許容幅を指定します。

ルール適用

オンラインDRCおよびバッチDRC。

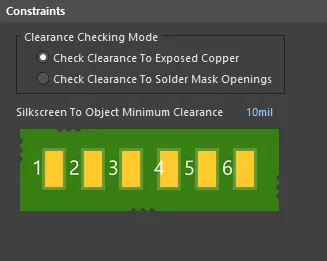

シルクからはんだマスクまでのクリアランス

デフォルトルール:必要i

このルールは、シルクスクリーンのプリミティブとはんだマスクのプリミティブ、またははんだマスクの開口部を通して露出した銅層のプリミティブとの間のクリアランスをチェックします。制約で指定された値以上であることを確認します。

多くのメーカーは、銅パッドだけでなくマスク開口部に沿ってシルクスクリーンを剥がす(または「クリップ」する)ことが一般的です。しかし、これによりシルクスクリーンのテキストが読めなくなる可能性があります。DRCを通じてこのような発生を捉えることができれば、基板を製造に送る前に問題のあるシルクスクリーンテキストを操作できます。

この設計ルールは、Altium Designer 13.0以前のリリースで見つかったSilkscreen Over Component Padsルールに代わるものです。このような以前のリリースからPCBドキュメントをロードするとき、定義されたSilkscreen Over Component Padsルールは自動的にSilk To Solder Mask Clearanceルールに変換され、そのスコープと制約がレガシー動作に合わせて設定されます。設計要件に関連してルールスコープと関連する制約の正確性を確認することをお勧めします。

制約

Silk To Solder Mask Clearanceルールのデフォルト制約

Altium Designer 13.0以前のソフトウェアのリリースで見つかった古いSilkscreen Over Component Padsルールのレガシー動作に合わせるために、Silk To Solder Mask ClearanceルールはClearance Checking ModeをCheck Clearance To Exposed Copperに設定し、そのルールスコープの完全なクエリをIsPadに設定する必要があります。前述のように、これは古いデザインを開くときに自動的に処理されます。

ルール適用

オンラインDRCおよびバッチDRC。

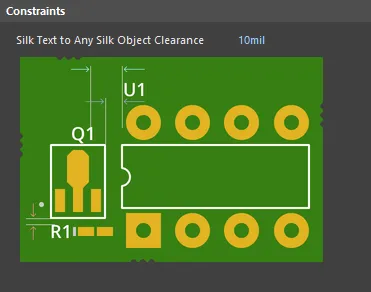

シルクからシルクへのクリアランス

デフォルトルール:必要i

このルールは、シルクスクリーン層上のテキストと他のオブジェクト間に許可される最小クリアランスを定義します。

制約

シルクからシルクへのクリアランスルールのデフォルト制約

Silk Text to Any Silk Object Clearance - 2つのシルクスクリーンオブジェクト間の最小許容クリアランスを指定します。

ルール適用

オンラインDRCおよびバッチDRC。

ネットアンテナ

デフォルトルール:必要i

このルールは、設計のネットレベルで動作し、開放端のトラック/アークプリミティブ、またはビアで終端された開放端のトラック/アークがアンテナを形成している場合にフラグを立てます。

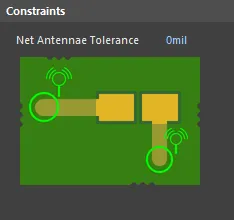

制約

ネットアンテナルールのデフォルト制約

Net Antennae Tolerance - 開放端のトラック/アークプリミティブ(またはビアで終端するもの)のスタブの最大許容長さ。

ルール適用

オンラインDRCおよびバッチDRC。

基板アウトラインクリアランス

デフォルトルール:不要

このルールは、製造される設計オブジェクトが基板の端から許可される最小クリアランスを定義します。単一のクリアランス値をすべてのオブジェクト対エッジの可能性に対して指定するか、専用の最小クリアランスマトリックスを使用して異なるペアリングに対して異なるクリアランスを定義できます。基板アウトラインと基板エッジという用語は、基板の外側のエッジを説明するために一般的に交換可能に使用されます。表の下に定義されているエッジという用語は、電気およびオーバーレイ(シルクスクリーン)層のオブジェクト対エッジのクリアランスをチェックする基板アウトラインクリアランス設計ルールで使用されます。

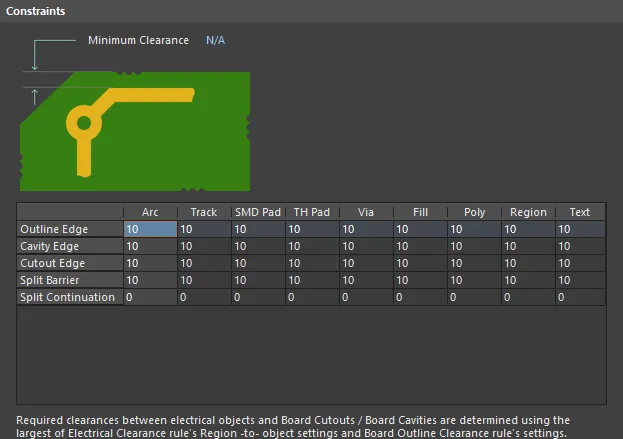

制約

基板アウトラインクリアランスルールのデフォルト制約

| エッジタイプ |

定義 |

| アウトラインエッジ |

基板の最も外側(外部)のエッジ |

| キャビティエッジ |

ユーザー定義のキャビティのエッジ |

| カットアウトエッジ |

ユーザー定義のカットアウトのエッジ |

| スプリットバリア |

この層でスプリットラインが基板のエッジを定義する場合、このエッジはスプリットラインバリアとして参照されます |

| スプリット継続 |

この層がスプリットラインを越えて続く場合、このエッジはスプリットライン継続(透過境界)として参照されます。オブジェクトの種類がスプリット継続を越えることを許可するには、クリアランス値をゼロに設定します。ゼロは、これらのオブジェクトの種類にとってこれが継続層であり、オブジェクトがスプリットラインを侵害(越える)ことが許可されていることを示します。たとえば、ルーテッドトラックが1つのレイヤースタックリージョンから別のリージョンに渡ることを許可するためにこの技術を使用します。 |

-

Minimum Clearance - 必要な最小クリアランスの値です。ここに入力された値は、最小クリアランスマトリックスのすべてのセルに複製されます。逆に、マトリックス内の1つ以上のオブジェクトペアリングに異なるクリアランス値が入力されると、Minimum Clearance制約はN/Aに変更され、単一のクリアランス値が全体に適用されていないことを反映します。

-

Minimum Clearance Matrix - 設計内のさまざまなオブジェクトとエッジのクリアランスの組み合わせ間のクリアランスを微調整する機能を提供します。

新しいPCBドキュメントのデフォルトのボードアウトラインクリアランスルールは、すべてのオブジェクトとエッジのクリアランスの組み合わせに対して10milを使用するように設定されます。新しいルールを作成すると、マトリックスは最低優先度のボードアウトラインクリアランスルールで現在定義されている値で埋められます。

オブジェクトの種類をエッジを越えて許可するには、クリアランス値をゼロに設定します。ゼロは、ソフトウェアに対して、オブジェクトの種類がこのエッジタイプを越える(通過する)ことを許可することを示します。この技術を使用して、例えば、配線されたトラックが一つのレイヤースタック領域から別の領域へ移動することを許可します。

クリアランスマトリックスの操作

マトリックス内でのクリアランス値の定義は、次の方法で実行できます:

-

単一セル編集 - 特定のオブジェクトペアリングの最小クリアランスを変更します。

-

複数セル編集 - 複数のオブジェクトペアリングの最小クリアランスを変更します:

-

列内の複数セルを選択するには、Ctrl+Click、Shift+Click、およびClick+Dragを使用します。

-

行内の連続する複数セルを選択するには、Shift+Click、およびClick+Dragを使用します。

-

複数の行と列にわたる連続する複数セルを選択するには、Click+Dragを使用します。

-

行ヘッダーをクリックすると、その行のすべてのセルをすばやく選択できます。

-

列ヘッダーをクリックすると、その列のすべてのセルをすばやく選択できます。

必要な選択を行った後(単一セルまたは複数セル)、現在の値を変更するのは、必要な新しい値を入力するだけです。新しく入力された値を送信するには、別のセルをクリックするか、Enterを押します。選択されたすべてのセルは、新しい値で更新されます。

すべての可能なオブジェクトペアリングに対して単一のクリアランス値を設定するには、Minimum Clearance制約に必要な値を設定します。Enterをクリックすると、この値はマトリックスのすべての適用可能なセルに複製されます。または、マトリックスの左上にある空白の灰色セルをクリックするか、Ctrl+Aショートカットを使用します。これにより、マトリックス内のすべてのセルが選択され、新しく入力された値を受け入れる準備が整います。

ルールの適用

オンラインDRC、バッチDRC、インタラクティブ配線、およびオート配線。