Типы производственных правил

Ниже описаны правила проектирования категории Manufacturing.

Категория Manufacturing правил проектирования.

Минимальное кольцо металлизации

Правило по умолчанию: не требуется

Это правило задаёт минимально допустимое кольцо металлизации (annular ring), требуемое для площадки (pad) или переходного отверстия (via). Кольцо металлизации измеряется по радиусу — от края отверстия площадки/переходного отверстия до края самой площадки/переходного отверстия (также называемого land perimeter).

Ограничения

Ограничения по умолчанию для правила «Минимальное кольцо металлизации»

Minimum Annular Ring (x-y) - минимальное значение кольца металлизации вокруг площадок/via, на которые нацелено правило.

Применение правила

Online DRC и Batch DRC.

Примечания

- Разные производители плат, безусловно, используют различные технологии и оборудование. Производства среднего уровня могут предлагать нормы, допускающие минимальное кольцо металлизации 10 mil. Высокотехнологичные производства могут снизить это значение до 5 mil. Если отверстия в площадках и via выполняются лазерным сверлением, а не механическим, то минимально допустимое кольцо металлизации может быть уменьшено ещё больше.

- Класс платы, которую вы проектируете, также влияет на требуемое значение минимального кольца металлизации. Например, если ваш проект соответствует стандарту IPC Class 3 (высоконадежная электроника), то требуемое минимальное кольцо металлизации составляет 2 mil.

- Если вам всё же нужно уменьшить кольцо металлизации ниже принятого стандарта конкретного производства, постарайтесь ограничить использование таких площадок и via. Чем больше на плате площадок и via с такими параметрами кольца металлизации, тем выше вероятность брака платы в процессе изготовления.

- Отсутствие кольца металлизации, помимо прочего, приведёт к плохим паяным соединениям, поскольку не будет меди, на которую мог бы растекаться припой после выхода из металлизированного отверстия площадки/via.

- Стандарты определяют минимальное значение кольца металлизации, но эти значения можно уменьшать. Причина, по которой они заданы именно на таких уровнях, — защита от «выхода сверла» (drill breakout). Это явление довольно распространено при малых значениях кольца металлизации. Drill breakout возникает из‑за неблагоприятного сочетания нескольких производственных параметров (например, позиционирование отверстия, размер отверстия, расширение фотошаблона), в результате чего отверстие сверлится так, что прорезает соединяющую медную дорожку(и).

- Возможен контролируемый drill breakout без ухудшения характеристик платы. Один из способов — применять «слёзки» (teardrops) к нужным площадкам и via. Teardropping (также известный как filleting или tapering) — это процесс добавления дополнительной площади меди к площадке/via в месте соединения с дорожкой(ами). Эта дополнительная область защищает соединение «площадка‑дорожка» (или «via‑дорожка») в случае выхода сверла.

-

Нарушения правила «Минимальное кольцо металлизации» обнаруживаются для площадок и via с соединениями на слоях, на которых формы площадки/via меньше, чем отверстие площадки/via (например, если формы площадки/via были настроены вручную в панели Properties или удалены с помощью инструмента Remove Unused Pad Shapes).

Острый угол

Правило по умолчанию: не требуется

Это правило задаёт минимально допустимый угол между любыми объектами в одной и той же цепи (net). Правило «Острый угол» работает только с цепями. Оно находит все острые углы, образованные любыми объектами в одной цепи. По сути, правило формирует контур из всех примитивов цепи (на одном и том же слое), а затем анализирует этот контур на наличие точек, которые могут образовать угол меньше заданного предельного значения.

Ограничения

Ограничения по умолчанию для правила «Острый угол»

- Minimum Angle - задаёт минимально допустимый угол, образованный между объектами в одной цепи.

- Check Tracks Only - включите эту опцию, чтобы заставить DRC проверять острые углы только для объектов дорожек (track).

Применение правила

Online DRC и Batch DRC.

Размер отверстия

Правило по умолчанию: требуется

Это правило задаёт максимальный и минимальный размер отверстий для площадок и via в проекте. Размер отверстия — это диаметр отверстия, которое будет просверлено в площадке/via при изготовлении.

Ограничения

Ограничения по умолчанию для правила «Размер отверстия»

-

Measurement Method - задаёт метод, используемый для определения минимального/максимального размеров отверстий:

- Absolute - значения минимального/максимального размеров отверстий будут абсолютными.

- Percent - минимальный/максимальный размеры отверстий будут выражены в процентах от размера площадки/via.

- Minimum - значение минимального размера отверстия для площадок и via в проекте. Значение будет отображаться как абсолютное (по умолчанию = 1mil) или как процент от размера площадки/via (по умолчанию = 20%) — в зависимости от выбранного метода измерения.

- Maximum - значение максимального размера отверстия для площадок и via в проекте. Значение будет отображаться как абсолютное (по умолчанию = 100mil) или как процент от размера площадки/via (по умолчанию = 80%) — в зависимости от выбранного метода измерения.

Применение правила

Online DRC и Batch DRC.

Пары слоёв

Правило по умолчанию: требуется

Это правило проверяет, что используемые типы via соответствуют текущим определённым типам via. Используемые типы via определяются по via и площадкам, найденным на плате. Допустимые типы via задаются на вкладке Via Types в Layer Stack Manager.

Ограничения

Ограничение по умолчанию для правила «Пары слоёв»

Enforce layer pairs settings – задаёт, выполняется ли проверка.

Применение правила

Online DRC, Batch DRC и во время интерактивной трассировки.

Зазор «отверстие‑отверстие»

Правило по умолчанию: требуется

Это правило обеспечивает проверку технологической совместимости просверленных отверстий. Если включено, оно помечает любые множественные via/площадки в одной и той же точке, либо перекрывающиеся отверстия площадок/via. Также есть опция, определяющая, разрешены ли «стековые» micro via (stacked micro vias).

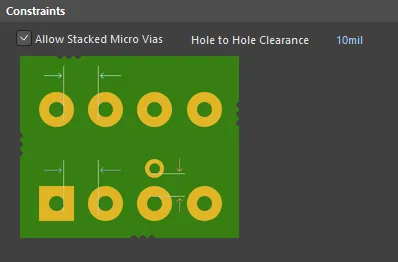

Ограничения

Ограничения по умолчанию для правила «Зазор отверстие‑отверстие»

-

Allow Stacked Micro Vias - включите эту опцию, чтобы разрешить стекование micro via .

- Hole To Hole Clearance - значение минимально допустимого зазора между отверстиями площадок/via в проекте.

Применение правила

Online DRC и Batch DRC.

Минимальная перемычка паяльной маски

Правило по умолчанию: требуется

Это правило помогает выявлять узкие участки паяльной маски, которые могут вызвать производственные проблемы на более позднем этапе. Обеспечивая минимальную ширину паяльной маски по всей плате, правило проверяет, что расстояние между любыми двумя окнами паяльной маски равно или больше заданного пользователем минимального значения. Это включает площадки, via и любые примитивы, расположенные на слоях паяльной маски. Также отдельно проверяются верхняя и нижняя стороны.

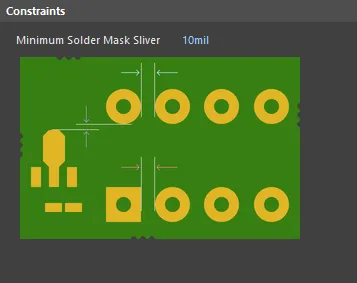

Ограничения

Ограничение по умолчанию для правила «Минимальная перемычка паяльной маски»

Minimum Solder Mask Sliver - задаёт минимально допустимую ширину паяльной маски.

Применение правила

Online DRC и Batch DRC.

Зазор «шелкография‑паяльная маска»

Правило по умолчанию: требуется

Это правило проверяет зазор между любым примитивом шелкографии и любым примитивом паяльной маски либо примитивом на медном слое, который открыт (экспонирован) через окна в паяльной маске. Проверка гарантирует, что расстояние равно или больше значения, заданного в ограничении.

Многие производители обычно «срезают» (strip/clip) шелкографию по окну маски, а не только по медной площадке. Однако это может сделать текст шелкографии нечитаемым. Возможность отлавливать такие случаи через DRC позволяет вам скорректировать проблемный текст шелкографии до отправки платы в производство.

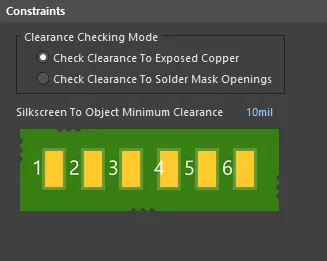

Ограничения

Ограничения по умолчанию для правила «Зазор шелкография‑паяльная маска»

-

Clearance Checking Mode - выберите режим проверки зазора:

- Check Clearance To Exposed Copper - в этом режиме проверка зазора выполняется между объектами шелкографии (слой Top/Bottom Overlay) и медью в площадках компонентов, которая открыта через окна в паяльной маске.

- Check Clearance To Solder Mask Openings- в этом режиме проверка зазоров выполняется между объектами шелкографии (слой Top/Bottom Overlay) и окнами паяльной маски, создаваемыми объектами, которые включают паяльную маску, такими как площадки, переходные отверстия или медные объекты с включённой опцией Solder Mask Expansion.

- Silkscreen To Object Minimum Clearance - задаёт минимально допустимый зазор между объектом шелкографии и либо открытой медью, либо окнами паяльной маски — в зависимости от выбранного режима проверки зазоров.

Применение правила

Online DRC и Batch DRC.

Silk To Silk Clearance

Правило по умолчанию: требуется

Это правило задаёт минимально допустимый зазор между текстом и другими объектами на слое шелкографии.

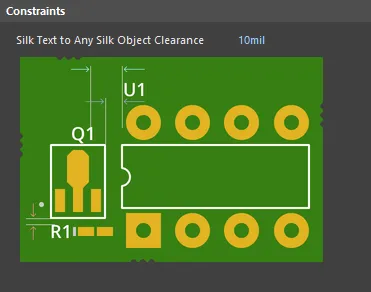

Ограничения

Ограничение по умолчанию для правила Silk To Silk Clearance

Silk Text to Any Silk Object Clearance - задаёт минимально допустимый зазор между любыми двумя объектами шелкографии.

Применение правила

Online DRC и Batch DRC.

Net Antennae

Правило по умолчанию: требуется

Это правило работает на уровне цепи (net) в проекте и отмечает любой незавершённый примитив дорожки/дуги либо незавершённую дорожку/дугу, оканчивающуюся переходным отверстием, тем самым образующую «антенну».

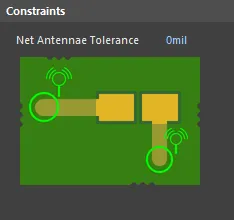

Ограничения

Ограничение по умолчанию для правила Net Antennae

Net Antennae Tolerance - максимально допустимая длина «хвоста» (stub) незавершённого примитива дорожки/дуги (или оканчивающегося переходным отверстием).

Применение правила

Online DRC и Batch DRC.

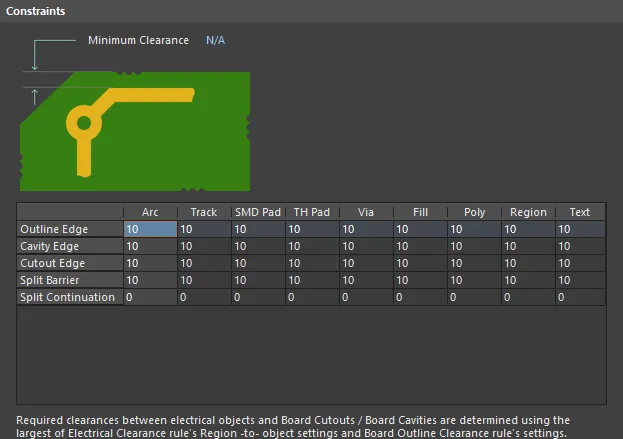

Board Outline Clearance

Правило по умолчанию: не требуется

Это правило задаёт минимально допустимый зазор от изготавливаемых объектов проекта до краёв платы. Можно указать одно значение зазора для всех вариантов «объект–край», либо определить разные зазоры для разных сочетаний, используя специализированную Minimum Clearance Matrix. Термины Board Outline и Board Edge — это общие названия, используемые взаимозаменяемо для обозначения внешней границы платы. Термин edge определён в таблице под изображением. Правило Board Outline Clearance проверяет зазоры «объект–край» на электрических слоях и слоях overlay (шелкография).

Ограничения

Ограничения по умолчанию для правила Board Outline Clearance

| Тип края | Определение |

|---|---|

| Outline Edge | Самый внешний (наружный) край платы |

| Cavity Edge | Край пользовательской полости (cavity) |

| Cutout Edge | Край пользовательского выреза (cutout) |

| Split Barrier | Когда линия Split Line задаёт край платы на этом слое, этот край называется Split Line Barrier |

| Split Continuation | Когда этот слой продолжается за линией Split Line, этот край называется Split Line Continuation (проницаемая граница). Чтобы разрешить определённому типу объектов пересекать Split Continuation, установите значение зазора равным нулю. Ноль означает, что для этих типов объектов это слой-продолжение, и объектам разрешено нарушать (пересекать) линию разделения. Используйте этот приём, чтобы, например, разрешить трассам переходить из одной области Layer Stack Region в другую. |

- Minimum Clearance - значение минимально требуемого зазора. Введённое здесь значение будет продублировано во всех ячейках матрицы Minimum Clearance Matrix. В свою очередь, если для одной или нескольких пар объектов в матрице будет задано другое значение зазора, ограничение Minimum Clearance изменится на N/A, отражая, что единое значение зазора не применяется ко всей плате.

- Minimum Clearance Matrix - предоставляет возможность тонкой настройки зазоров между различными комбинациями «объект–край» в проекте.

Работа с матрицей зазоров

Задание значений зазоров в матрице можно выполнять следующими способами:

- Редактирование одной ячейки — чтобы изменить минимальный зазор для конкретной пары объектов.

-

Редактирование нескольких ячеек — чтобы изменить минимальный зазор для нескольких пар объектов:

- Используйте Ctrl+Click, Shift+Click и Click+Drag, чтобы выбрать несколько ячеек в столбце.

- Используйте Shift+Click и Click+Drag, чтобы выбрать несколько смежных ячеек в строке.

- Используйте Click+Drag, чтобы выбрать несколько смежных ячеек в нескольких строках и столбцах

- Щёлкните по заголовку строки, чтобы быстро выбрать все ячейки в этой строке.

- Щёлкните по заголовку столбца, чтобы быстро выбрать все ячейки в этом столбце.

После выполнения нужного выделения (одной ячейки или нескольких) изменение текущего значения сводится к вводу требуемого нового значения. Чтобы применить введённое значение, щёлкните в другом месте (в другой ячейке) или нажмите Enter. Все ячейки в выделении будут обновлены новым значением.

Применение правила

Online DRC, Batch DRC, интерактивная трассировка и автотрассировка.

Локализовано с помощью ИИ

Локализовано с помощью ИИ