Wyzwanie

Wraz ze stale rosnącymi prędkościami przełączania układów pojawia się wyzwanie utrzymania integralności sygnału oraz spełnienia wymagań czasowych sygnału. Integralnością sygnału można zarządzać poprzez prowadzenie ścieżek o kontrolowanej impedancji, co osiąga się dzięki starannemu zaprojektowaniu zarówno stackupu PCB, jak i szerokości ścieżek stosowanych na poszczególnych warstwach.

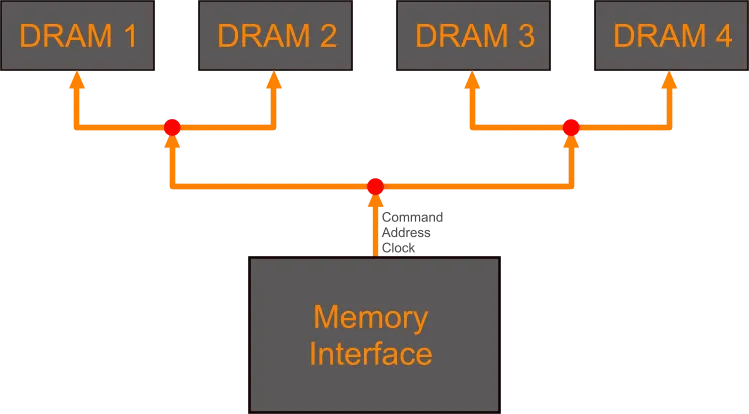

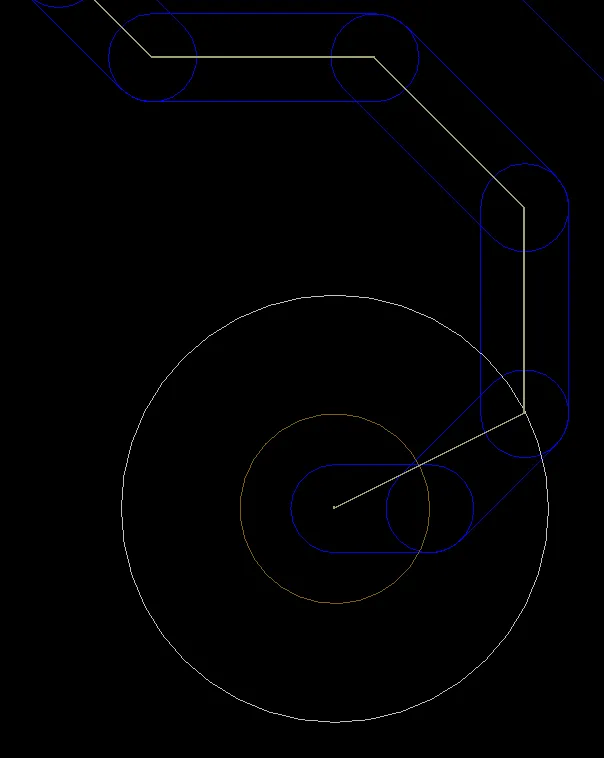

Wymagania czasowe spełnia się przez dopasowanie długości poprowadzonych ścieżek sygnałowych. Dla zestawu ścieżek sygnałowych 2‑pinowych, z których każda biegnie od pinu wyjściowego do pojedynczego pinu wejściowego, obliczanie i porównywanie długości jest procesem prostym. Nie dotyczy to jednak wielu typowych rozwiązań projektowych, gdzie w torze sygnału może znajdować się element terminacji szeregowej albo sygnał obejmuje więcej niż dwa piny, co można następnie poprowadzić topologią Balanced T lub Fly‑By, jak pokazano na poniższym obrazie.

Cztery układy DDR2 RAM poprowadzone topologią Balanced T. ##

Rozwiązanie

Zadaniem projektanta jest przełożenie wymagań projektowych, takich jak maksymalna dopuszczalna długość prowadzenia wynikająca z budżetu czasowego, na zestaw reguł projektowych, takich jak reguła Length zapewniająca dotrzymanie wymagań czasowych oraz reguła Matched Length wykrywająca potencjalne niedopasowania czasowe.

Teraz projektant postrzega sygnały przez pryzmat ich funkcji (np. „Ten sygnał adresowy musi być poprowadzony od tego złącza do każdego układu pamięci. Żeby to osiągnąć, poprowadzę go topologią fly‑by z rezystorem terminującym na końcu. Mogę też wymagać terminatora szeregowego przy źródle”). Mimo że adres A0 przechodzi przez rezystor terminujący, dla projektanta ten sygnał po drugiej stronie rezystora nadal jest A0.

Edytor PCB widzi jednak każdy sygnał po prostu jako zestaw połączonych pinów (powszechnie nazywany netem) — net A0 biegnie od tego pinu złącza do tego pinu układu pamięci, potem do tego pinu układu pamięci itd. Gdy tylko zostanie dodany rezystor terminacji szeregowej, ta linia adresowa staje się dwoma odrębnymi netami. Utrudnia to projektantowi określenie kluczowych wymagań projektowych, takich jak reguły Length i Matched Length.

Można tym zarządzać dzięki funkcji o nazwie xSignals (lub exxtended Signal). Funkcja ta umożliwia poprawne traktowanie szybkiego toru sygnałowego właśnie jako toru — ścieżki, którą sygnał przemieszcza się między źródłem a celem, przez elementy terminujące oraz rozgałęzienia.

xSignal to w istocie zdefiniowana przez projektanta ścieżka sygnałowa pomiędzy dwoma węzłami. Mogą to być dwa węzły w obrębie tego samego netu albo dwa węzły w powiązanych netach rozdzielonych elementem. xSignal można następnie wykorzystać do zawężenia zakresu odpowiednich reguł projektowych, takich jak Length i Matched Length, które będą wtedy przestrzegane podczas zadań projektowych, np. interaktywnego strojenia długości.

Tworzenie nowego xSignal

xSignal to zdefiniowana przez projektanta ścieżka sygnałowa pomiędzy dwoma węzłami; mogą to być dwa węzły w obrębie tego samego netu albo dwa węzły w różnych netach.

xSignals definiuje się następującymi metodami:

- Użyj xSignals Multi-Chip Wizard. Będzie to najczęstsze podejście do tworzenia xSignals i jest opisane poniżej.

Alternatywnie, poniższe metody stosuje się, najpierw zaznaczając interesujące obiekty, a następnie wybierając odpowiednie polecenie:

-

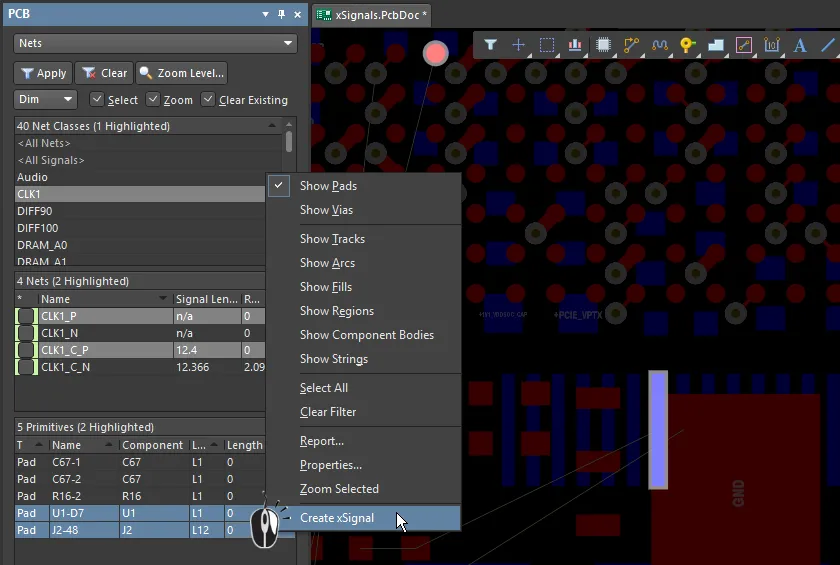

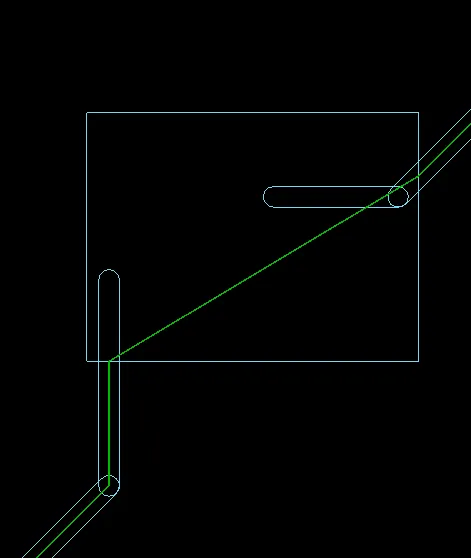

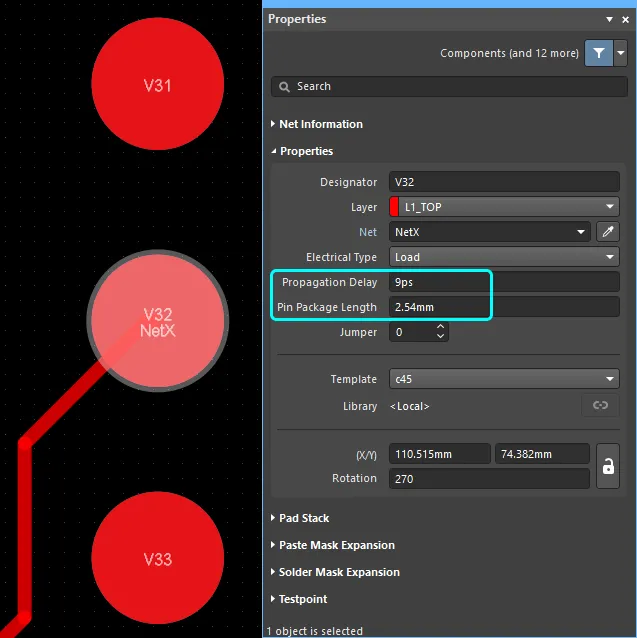

Utwórz pojedynczy xSignal na podstawie zaznaczonych padów. Zaznacz wymagany pad początkowy i pad końcowy (pady te mogą należeć do różnych netów, jeśli występuje element terminacji szeregowej). Pady można zaznaczać bezpośrednio w obszarze projektu albo użyć panelu PCB w trybie Nets, aby zlokalizować i zaznaczyć pady (jak pokazano na obrazie poniżej). Po zaznaczeniu padów kliknij prawym przyciskiem na jednym z zaznaczonych padów w obszarze projektu, a następnie uruchom polecenie xSignals » Create xSignal from Selected Pins, albo kliknij prawym przyciskiem na jednym z zaznaczonych padów w panelu PCB i uruchom polecenie Create xSignal. Nowy xSignal zostanie wyświetlony w trybie xSignals panelu PCB.

Gdy definiujesz xSignal na podstawie zaznaczonych pinów (padów footprintu), przed uruchomieniem polecenia Create zaznacz tylko pad początkowy i pad końcowy.

Nazwa nowego xSignal będzie kombinacją dwóch nazw netów, rozdzielonych łącznikiem. Nazwę xSignal można edytować w trybie xSignals panelu PCB.

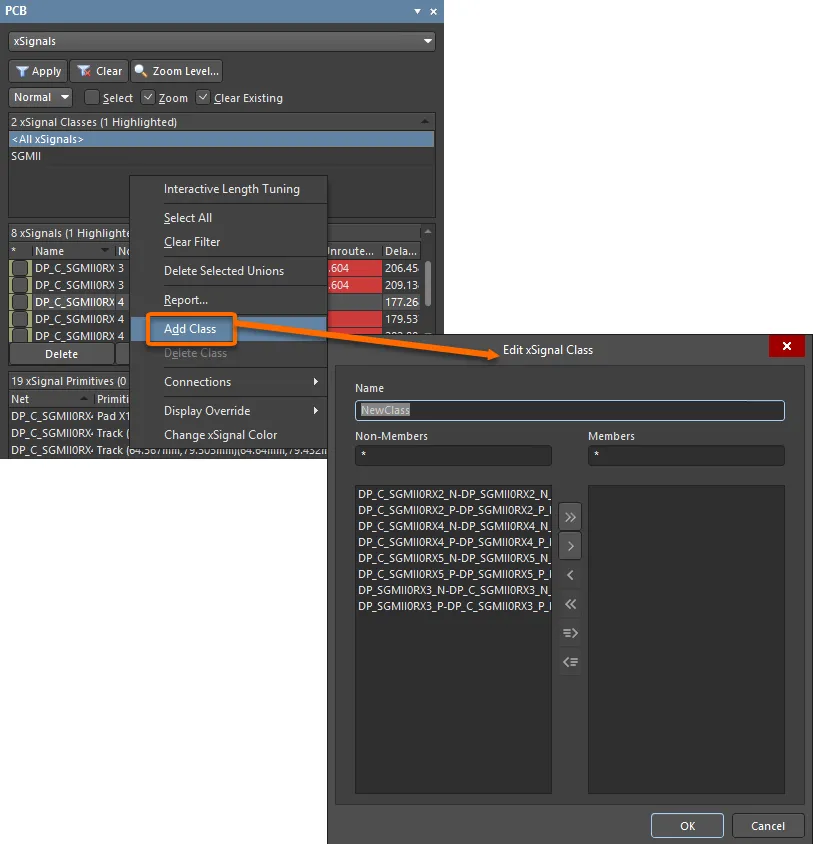

Nowy xSignal można dodać do klasy xSignal; kliknij prawym przyciskiem w obszarze xSignal Classes panelu, aby utworzyć nową klasę i dodać do niej elementy.

- Zaznacz komponent źródłowy, następnie kliknij prawym przyciskiem na zaznaczonym komponencie i wybierz z menu kontekstowego polecenie xSignal » Create xSignals between Components . Otworzy się okno dialogowe Create xSignals Between Components, z zaznaczonym wybranym komponentem źródłowym. Okno dialogowe jest opisane poniżej.

- Zaznacz jeden lub więcej komponentów szeregowych w obszarze projektu, następnie kliknij prawym przyciskiem na jednym z zaznaczonych komponentów i wybierz z menu kontekstowego polecenie xSignal » Create xSignals from Connected Nets . Otworzy się okno dialogowe Create xSignals From Connected Nets. Zostanie zaznaczony wybrany komponent źródłowy oraz nety podłączone do tego komponentu. Okno dialogowe jest opisane poniżej.

- Mogą też wystąpić sytuacje, w których chcesz utworzyć xSignal wewnątrz istniejącego xSignal; w takim przypadku można użyć trybu xSignal panelu PCB. Upewnij się, że na górze panelu jest włączona opcja Select, znajdź bieżący xSignal, zaznacz wymagane pady w sekcji xSignal Primitives panelu, a następnie kliknij prawym przyciskiem na jednym z zaznaczonych padów w obszarze projektu i użyj metody opisanej w kroku 2 tej listy, aby zakończyć proces.

Zaznacz dwa pady w trybie Nets panelu, kliknij prawym przyciskiem na jednym z zaznaczonych padów, a następnie wybierz Create xSignal. Zwróć uwagę, że pady należą do różnych netów.

Jeśli pad początkowy i końcowy znajdują się w tym samym necie, xSignal otrzyma nazwę w postaci <NetName>_PPn, gdzie n jest kolejną dostępną liczbą całkowitą używaną do rozróżnienia wielu xSignals zdefiniowanych dla tego netu. Jeśli pad początkowy i końcowy znajdują się w różnych netach, xSignal otrzyma nazwę w postaci <StartNet>_<EndNet>_PPn, gdzie n jest kolejną dostępną liczbą całkowitą używaną do rozróżnienia wielu xSignals zdefiniowanych dla tej kombinacji netów.

Kreator xSignals Multi-Chip

xSignals Multi-Chip Wizard służy do tworzenia xSignals pomiędzy pojedynczym komponentem źródłowym a wieloma komponentami docelowymi. Wizard wykorzystuje podejście zorientowane na komponenty do identyfikacji potencjalnych xSignals — wybierasz pojedynczy komponent źródłowy, interesujące nety oraz komponenty docelowe, a następnie Wizard analizuje wszystkie potencjalne ścieżki od komponentu źródłowego do komponentów docelowych, przechodząc przez szeregowe elementy pasywne i wzdłuż wszelkich rozgałęzień. Jako projektant możesz następnie wybrać xSignals, które chcesz wygenerować, a także utworzyć reguły projektowe Matched Length, jeśli są wymagane. Wizard może również służyć do automatycznego tworzenia xSignals i klas xSignal dla wielu różnych, typowych interfejsów oraz układów pamięci.

W tym Wizard pin wyjściowy jest określany jako Source, a docelowy pin wejściowy jako Destination.

Kreator jest także narzędziem wielokrotnego uruchamiania — z ogólnej, nadrzędnej grupy xSignals, którą początkowo tworzysz na stronie xSignal Routes, możesz wybrać jej podzbiór, zdefiniować klasy i reguły, następnie wrócić do grupy nadrzędnej, wybrać kolejny podzbiór, zdefiniować dla niego klasy i reguły itd.

Jedną z największych zalet Wizard jest łatwość pracy pomiędzy Wizard a edytorem PCB. Kliknij xSignal na dowolnej stronie Kreatora, a pady oraz wszelkie prowadzenia zostaną wizualnie podświetlone na PCB.

Na tym etapie Kreator nie obsługuje automatycznego dodawania identyfikatorów złączy typu T, często nazywanych tie‑points lub branch‑points. Jeśli Twój projekt zawiera prowadzenie z rozgałęzieniami, zaleca się, aby:

- Stroić długość od komponentu źródłowego do komponentu pasywnego (np. rezystora terminacji szeregowej), jeśli takie występują.

- Stroić długość w każdej gałęzi, od złącza T do komponentu docelowego.

- Jeśli to konieczne, dostroić pozostałą długość pomiędzy komponentem pasywnym (lub od źródła, jeśli nie ma elementów pasywnych) a złączem T.

Jeśli musisz stroić długości wyłącznie gałęzi, utwórz zdefiniowany przez użytkownika punkt rozgałęzienia, umieszczając w prowadzeniu przy złączu T komponent jednowarstwowy z pojedynczym padem. Więcej informacji znajdziesz w sekcji

Defining the Branch Point in a Balanced T Pattern poniżej.

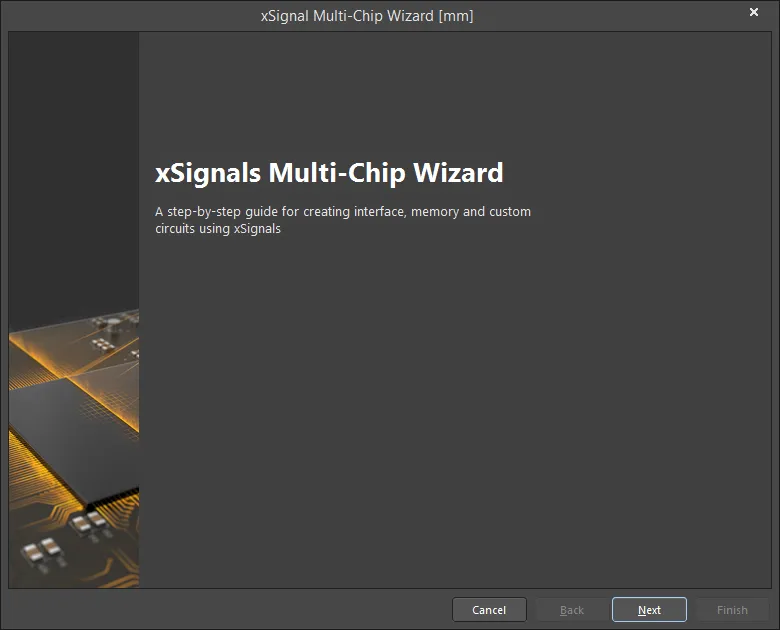

Aby uzyskać dostęp do xSignals Multi-Chip Wizard, wybierz polecenie Design » xSignals » Run xSignals Wizard z menu głównego lub kliknij prawym przyciskiem w układzie PCB, a następnie wybierz xSignals » Run xSignals Wizard. Zostanie wyświetlona strona startowa Kreatora.

Strona startowa xSignals Multi-Chip Wizard

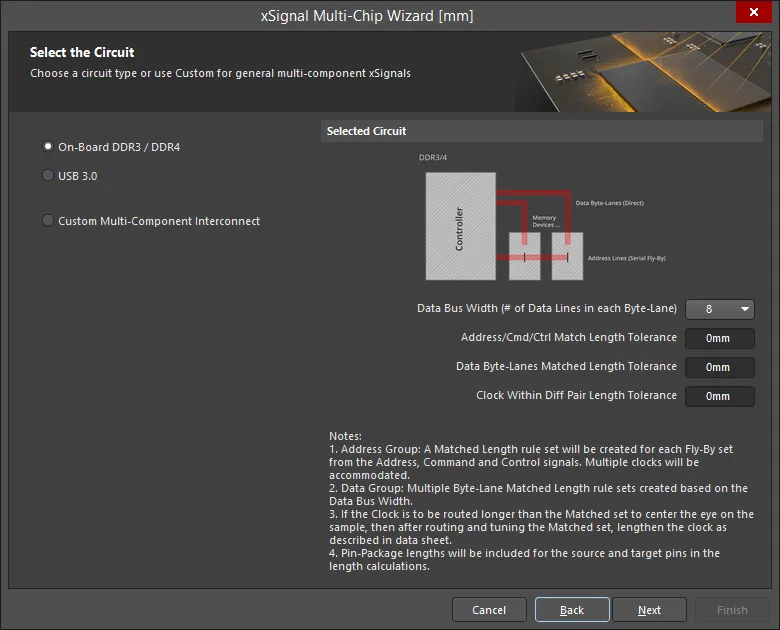

Kreatora xSignals Multi-Chip — tryby

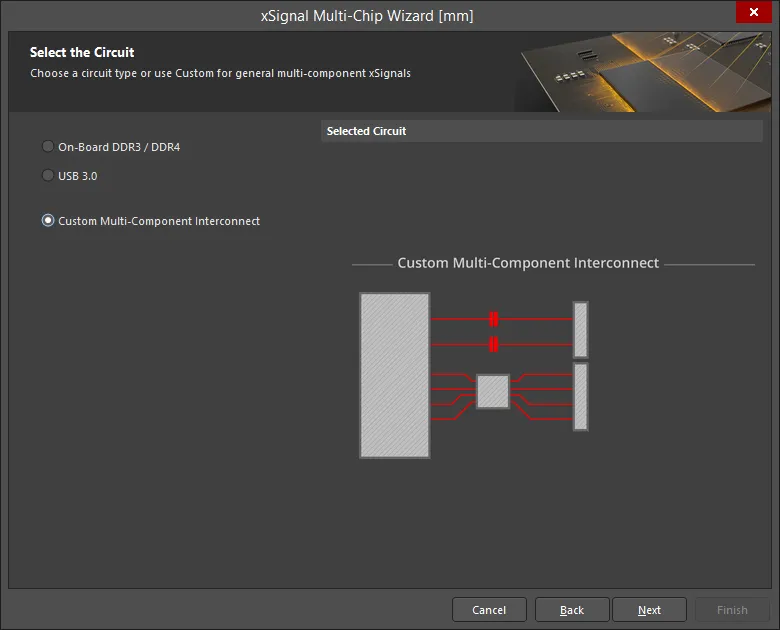

Na drugiej stronie Wizard zostaniesz poproszony o wybór Custom Multi-Component Interconnect, On-Board DDR3 / DDR4 lub USB 3.0. Tryb Custom Multi-Component Interconnect służy do definiowania wielu xSignals pomiędzy wybranym komponentem źródłowym a wieloma komponentami docelowymi, natomiast tryb On-Board DDR3 / DDR4 służy do tworzenia xSignals dla pamięci DDR3 lub DDR4. Tryb USB 3.0 tworzy xSignals, klasy xSignal oraz reguły Matched Length dla każdego kanału USB 3.0. Wybierz tryb odpowiedni do swoich potrzeb.

The Custom Multi-Component Interconnect Mode

W tym trybie Kreator może zostać użyty do zdefiniowania wielu xSignals pomiędzy wybranym komponentem źródłowym a wieloma komponentami docelowymi. Kreator stosuje podejście zorientowane na komponenty do identyfikacji potencjalnych xSignals; wybierasz pojedynczy komponent źródłowy, interesujące Cię sieci oraz komponenty docelowe; następnie analizuje wszystkie potencjalne ścieżki od komponentu źródłowego do komponentów docelowych, przechodząc przez szeregowe elementy pasywne oraz wzdłuż wszelkich odgałęzień. Jako projektant wybierasz potem xSignals, które mają zostać wygenerowane. Oprócz definiowania end-to-end xSignals dla wielu sieci pomiędzy komponentami, Kreator umożliwia także tworzenie xSignals dla odcinków tych sygnałów end-to-end (od pinu wyjściowego źródła do szeregowego elementu terminującego oraz od szeregowego elementu terminującego do pinu wejściowego celu). W zależności od włączonych ustawień Kreator może również tworzyć klasy xSignal oraz reguły projektowe Matched Net Lengths ukierunkowane na te xSignals. Po zakończeniu pracy Kreatora możesz rozpocząć proces dopasowywania długości.

Kreator jest konfigurowany na kilku stronach. Liczba stron zależy od konfiguracji układu. Na przykład, jeśli występują terminatory szeregowe, pojawią się dodatkowe strony. Konfiguracja każdej strony została opisana poniżej.

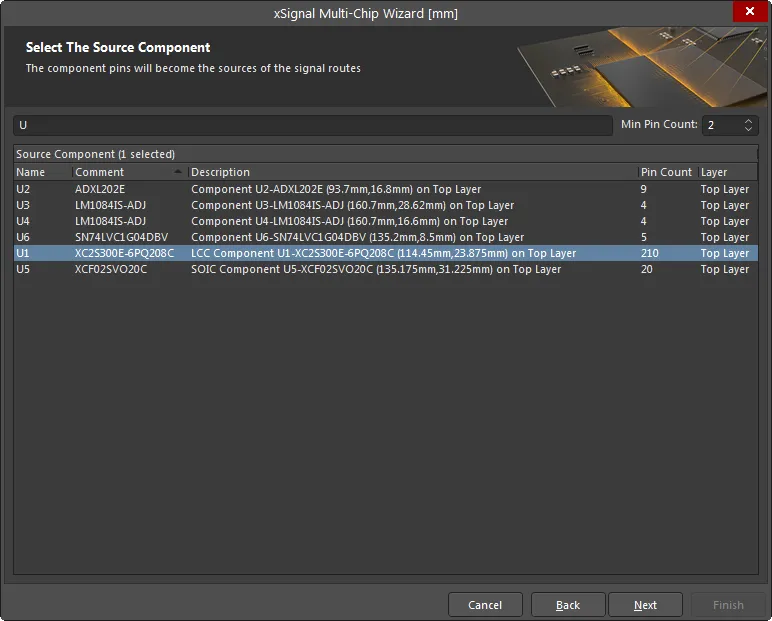

Wybierz komponent źródłowy

Użyj tej strony, aby wybrać pojedynczy komponent źródłowy. Użyj pól Filter oraz Min Pin Count u góry siatki, aby łatwiej zlokalizować interesujący komponent. Obsługiwane są symbole wieloznaczne * i ?.

Siatki w tym Kreatorze zawierają menu skrótów dostępne pod prawym przyciskiem myszy, a także obsługę standardowych klawiszy wielokrotnego zaznaczania w Windows. Możesz też użyć lewego przycisku myszy lub spacji, aby przełączać checkbox zaznaczonych elementów.

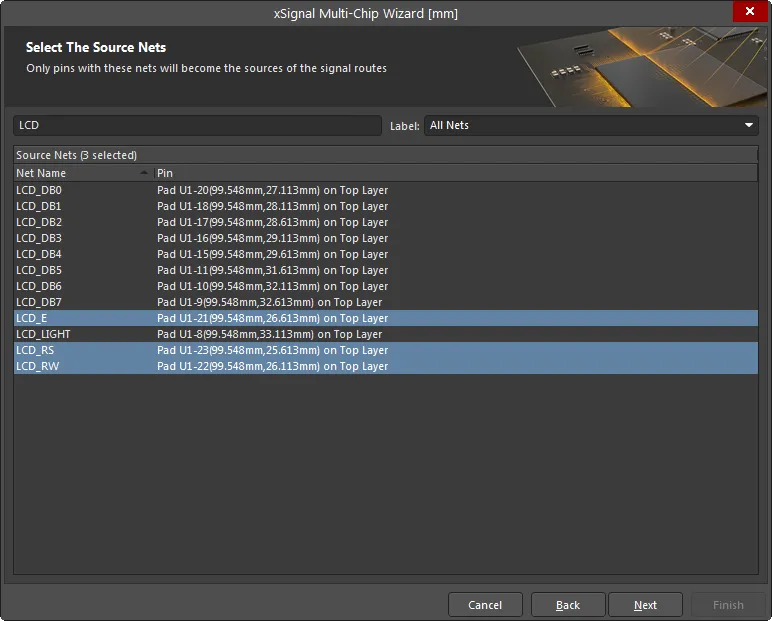

Wybierz sieci źródłowe

Wybierz interesujące Cię sieci podłączone do wybranego komponentu źródłowego. Użyj pól Filter oraz Label u góry siatki, aby łatwiej zlokalizować interesujące sieci. Tylko piny z wymienionymi sieciami staną się źródłami tras sygnałowych.

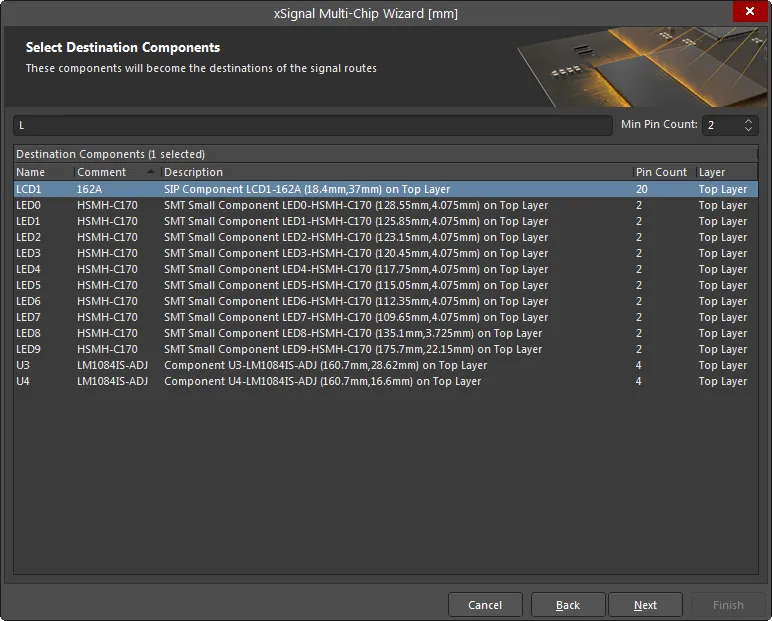

Wybierz komponenty docelowe

Wybierz żądany(e) komponent(y) docelowy(e). Użyj pól komponentu Filter oraz Min Pin Count u góry siatki, aby łatwiej zlokalizować interesujący komponent.

Po kliknięciu Next Kreator zidentyfikuje wszystkie możliwe xSignals, które można utworzyć z zestawu sieci wybranych pomiędzy wskazanymi komponentami. Jeśli Kreator wykryje elementy 2-pinowe, których oba piny są podłączone do wybranych sieci, zostaną one automatycznie zidentyfikowane jako szeregowe elementy terminujące i w dalszej części procesu pojawią się dodatkowe strony Kreatora.

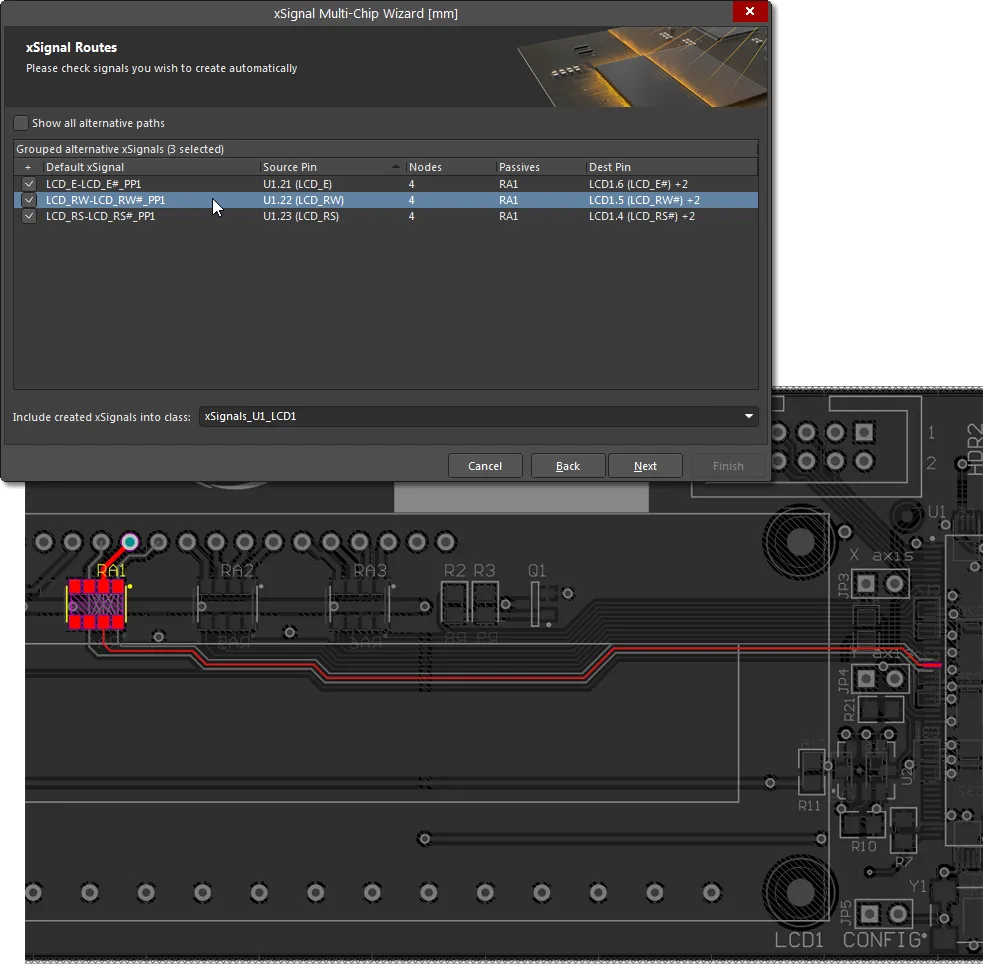

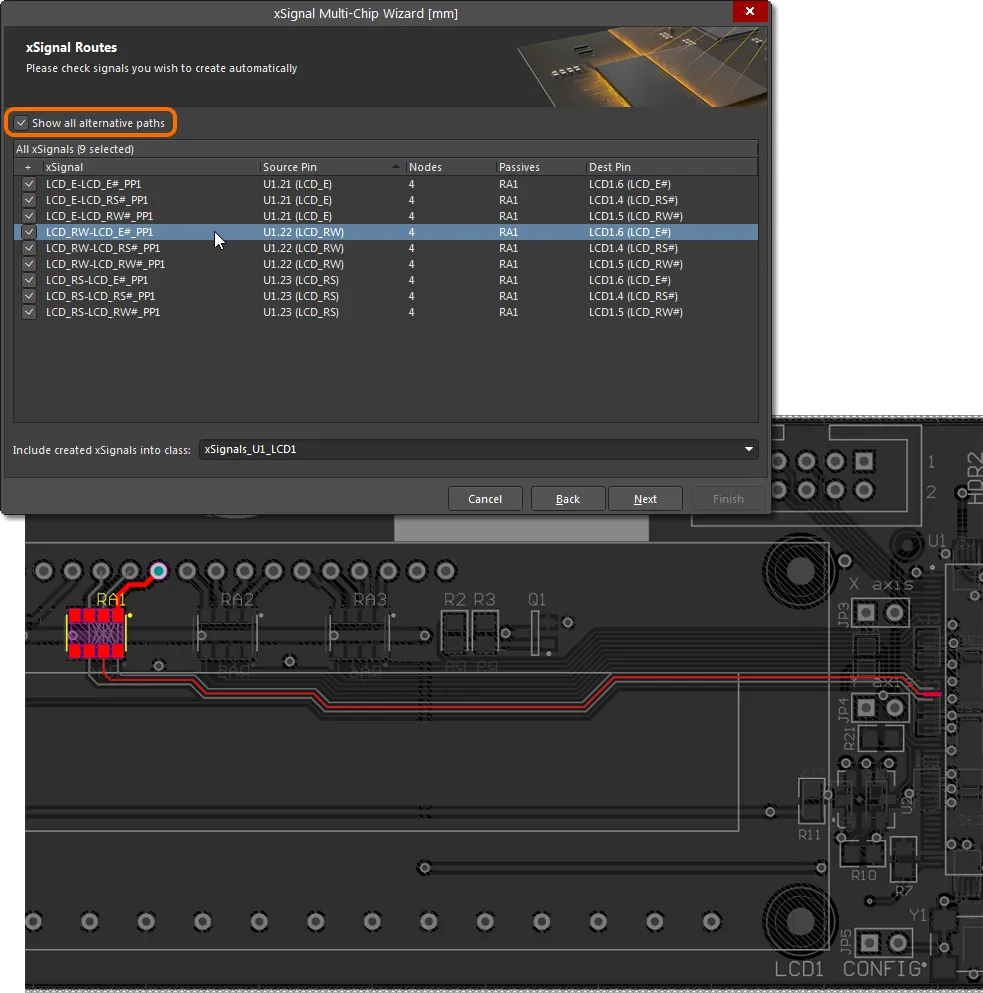

Trasy xSignal

Ta strona Kreatora wyświetla proponowane xSignals od każdego Source Pin do każdego Destination Pin. Kliknij wpis, aby podświetlić ten xSignal na PCB.

Po przeanalizowaniu ścieżek sieci w celu zidentyfikowania potencjalnych xSignals, Kreator spróbuje następnie zredukować zestaw tak, aby wyświetlić tylko kombinacje, które Cię interesują. Są to end-to-end xSignals; powyższy obraz pokazuje je pomiędzy komponentami źródłowymi i docelowymi wybranymi na poprzednich stronach Kreatora. Obraz pokazuje również, że Kreator wykrył w każdej trasie szeregowy element terminujący RA1. RA1 jest w rzeczywistości czterorezystorowym pakietem – w takiej sytuacji Kreator automatycznie utworzy powiązania logiczne, zakładając, że każdy rezystor przebiega „w poprzek” pakietu; sparuje sieci podłączone do pinów leżących naprzeciw siebie na komponencie.

Ponieważ założenie, że piny każdego rezystora leżą naprzeciw siebie, nie zawsze musi być poprawne, możesz wybrać dowolną inną dostępną sieć wyjściową z listy rozwijanej w kolumnie Dest Pin. Alternatywnie włącz opcję Show all alternative paths u góry siatki, aby wyświetlić wszystkie potencjalne kombinacje sieci, które mogłyby zostać użyte do wygenerowania xSignals. Zaznacz checkbox dla każdej linii, dla której chcesz utworzyć xSignal. Włączone xSignals zostaną dodane do klasy wyświetlanej w polu Include created xSignals into class na dole tej strony. Wpisz nową nazwę lub wybierz ją z listy rozwijanej.

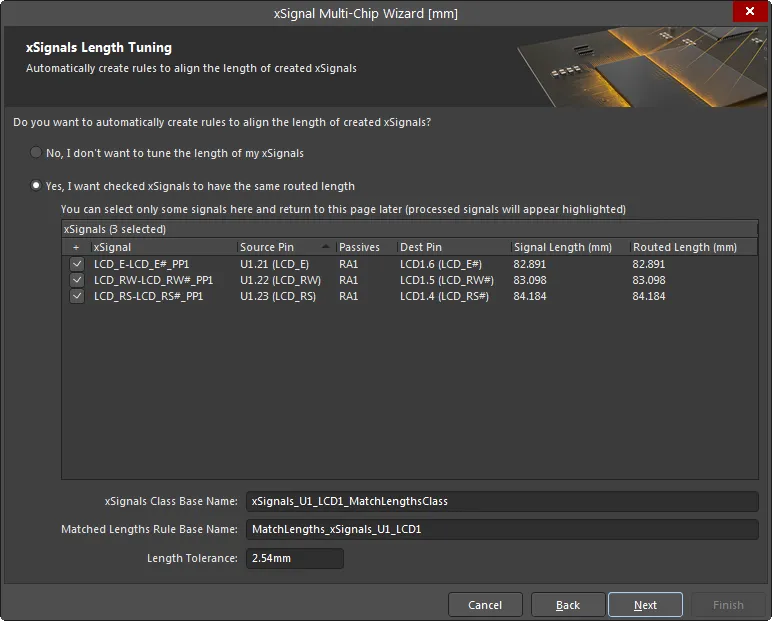

Dopasowywanie długości xSignals

Ta strona służy do automatycznego utworzenia reguły projektowej Matched Length dla włączonych xSignals. Włącz only te xSignals, które mają być objęte tą nową regułą projektową. Jeśli projekt wymaga wielu reguł o różnych wymaganiach, w dalszej części procesu otrzymasz możliwość zdefiniowania dodatkowych reguł dla tych xSignals, dla których reguła nie została jeszcze zdefiniowana. Ten pierwszy etap pokaże również ogólne end-to-end xSignals. Na kolejnych stronach Kreatora będziesz mieć możliwość zdefiniowania reguł projektowych dla sekcji wewnątrz xSignals – na przykład dla odcinków od pinu wyjściowego do szeregowego rezystora terminującego.

Jeśli nie chcesz dopasowywać długości swoich xSignals, włącz No, I don't want to tune the length of my xSignals. Jeśli ta opcja jest włączona, żadne inne opcje na tej stronie nie będą dostępne. Aby móc edytować i uzyskać dostęp do pozostałych opcji, włącz Yes, I want checked xSignals to have the same routed length.

Pole xSignals Class Base Name służy do zdefiniowania nazwy dla aktualnie wybranych xSignals. Wpisz znaczącą nazwę, pamiętając, że możesz powtarzać ten proces dla innych xSignals. Ten zestaw xSignals będzie następnie objęty regułą projektową o nazwie wpisanej w polu Matched Lengths Rule Base Name, z określonym Length Tolerance.

Nie masz pewności, które obiekty są obejmowane? Kliknij jeden lub więcej wpisów, aby podświetlić ścieżkę(i) sygnału w układzie PCB.

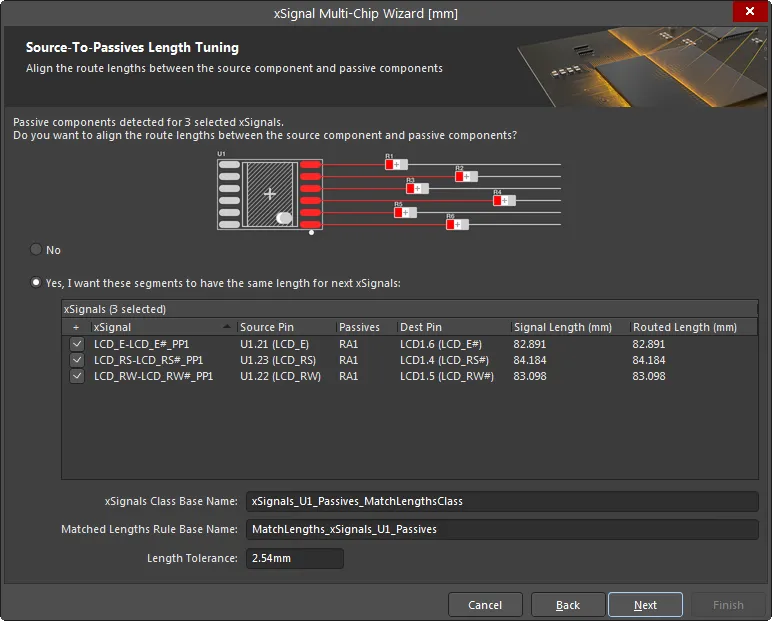

Dopasowywanie długości od źródła do pasywnych

Jeśli wybrany zestaw sieci obejmuje szeregowe elementy terminujące, pojawią się dodatkowe strony Kreatora, które dadzą możliwość utworzenia dodatkowych xSignals i reguł projektowych dla tych sekcji sieci. Na powyższym obrazie widać, że ta strona Kreatora jest używana do utworzenia reguły projektowej Matched Length dla wybranych xSignals biegnących od pinów źródłowych do elementów terminujących. Jeśli potrzebujesz xSignals / klasy xSignal / reguły projektowej dla tych odcinków, włącz opcję Yes, I want these segments to have the same length for next xSignals, włącz wymagane xSignals i zdefiniuj xSignals Class Base Name, Matched Lengths Rule Base Name oraz Length Tolerance. Zostaną utworzone dodatkowe xSignals do użycia z tą regułą Matched Length.

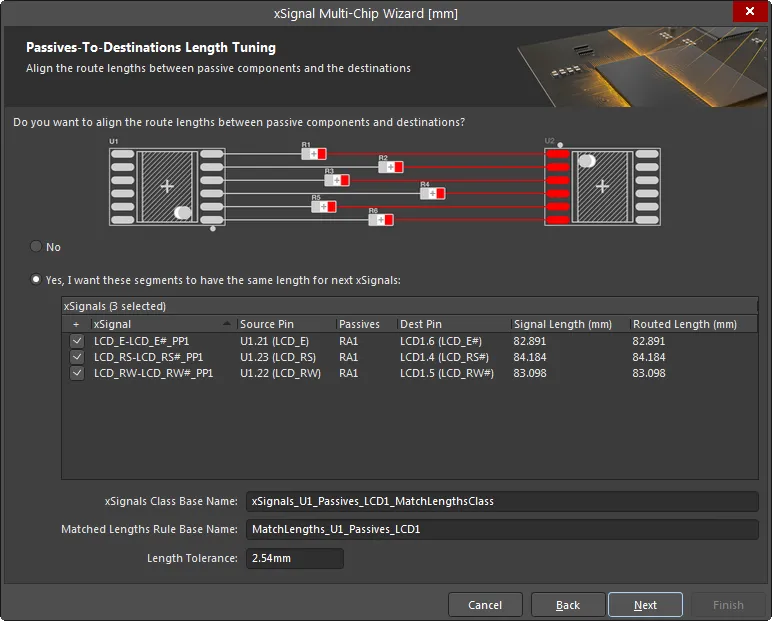

Dopasowywanie długości od pasywnych do celów

Ta strona służy do utworzenia reguły projektowej Matched Length dla wybranych xSignals biegnących od elementów terminujących do pinów docelowych. Jeśli jest to wymagane, włącz opcję Yes, I want these segments to have the same length for next xSignals , włącz wymagane xSignals i zdefiniuj xSignals Class Base Name, Matched Lengths Rule Base Name oraz Length Tolerance. Zostaną utworzone dodatkowe xSignals do użycia z tą regułą Matched Length.

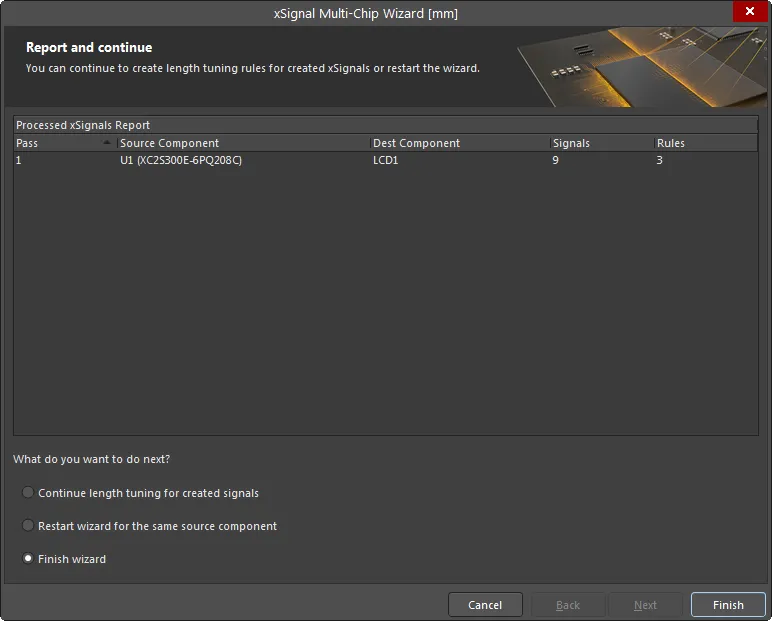

Raport i kontynuacja

Ta strona Kreatora wyszczególni liczbę xSignals, które mają zostać utworzone, oraz liczbę reguł projektowych, które mają zostać utworzone.

Na dole strony możesz wybrać:

- Continue length tuning for created signals – wybierz, jeśli na poprzednich stronach wyłączyłeś określone xSignals i teraz musisz przejść przez proces definiowania dodatkowych reguł dla tych xSignals.

- Restart wizard for the same source component – wybierz, jeśli chcesz odrzucić te ustawienia i uruchomić Kreator ponownie z tymi samymi wybranymi komponentami/sieciami.

- Finish wizard – wybierz, jeśli zakończyłeś tworzenie xSignal i reguł projektowych dla tego komponentu źródłowego.

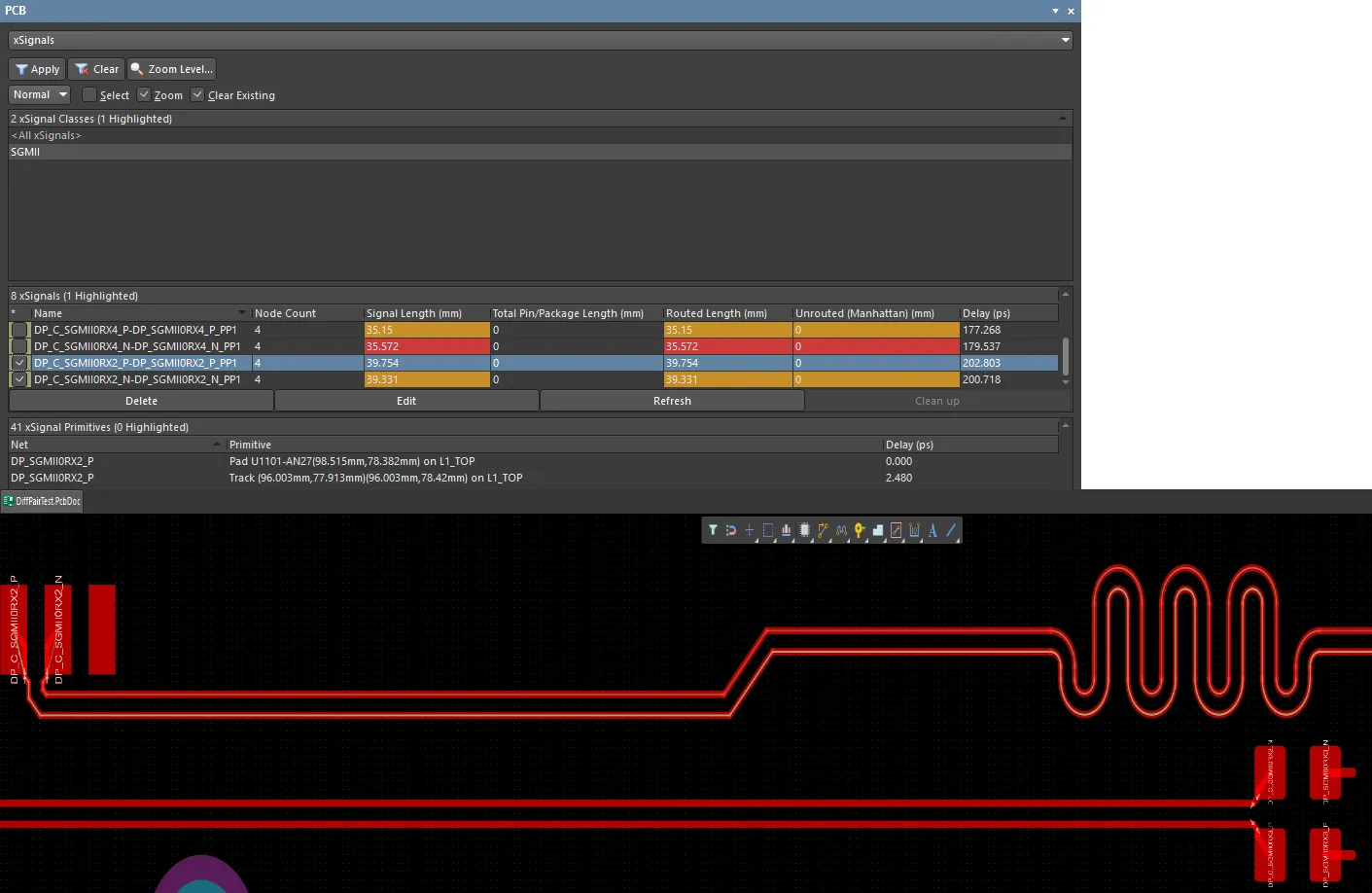

xSignals są wyszczególnione w trybie xSignal panelu PCB. Naciśnij klawisz Delete w panelu, aby usunąć wybrane klasy xSignal lub wybrane xSignals.

Te xSignals są gotowe do dopasowywania długości. Aby rozpocząć, wybierz opcję Interactive Length Tuning ( ) z głównego menu Route lub z Active Bar.

) z głównego menu Route lub z Active Bar.

Możesz łatwo usunąć „harmonijkę” dopasowywania długości. Kliknij raz dowolny segment harmonijki, aby go zaznaczyć, a następnie naciśnij Delete.

Zwróć uwagę, że istniejące segmenty ścieżek są dzielone w punktach początkowym i końcowym podczas umieszczania harmonijki. Dlatego, jeśli powtórzysz ten proces strojenia i usuwania kilka razy, możesz skończyć z prostym odcinkiem prowadzenia, który w rzeczywistości składa się z wielu krótkich segmentów ścieżek. Aby scalić wiele małych segmentów ścieżek z powrotem w jeden segment, uruchom polecenie Design » Netlist » Clean All Nets z głównych menu.

On-Board DDR3 / DDR4

W tym trybie kreator automatycznie utworzy xSignals, klasy xSignal, Matched Length Groups, reguły Diff Pair Matched Lengths oraz topologię Fly-By dla wbudowanej pamięci DDR3/DDR4. Kreator zakłada, że zostanie użyta topologia prowadzenia typu fly-by.

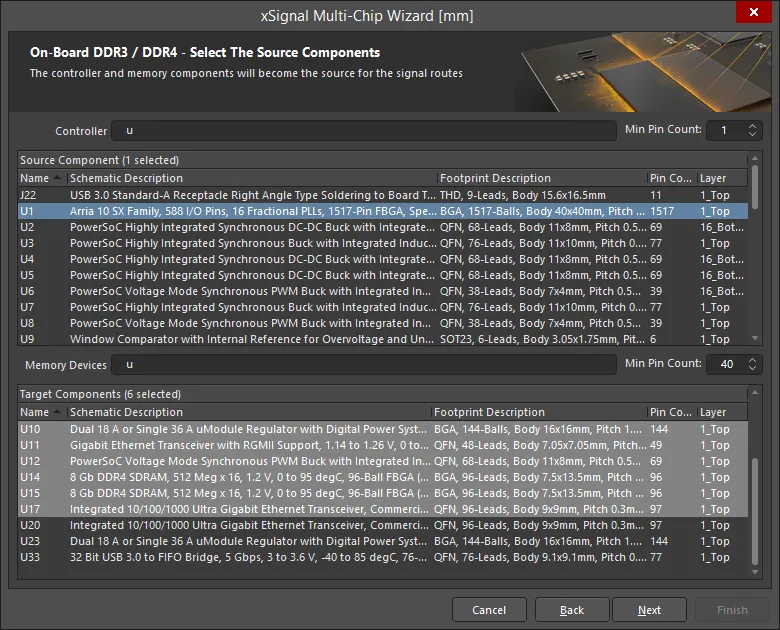

Wybierz komponenty źródłowe

Na tej stronie Wizard identyfikuje wszystkie potencjalne komponenty źródłowe i komponenty docelowe na podstawie prefiksu oznaczenia oraz liczby pinów. Użyj pól Controller/Memory Devices , aby filtrować komponenty/układy pamięci, oraz użyj strzałek góra/dół, aby ustawić Min Pin Count zgodnie z wymaganiami zarówno dla Source Component, jak i Target Components . Następnie wybierz pojedynczy komponent źródłowy i wybierz komponent(y) docelowy(e).

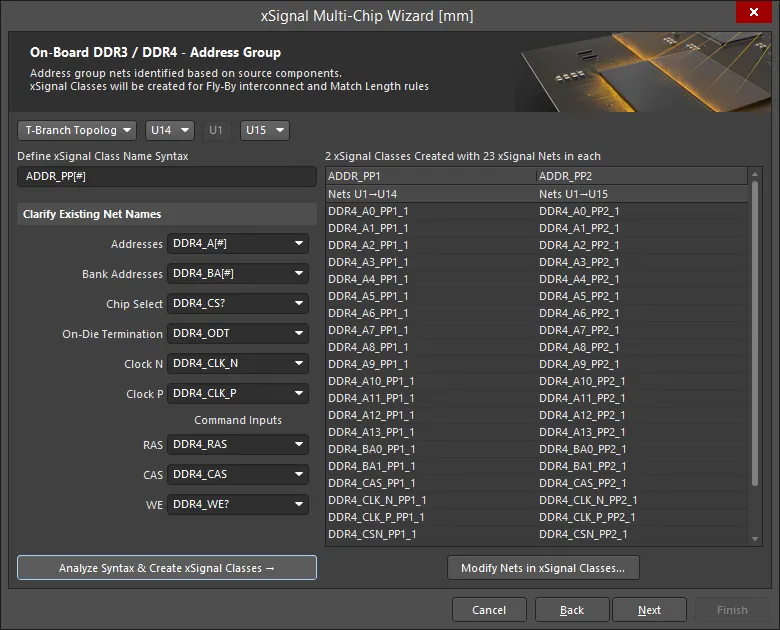

Grupa adresowa

Funkcjonalność tej strony jest następująca:

- Fly-By Topology Obsługiwane są opcje T-Branch Topology oraz T-Branch Topology. Wybierz wymaganą topologię z listy rozwijanej.

- Jeśli wybrano Fly-By Topology, urządzenia docelowe są wyświetlane w kolejności Point-to-Point dla prowadzenia fly-by. Oprogramowanie spróbuje określić tę kolejność automatycznie. Jeśli Kreator zostanie uruchomiony przed rozmieszczeniem komponentów, kolejność point-to-point będzie musiała zostać ustawiona ręcznie za pomocą kontrolek list rozwijanych.

- Jeśli wybrano T-Branch Topology (jak pokazano powyżej), połowa urządzeń docelowych zostanie pokazana przed źródłem, a połowa po nim. Użyj kontrolek list rozwijanych, aby uporządkować komponenty docelowe zgodnie z wymaganiami.

- Define xSignal Class Name Syntax:

- Domyślnym punktem startowym jest

ADDR_PP[#]

- .

[#] reprezentuje liczbę układów pamięci.

- Sufiks

PP można zmienić, jeśli jest to wymagane.

- Kreator analizuje komponenty i wyszukuje te sufiksy w projekcie, a następnie wyświetla pełną składnię nazwy, stosując podejście opisane poniżej. Zaktualizuj je, jeśli nie są poprawne.

- Celem jest automatyczne znalezienie sieci (netów) odpowiadających tym funkcjom. Po znalezieniu netów składnia nazewnictwa jest wprowadzana do pól.

- Następnie przeglądane są nety pomiędzy komponentami; po znalezieniu sufiksu identyfikowany jest prefiks. Na przykład Kreator szuka

_A[#], aby zlokalizować linie adresowe.

- Jeśli nie zostaną znalezione żadne nety z sufiksem zaczynającym się od „_”, wtedy wyszukiwany jest wyłącznie tekst po „_”. Sprawdzane są również alternatywne separatory, takie jak „-” lub „.”.

- Jeśli składni nie da się określić automatycznie, musisz zdefiniować te pola. Użyj list rozwijanych, aby wybrać spośród istniejących netów na płytce.

- Po zdefiniowaniu kolejności i składni nazewnictwa kliknij przycisk Analyze Syntax & Create xSignal Classes, aby zbudować listę xSignals. Kreator przeanalizuje składnię oraz sposób połączenia komponentów i utworzy klasy xSignal, które zostaną wyświetlone w siatce po prawej stronie okna dialogowego. Liczba Classes Created będzie odpowiadać liczbie układów pamięci.

- Wyświetlana jest liczba utworzonych klas (np. 4) oraz liczba netów xSignal w każdej klasie (np. 26).

- xSignals są pogrupowane w kolumnie dla każdej klasy xSignal. Dla każdej klasy zostanie utworzona reguła projektowa Matched Lengths. Podnagłówki w tabeli reprezentują komponenty źródłowe i docelowe dla tych xSignals.

- Jeśli automatycznie wygenerowana lista jest niekompletna lub niepoprawna, kliknij przycisk Modify Nets in xSignal Classes, aby otworzyć okno dialogowe Edit xSignal Class i ręcznie dodać lub usunąć nety do/z klasy. Pamiętaj, że ręczne zmiany zostaną utracone, jeśli następnie ponownie klikniesz przycisk Analyze Syntax & Create xSignal Classes.

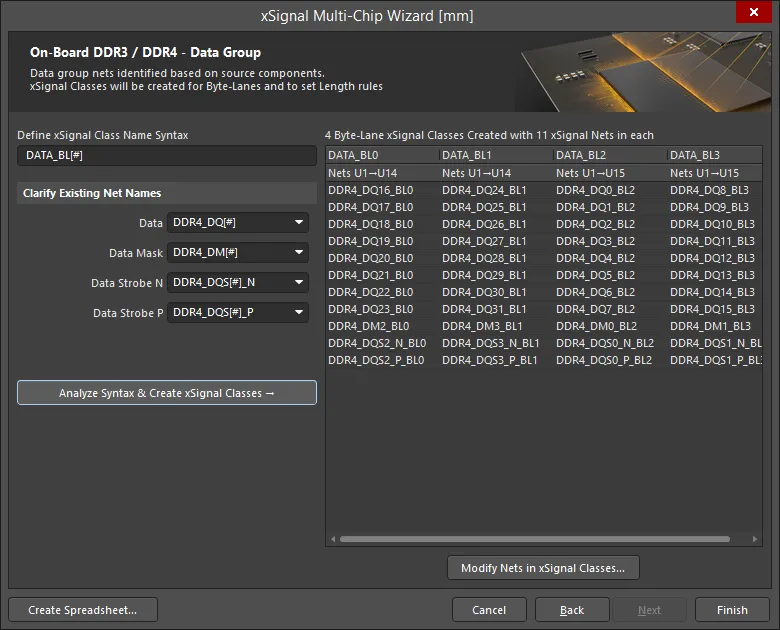

Identyfikowanie netów grupy danych

Ostatnim etapem jest zidentyfikowanie wszystkich netów należących do grupy danych (Data Group).

Funkcjonalność tej strony jest następująca:

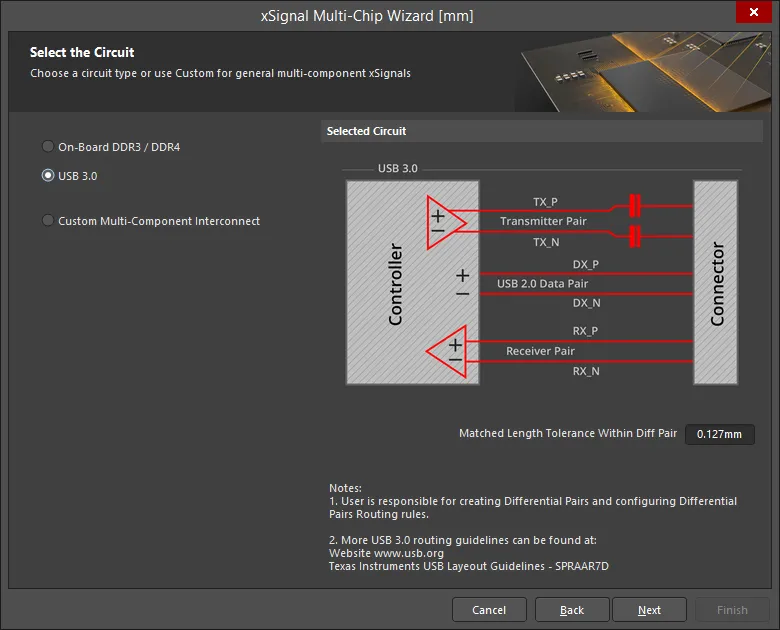

USB 3.0

Kreator może przetworzyć wszystkie kanały USB 3.0 pomiędzy każdą parą kontroler–złącze określoną przez użytkownika. Kreator automatycznie ocenia nety par różnicowych (Differential Pair) podłączone do kontrolera, wykrywając te, które przechodzą aż do złącza. Taki przebieg może obejmować elementy pasywne i wiele netów. Kreator identyfikuje każdą z tych par jako klasę xSignal, przy czym każda „noga” pary jest identyfikowana jako xSignal kontroler–złącze.

Po wybraniu USB 3.0 strona będzie zawierać ustawienie dla Matched Length Tolerance Within Diff Pair. Wprowadź odpowiednią wartość. Ta wartość jest używana w regule projektowej utworzonej przez Kreator i może zostać zmieniona w dowolnym momencie w PCB Rules and Constraints Editor. Ustawienia zdefiniowane przez użytkownika, takie jak to, są zapisywane do przyszłego użycia.

Dla USB 3.0 każdy port użytkownika USB jest określany jako channel. Jak widać na obrazie, każdy kanał zawiera trzy pary różnicowe: Transmit, Receive oraz Data.Dla USB 3.0 krytycznym wymaganiem projektowym trasowania jest dopasowanie długości ścieżek w obrębie każdej pary; dopasowanie długości pomiędzy parami nie jest tak krytyczne. Z uwagi na to wymaganie oraz fakt, że reguła Matched Length wymaga par różnicowych do sprawdzania długości w obrębie pary netów, Kreator sprawdzi definicje Differential Pair i automatycznie utworzy odpowiednie pary różnicowe, jeśli ich nie ma. Reguła Matched Length utworzona przez Kreator jest następnie skonfigurowana do sprawdzania dopasowania długości Within Differential Pair Length. Zwróć uwagę, że reguła jest skonfigurowana do porównywania długości „nóg” w obrębie pary dla całego xSignal; nie porównuje długości „nóg” w obrębie każdej pary różnicowej.

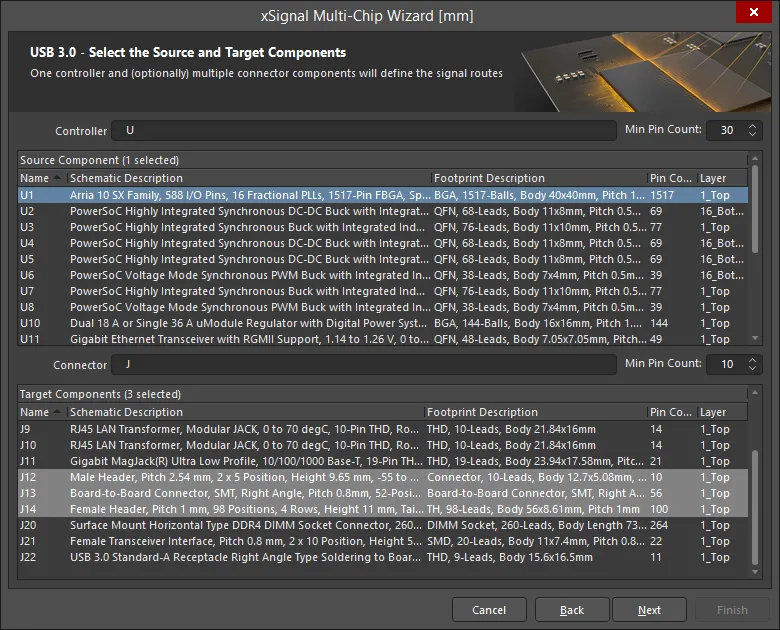

Wybór komponentów źródłowych i docelowych

Na tej stronie Kreator identyfikuje wszystkie potencjalne komponenty źródłowe i złącza docelowe na podstawie prefiksu oznaczenia (designator) oraz liczby pinów.

- Ustaw prefiks filtra dla oznaczenia Controller, oznaczenia Connector oraz wartości Min Pin Count zgodnie z potrzebami.

- Wybierz pojedynczy komponent źródłowy.

- Wybierz komponent(y) docelowy(e).

Jeśli wybierzesz wiele komponentów docelowych, w następnej stronie Kreatora powinieneś sprawdzić składnię nazewnictwa xSignal i netów dla każdego z tych komponentów, używając listy rozwijanej.

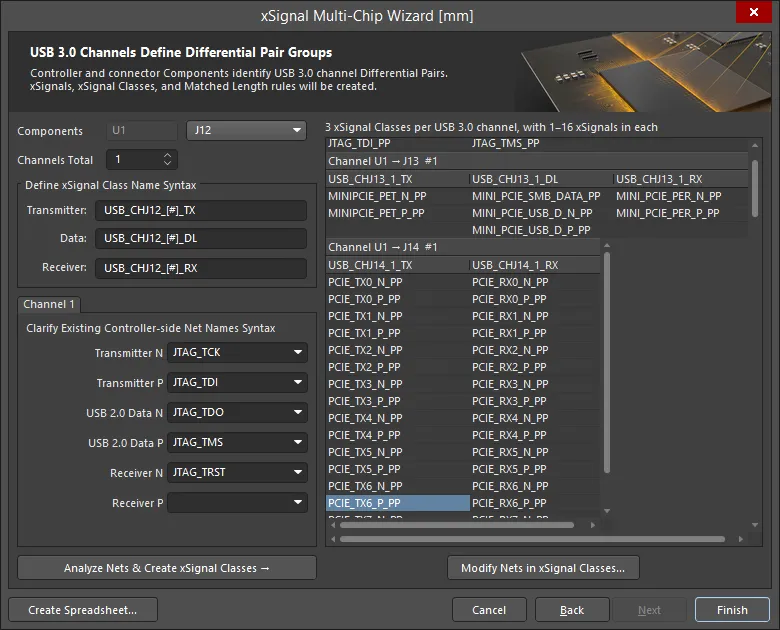

Kanały definiują grupy par różnicowych

Na tej stronie zdefiniuj składnię nazewnictwa, której Kreator może użyć do identyfikacji odpowiednich netów par: Transmitter, Receiver i Data, które następnie są uwzględniane w xSignals. Każda para xSignals jest następnie grupowana w klasę xSignal, a te klasy są używane do określenia zakresu reguły projektowej Matched Length.

Funkcjonalność tej strony jest następująca:

- Oznaczenie kontrolera jest wyświetlane obok etykiety Components. Obok tego lista rozwijana zawiera wszystkie Connectors wybrane na poprzedniej stronie Kreatora.

- Pokazane opcje składni nazewnictwa dotyczą każdego ze złączy wymienionych na liście rozwijanej. Wybieraj je kolejno i sprawdzaj, czy wybrana składnia nazewnictwa jest kompletna i odpowiednia.

- Jak wspomniano, dla USB 3.0 każdy port użytkownika USB jest określany jako channel. Możesz ustawić liczbę kanałów (Channels Total) od 1 do 32. Zwykle każde złącze ma pojedynczy kanał.

- W obrębie każdego kanału USB 3.0 istnieją trzy ścieżki par różnicowych: Transmit, Receive i Data, które biegną od kontrolera do złącza. Kreator utworzy xSignal, obejmujący w razie potrzeby elementy szeregowe, dla każdego netu dodatniego oraz kolejny xSignal dla każdego netu ujemnego, a następnie klasę xSignal reprezentującą tę parę kontroler–złącze. Grupa Define xSignal Class Name Syntax służy do określenia nazw tych klas xSignal. Kreator tworzy również odpowiednie pary różnicowe, jeśli nie są jeszcze zdefiniowane.

- Define xSignal Class Name Syntax – utworzone klasy xSignal będą nazwane zgodnie z podanymi ustawieniami, przy czym każdemu kanałowi zostanie przypisana wartość numeryczna w miejsce

[#]. Wprowadź preferowany ciąg znaków zgodnie z potrzebami.

- Channel <N> – te pola definiują maski używane do identyfikacji odpowiednich nazw netów Transmitter / Receiver / Data.

- Kreator ma duży szablon predefiniowanych schematów nazewnictwa, które sprawdza i zazwyczaj automatycznie wypełnia te pola. Jeśli tego nie zrobi, wybierz poprawną nazwę z listy rozwijanej lub wpisz odpowiednią składnię nazwy netu.

- Po skonfigurowaniu pól nazewnictwa kliknij przycisk Analyze Nets & Create xSignal Classes.

- Kreator utworzy xSignals, klasy xSignal oraz reguły Matched Length dla wszystkich kanałów. Zwróć uwagę, że są one tworzone za każdym razem, gdy ponownie uruchamiasz Kreator. Usuń je, jeśli planujesz uruchomić Kreator ponownie.

- Wynikowe nazwy klas xSignal oraz należące do nich xSignals są wyszczególnione w siatce.

- Kliknij przycisk Create Spreadsheet, aby wygenerować arkusz kalkulacyjny w formacie XLS z xSignals utworzonymi przez Kreator.

- Kliknij Finish, aby zakończyć działanie Kreatora.

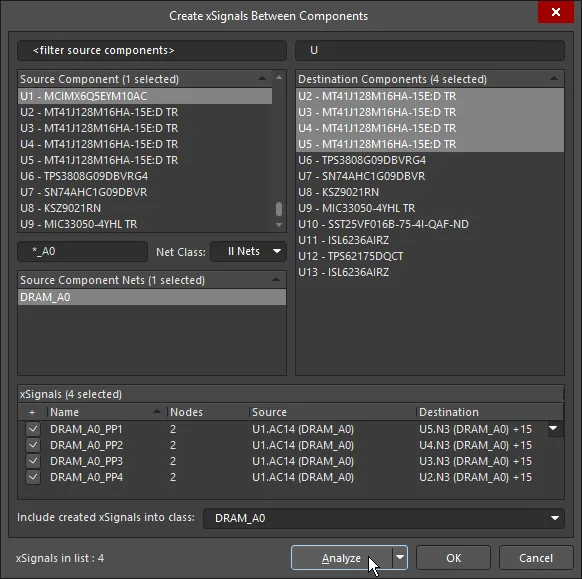

Okno dialogowe Create xSignals Between Components

Jeśli masz dużą liczbę xSignals do zdefiniowania, bardziej efektywne jest użycie okna dialogowego Create xSignals Between Components. Dostępne poprzez polecenie Design » xSignals » Create xSignals, okno dialogowe prezentuje komponenty źródłowe i docelowe oraz umożliwia utworzenie jednego lub wielu xSignals w ramach jednej operacji.

Użyj tego okna dialogowego, aby szybko zidentyfikować i utworzyć wiele xSignals oraz dodać je do wymaganej klasy xSignal.

Podejście jest następujące:

- Wybierz pojedynczy Source Component.

- Wybierz jeden lub więcej wymaganych Destination Components.Wybierz interesujący Source Net(s). Zostaną wyświetlone wszystkie nety aktualnie podłączone do wybranego komponentu źródłowego. Dla netów powiązanych z określoną klasą wybierz tę klasę z listy rozwijanej Net Class.

- Kliknij przycisk Analyze. Oprogramowanie próbuje zidentyfikować potencjalne xSignals istniejące pomiędzy wybranymi komponentami źródłowymi i docelowymi dla wybranych netów. Wszystkie możliwe xSignals, które obejmują wybrane nety i biegną pomiędzy wybranymi komponentami źródłowymi i docelowymi, zostaną wyświetlone w polu xSignals. Zwróć uwagę, że algorytm analizy podąża za bieżącą topologią wybranych netów, co będzie wpływać na proponowane xSignals.

Oprogramowanie może również, w razie potrzeby, przeszukiwać komponenty szeregowe, wybierając odpowiednią opcję z listy rozwijanej Analyze : Search for direct connections, Through 1 series component, Through 2 series components lub Multipath coupled nets.

- Po wykonaniu analizy potencjalne xSignals zostaną wyświetlone w dolnej części okna dialogowego i wszystkie będą włączone do utworzenia. Dokładnie sprawdź listę proponowanych xSignals i włącz tylko te, które są wymagane. Użyj poleceń dostępnych w menu kontekstowym po kliknięciu prawym przyciskiem myszy, aby przełączać wiele pozycji.

- Wybierz wymaganą class na dole okna dialogowego lub wpisz nazwę, aby utworzyć nową klasę. Jeśli nie zostanie wybrana żadna klasa, xSignals i tak zostaną utworzone i będzie można dodać je do dowolnej klasy xSignal w oknie dialogowym Object Class Explorer (Design » Classes). Korzystanie z klas może znacznie uprościć tworzenie i konfigurację reguł projektowych.

- Kliknij OK, aby utworzyć xSignals.

Okno dialogowe zostanie zamknięte i wrócisz do obszaru projektu. Nowe xSignals będą widoczne w trybie xSignals panelu PCB.

Użyj filtrów nad każdą listą, aby szybko znaleźć interesujące komponenty lub sieci; obsługiwane są symbole wieloznaczne.

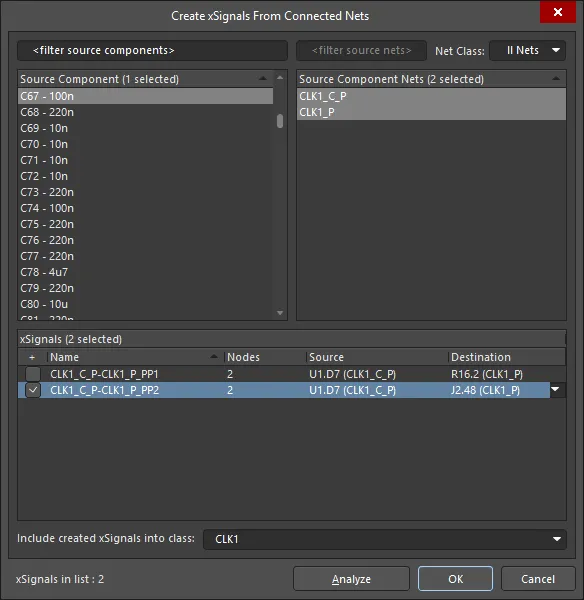

Okno dialogowe Create xSignals From Connected Nets

Jeśli tworzysz xSignals obejmujące szeregowe elementy terminujące, dobrym podejściem jest użycie polecenia Create xSignals from connected nets. Polecenie jest dostępne zawsze, gdy zaznaczony jest komponent — zarówno przez podmenu Design » xSignals w menu głównym, jak i podmenu xSignals po kliknięciu prawym przyciskiem myszy.

To polecenie służy do budowania xSignals „na zewnątrz” od wybranego szeregowego elementu terminującego, takiego jak rezystor lub kondensator. Obsługuje zarówno jeden lub więcej elementów dyskretnych, jak i jeden lub więcej komponentów typu „pack” z wieloma instancjami, np. sieci rezystorowe. Po uruchomieniu tego polecenia zostanie otwarte okno dialogowe Create xSignals From Connected Nets.

Użyj okna dialogowego, aby utworzyć xSignals przechodzące przez wybrany element szeregowy. W tym przykładzie zaproponowano dwa możliwe xSignals, ale zostanie utworzony tylko jeden.

Podejście jest następujące:

- Wybierz pojedynczy Source Component.

- Wybierz interesujące Source Net(s). Zostaną wyświetlone wszystkie sieci aktualnie podłączone do wybranego komponentu źródłowego. Dla sieci powiązanych z określoną klasą wybierz tę klasę z listy rozwijanej Net Class.

- Kliknij przycisk Analyze. Oprogramowanie próbuje zidentyfikować potencjalne xSignals istniejące dla wybranych komponentów źródłowych i ich wybranych sieci. Wszystkie możliwe xSignals zostaną wyświetlone w polu xSignals.

- Po wykonaniu analizy potencjalne xSignals zostaną wyświetlone w dolnej części okna dialogowego i wszystkie będą włączone do utworzenia. Dokładnie sprawdź listę proponowanych xSignals i włącz tylko te, które są wymagane. Użyj poleceń dostępnych w menu kontekstowym po kliknięciu prawym przyciskiem myszy, aby przełączać wiele pozycji.

- Wybierz wymaganą class na dole okna dialogowego lub wpisz nazwę, aby utworzyć nową klasę. Jeśli nie zostanie wybrana żadna klasa, xSignals i tak zostaną utworzone i będzie można dodać je do dowolnej klasy xSignal w oknie dialogowym Object Class Explorer (Design » Classes). Korzystanie z klas może znacznie uprościć tworzenie i konfigurację reguł projektowych.

- Kliknij OK, aby utworzyć xSignals.

Okno dialogowe zostanie zamknięte i wrócisz do obszaru projektu. Nowe xSignals będą widoczne w trybie xSignals panelu PCB.

Użyj filtrów nad każdą listą, aby szybko znaleźć interesujące komponenty lub sieci; obsługiwane są symbole wieloznaczne.

Rola topologii sieci

Gdy definiujesz xSignal, jest on pomiędzy dwoma węzłami lub padami. Jednak gdy wybierzesz ten xSignal w trybie xSignals panelu PCB, będzie on w rzeczywistości podążał ścieżką linii połączeń biegnących między tymi dwoma padami, wskazując, że jest to ścieżka, którą oprogramowanie zakłada jako trasę prowadzenia xSignal. Dzieje się tak, ponieważ respektowana jest topologia zdefiniowana dla tej sieci. Topologia sieci jest definiowana przez odpowiednią regułę projektową Routing Topology; domyślna topologia to Shortest.

Prosta animacja pokazuje CPU połączony z czterema kośćmi pamięci DDR3, które będą prowadzone strategią fly-by. Klasa xSignal DRAM_A2 zawiera cztery xSignals. Najpierw wybierana jest klasa, a następnie kolejno każdy xSignal. Widać, jak ścieżka xSignal podąża za topologią sieci, która jest obecnie ustawiona na domyślną — Shortest.

Ponieważ topologia sieci jest obecnie ustawiona na Shortest, xSignals nie podążają wymaganą ścieżką od procesora do kości pamięci.

Jeśli planujesz używać okna dialogowego Create xSignals Between Components, musisz skonfigurować topologię sieci, aby algorytm analizy xSignal rozumiał zamierzoną ścieżkę prowadzenia xSignal.

Polecenia tworzenia xSignal

Poza poleceniem Design » xSignals » Create xSignals istnieją inne polecenia tworzenia xSignal w podmenu xSignals, gdy spełnione są określone warunki.

Poniżej znajduje się podsumowanie poleceń i sytuacji, w których są dostępne:

| Polecenie |

Opis |

| Create xSignal from selected pins |

Natychmiast tworzy pojedynczy xSignal. To polecenie jest dostępne, gdy w obszarze projektu zaznaczone są co najmniej dwa pady, i jest tym samym poleceniem, które pojawia się po kliknięciu prawym przyciskiem myszy na jednym z zaznaczonych padów.

|

| Create xSignals between components |

To polecenie jest dostępne, gdy w obszarze projektu zaznaczone są komponenty. Po uruchomieniu otwiera się okno dialogowe Create xSignals Between Components z wstępnie zaznaczonymi komponentami. Upewnij się, że wybrane są właściwe komponenty Source i Designation, a następnie dokończ proces analizy/tworzenia.

Po uruchomieniu polecenia zostanie otwarte okno dialogowe Create xSignals Between Components dialog. Użyj go do utworzenia xSignals w następujący sposób:

- Wybrany komponent źródłowy będzie zaznaczony w obszarze Source Component.

- Wszelkie inne komponenty zaznaczone w obszarze roboczym będą zaznaczone w obszarze Destination Components. Jeśli nie, dokonaj wyboru teraz.

- Domyślnie zaznaczone będą wszystkie sieci powiązane z padami komponentu źródłowego (w obszarze Source Component Nets). Dostosuj ten wybór w razie potrzeby.

-

Kliknij przycisk Analyze — oprogramowanie spróbuje zidentyfikować potencjalne xSignals istniejące pomiędzy wybranymi komponentami źródłowymi i docelowymi dla zaznaczonych sieci.

Zwróć uwagę, że algorytm analizy podąża za bieżącą topologią wybranych sieci.

Oprogramowanie może również, w razie potrzeby, przeszukiwać komponenty szeregowe, wybierając odpowiedni tryb z listy rozwijanej powiązanej z przyciskiem. Dostępne tryby to: Search for direct connections, Through 1 series component, Through 2 series components i Multipath coupled nets.

- Wszystkie zidentyfikowane xSignals są wyświetlane w obszarze xSignals okna dialogowego. Domyślnie wszystkie są zaznaczone do utworzenia — dostosuj to w razie potrzeby.

- Opcjonalnie możesz powiązać utworzone xSignals z klasą xSignal. Wybierz istniejącą klasę xSignal albo wpisz nazwę nowej klasy. Jeśli chcesz, możesz pozostawić to pole puste; xSignals zawsze można później dodać jako członków do wymaganej klasy.

- Kliknij OK , aby utworzyć xSignals. Okno dialogowe zostanie zamknięte i wrócisz do obszaru projektu, który pokaże przefiltrowany widok z nowo utworzonymi xSignals. Jeśli wskazano klasę xSignal, zostanie ona utworzona (jeśli nie istniała) i xSignals zostaną z nią powiązane.

|

| Create xSignals from connected nets |

Użyj tego polecenia, gdy istnieje jeden lub więcej szeregowych elementów terminujących, dla których chcesz utworzyć xSignals. Zaznacz komponent(y) terminujące, a następnie uruchom polecenie, aby otworzyć okno dialogowe Create xSignals from Connected Nets, gotowe do dokończenia procesu tworzenia zestawu xSignals. Użyj okna dialogowego do utworzenia xSignals w następujący sposób:

- Wybrane komponenty źródłowe będą zaznaczone w obszarze Source Component.Domyślnie zaznaczone będą wszystkie sieci powiązane z padami komponentów źródłowych (w obszarze Source Component Nets). Dostosuj ten wybór w razie potrzeby.

-

Kliknij przycisk Analyze — oprogramowanie spróbuje zidentyfikować potencjalne xSignals istniejące dla zaznaczonych sieci wychodzących z wybranych komponentów.

Zwróć uwagę, że algorytm analizy podąża za bieżącą topologią wybranych sieci.

- Wszystkie zidentyfikowane xSignals są wyświetlane w obszarze xSignals okna dialogowego. Domyślnie wszystkie są zaznaczone do utworzenia — dostosuj to w razie potrzeby.Opcjonalnie możesz powiązać utworzone xSignals z klasą xSignal. Wybierz istniejącą klasę xSignal albo wpisz nazwę nowej klasy. Jeśli chcesz, możesz pozostawić to pole puste; xSignals zawsze można później dodać jako członków do wymaganej klasy.

- Kliknij OK , aby utworzyć xSignals. Okno dialogowe zostanie zamknięte i wrócisz do obszaru projektu, który pokaże przefiltrowany widok z nowo utworzonymi xSignals. Jeśli wskazano klasę xSignal, zostanie ona utworzona (jeśli nie istniała) i xSignals zostaną z nią powiązane.

|

| Create xSignals |

Otwiera okno dialogowe Create xSignals Between Components. To polecenie jest zawsze dostępne. Użyj okna dialogowego do utworzenia xSignals w następujący sposób:

- Wybierz komponent źródłowy w obszarze Source Component.Wybierz jeden lub więcej komponentów docelowych w obszarze Destination Components.

- W obszarze Source Component Nets zostaną wyświetlone wszystkie sieci powiązane z padami komponentu źródłowego. Wybierz interesujące sieci.

-

Kliknij przycisk Analyze — oprogramowanie spróbuje zidentyfikować potencjalne xSignals istniejące pomiędzy wybranymi komponentami źródłowymi i docelowymi dla zaznaczonych sieci.

Zwróć uwagę, że algorytm analizy podąża za bieżącą topologią wybranych sieci.

Oprogramowanie może również przeszukiwać komponenty szeregowe, jeśli jest to wymagane, wybierając odpowiedni tryb z powiązanego z przyciskiem menu rozwijanego. Dostępne tryby to: Search for direct connections, Through 1 series component, Through 2 series components i Multipath coupled nets.

- Wszystkie zidentyfikowane xSignals są wyświetlane w obszarze xSignals okna dialogowego. Domyślnie wszystkie są zaznaczone do utworzenia — w razie potrzeby dostosuj to ustawienie.

- Opcjonalnie możesz powiązać utworzone xSignals z klasą xSignal. Wybierz istniejącą klasę xSignal albo wprowadź nazwę nowej klasy. Jeśli chcesz, możesz pozostawić to pole puste; xSignals zawsze można później dodać jako członków do wymaganej klasy.

- Kliknij OK , aby utworzyć xSignals. Okno dialogowe zostanie zamknięte i nastąpi powrót do przestrzeni projektowej, która pokaże przefiltrowany widok z nowo utworzonymi xSignals. Jeśli określono klasę xSignal, zostanie ona utworzona (jeśli nie istniała) i xSignals zostaną z nią powiązane.

|

Definiowanie punktu rozgałęzienia w zbalansowanym układzie T

Jednym z wyzwań strategii prowadzenia ścieżek Balanced T jest wyrównanie długości pni oraz gałęzi za punktami T. Dostępne węzły w sieci znajdują się wyłącznie na padach, więc nie da się zdefiniować osobnych xSignals dla pnia oraz od punktu rozgałęzienia do końca każdej gałęzi. Punkty rozgałęzienia są oznaczone czerwonymi kropkami na poniższym obrazie.

Jednym ze sposobów rozwiązania tego problemu jest dodanie do sieci komponentu z pojedynczym pinem. Utwórz komponent z pojedynczym padem o rozmiarze przelotek używanych w projekcie. Jeśli pad komponentu punktu rozgałęzienia jest jednokwarstwowy, można go także używać w połączeniu z przelotką ślepą lub zagrzebaną, umieszczając go na warstwie startowej lub końcowej przelotki, co daje pełną elastyczność w sposobie tworzenia prowadzenia. Jeśli chcesz uwzględnić komponent punktu rozgałęzienia tylko na PCB, ustaw Type komponentu punktu rozgałęzienia na Mechanical, aby wykluczyć go z BOM i zapobiec problemom z synchronizacją ze schematem. Jeśli planujesz uwzględnić komponent punktu rozgałęzienia na schemacie, właściwość Type komponentu można ustawić na Standard (no BOM).

Prowadzenie Balanced T może wymagać dopasowanych długości pomiędzy pośrednimi punktami rozgałęzienia.

Ponieważ punkt rozgałęzienia jest węzłem w sieci, możesz teraz definiować xSignals tylko dla pnia, dla każdej głównej gałęzi oraz — w razie potrzeby — dla każdej gałęzi podrzędnej. Następnie można ich użyć do zawężenia zakresu reguł projektowych dopasowanej długości, dając projektantowi pełną kontrolę nad tym, jak precyzyjnie ma być wykonywane dopasowanie długości.

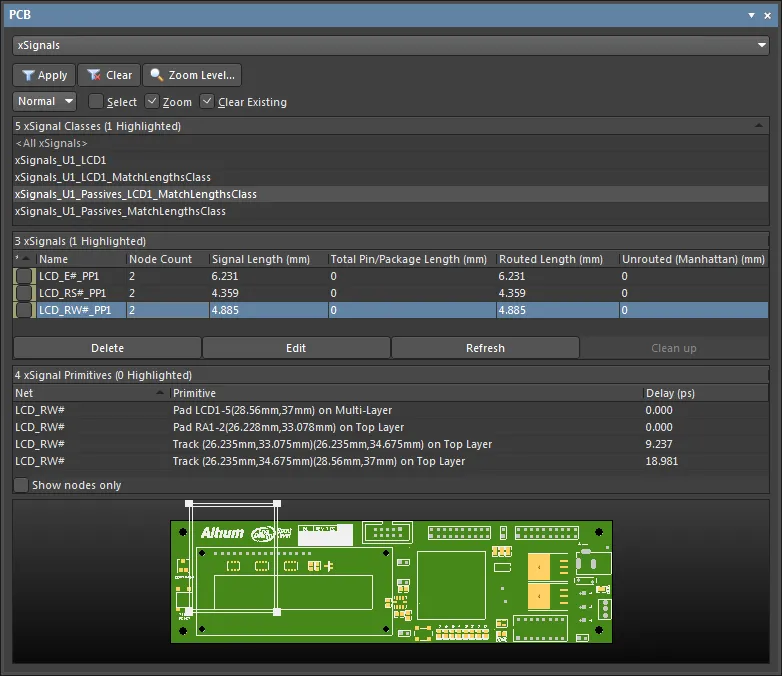

Zarządzanie xSignals

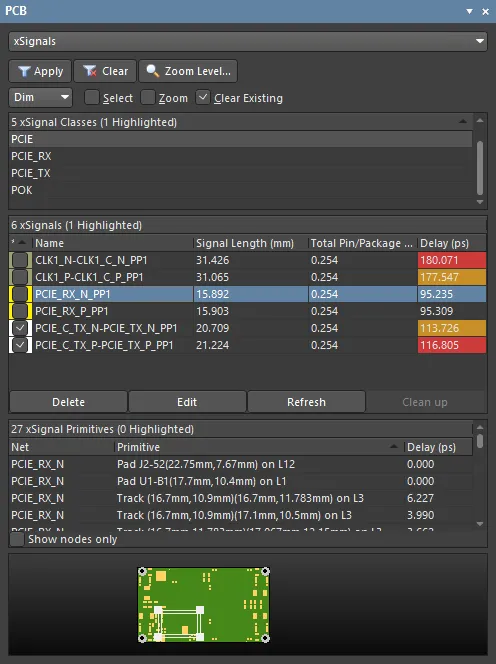

W trybie panelu PCB xSignals jego trzy główne obszary zmieniają się tak, aby odzwierciedlać hierarchię xSignal bieżącego projektu PCB (kolejno od góry):

- xSignal Classes

- Pojedyncze xSignals w obrębie klasy

- Pojedyncze xSignal Primitives, które składają się na xSignal (pady, ścieżki i przelotki)

Obszar klas xSignal

Obszar xSignal Classes wyświetla zdefiniowane kolekcje klas xSignal lub wszystkie dostępne klasy (<All xSignals>).

Wybierz klasę, aby zobaczyć listę jej xSignals w środkowym obszarze (xSignals) oraz wyświetlić je w przestrzeni projektowej PCB.

Aby utworzyć nową klasę xSignal z istniejącej kolekcji xSignal, kliknij prawym przyciskiem w obszarze, a następnie wybierz Add Class z menu kontekstowego, aby otworzyć okno Edit xSignal Class dialog. Okno dialogowe wyświetla dostępne xSignals, które można dodawać lub usuwać jako członków nowej klasy za pomocą przycisków zarządzania. Użyj pola Name, aby zdefiniować odpowiednią nazwę nowej klasy xSignal.

Utwórz klasę xSignal lub dodaj do niej elementy, dodając/usuwając członków xSignal w oknie Edit xSignal Class.

Menu kontekstowe (prawy przycisk) obszaru panelu oferuje także możliwość usunięcia (Delete) lub zmiany reprezentacji wizualnej w przestrzeni projektowej PCB (na przykład Change xSignal Color).

Obszar xSignals

Środkowy obszar panelu wyświetla xSignals z klas xSignal wybranych w obszarze powyżej.

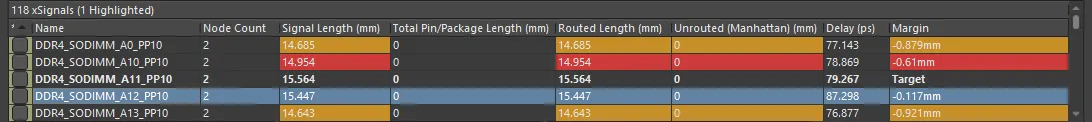

Domyślnie przy każdym xSignal wyświetlane są następujące informacje:

-

– ta funkcja ma dwa zastosowania:

– ta funkcja ma dwa zastosowania:

- kolor tła – kolor przypisany do xSignal (cienka linia reprezentująca xSignal w przestrzeni projektowej). Kliknij prawym przyciskiem, aby Change xSignal Color dla wszystkich aktualnie zaznaczonych xSignals.

- pole wyboru widoczności – użyj go, aby zawsze wyświetlać xSignal niezależnie od tego, czy jest aktualnie zaznaczony, czy nie.

- Name – nazwa xSignal.

- Node Count – łączna liczba padów w tym xSignal.

- Routed Length – suma długości umieszczonych segmentów ścieżek i łuków tworzących prowadzenie plus pionowa odległość pokonywana przez przelotki (patrz uwaga poniżej). Kalkulator długości prowadzenia nie próbuje rozwiązywać nakładających się segmentów ścieżek ani „falowania” prowadzenia wewnątrz padów.

- Signal Length – dokładne obliczenie całkowitej odległości węzeł–węzeł. Do obliczeń długości sygnału mają zastosowanie następujące uwagi:

- Total Pin/Package Length – suma wszystkich wartości Pin Package Length we wszystkich padach w tym xSignal. Wartość ta jest zdefiniowana jako właściwość pada PCB i może być również określona w pinie schematu.

- Unrouted (Manhattan) Length – pionowa plus pozioma (X+Y) odległość wszystkich niepoprowadzonych odcinków.

- Margin – różnica między rzeczywistą długością sygnału a docelową długością sygnału zdefiniowaną przez obowiązujące reguły projektowe Length/Matched Length.

Kliknij prawym przyciskiem w obszarze, a następnie użyj podmenu Columns, aby dodać następującą kolumnę:

- Delay – czas potrzebny na propagację sygnału wzdłuż tej trasy.

Użyj podmenu Columns, aby pokazać/ukryć kolumny.

Vertical distance through a via – pionowa odległość, jaką sygnał pokonuje przez przelotkę, to suma grubości wszystkich warstw (miedź i dielektryk) pomiędzy warstwami miedzi startową i końcową, plus połowa grubości warstwy startowej i połowa grubości warstwy końcowej. Grubości warstw są definiowane w

Layer Stack.

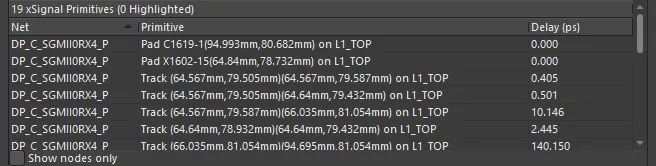

Obszar prymitywów xSignal

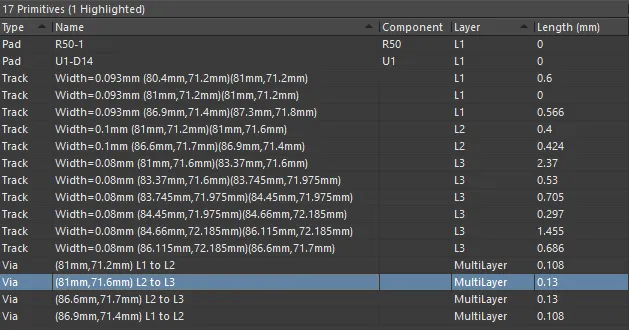

Trzeci obszar panelu PCB, xSignal Primitives, wyświetla wszystkie elementy składowe (prymitywy) aktualnie wybranego xSignal.

Zaznacz pole wyboru Show nodes only w tym obszarze, aby ograniczyć listę prymitywów do padów będących węzłami punktu startowego/końcowego xSignal. W tym trybie wybrany xSignal będzie pokazany w przestrzeni projektowej PCB jako pady-węzły połączone cienkim śladem (zamiast ścieżek), który reprezentuje przebieg xSignal.

Dolny obszar xSignal Primitives wyświetla wszystkie elementy wybranego xSignal, takie jak pady, przelotki i ścieżki, oraz odpowiadające im opóźnienie.

Wyświetlanie xSignals w przestrzeni projektowej

xSignals są wyświetlane w przestrzeni projektowej jako cienka linia. Linia wskazuje ścieżkę, którą podąża xSignal. Całkowita długość linii stanowi składową X/Y długości sygnału tego xSignal. Składowa Z, czyli pionowy wkład do całkowitej długości sygnału, została opisana powyżej.

Na poniższym obrazie pokazano xSignals dla pary różnicowej. xSignal dla niezaznaczonego członka pary pozostaje widoczny, ponieważ pole wyboru dla tego xSignal jest włączone w panelu.

xSignals są reprezentowane w przestrzeni projektowej przez cienką linię. Oba xSignals w tej parze różnicowej pozostają widoczne, mimo że w panelu zaznaczony jest tylko jeden, ponieważ pole wyboru widoczności jest włączone.

Usuwanie xSignal

Wybierz xSignal w panelu, a następnie kliknij przycisk Delete poniżej listy xSignals. Alternatywnie kliknij prawym przyciskiem i wybierz Delete z menu kontekstowego albo naciśnij Delete na klawiaturze.

Słowa kluczowe zapytań xSignal

Edytor PCB zawiera potężny i zaawansowany filtering engine. Ten silnik jest używany do identyfikowania obiektów podczas wyszukiwania obiektów w przestrzeni projektowej, stosowania reguł w trakcie interaktywnych i automatycznych zadań projektowych oraz do sprawdzania zgodności z regułami. Projektant informuje silnik filtrowania, które obiekty go interesują, pisząc zapytanie z użyciem słów kluczowych rozpoznawanych przez silnik filtrowania.

Dodano następujące słowa kluczowe zapytań typu xSignal do użycia w regułach projektowych i filtrach przestrzeni projektowej:

Słowa kluczowe typu sprawdzania członkostwa

- InxSignal - Czy obiekt należy do określonego xSignal, np.

InxSignal('DRAM_A0_PP1')

- InxSignalClass - Czy obiekt należy do określonej klasy xSignal, np.

InxSignalClass('PCIE')

- IsxSignal - Czy obiekt jest xSignal o określonej nazwie, np.

IsxSignal('DRAM_A0_PP1')

Słowa kluczowe typu sprawdzania atrybutów

- InAnyxSignal - Czy obiekt należy do dowolnego xSignal, np.

InAnyxSignal

Obsługa xSignals w regułach projektowych

Reguły projektowe to sposób, w jaki przekładasz swoje wymagania na zestaw instrukcji, które edytor PCB potrafi zrozumieć i egzekwować. Reguły mogą być sprawdzane podczas rozmieszczania obiektów (Online DRC) lub jako proces końcowy (Batch DRC). xSignals mogą być używane do zdefiniowania obiektów, do których ma zostać zastosowana reguła projektowa.

► Dowiedz się więcej o Design Rules

► Dowiedz się więcej o Length Tuning

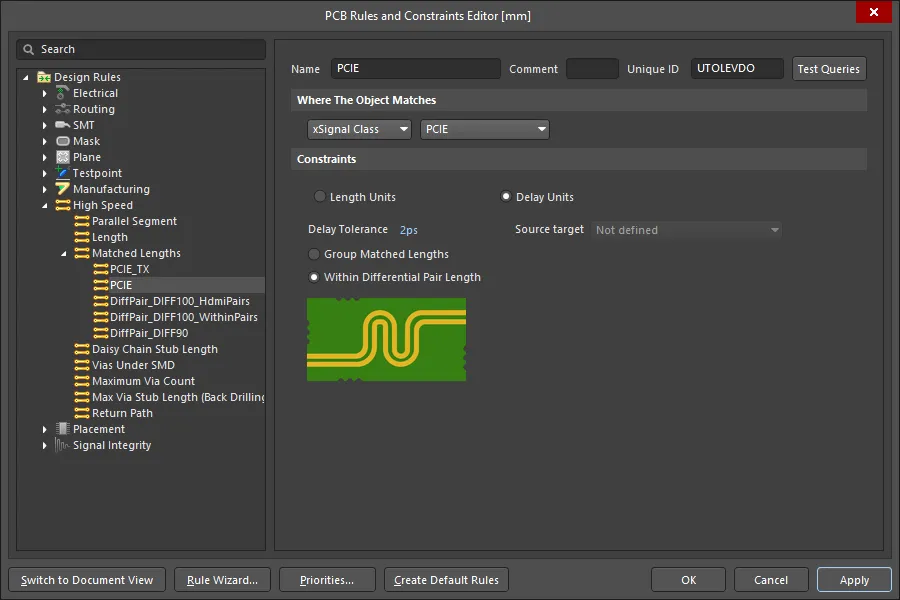

Reguła Matched Length

Reguła projektowa Matched Length służy do zapewnienia, że długość wskazanych sieci mieści się w określonym zakresie. Reguła ta jest kluczowa w projektach wysokich prędkości, gdzie wyzwaniem nie jest wyłącznie to, jak długo sygnały docierają do celu (co wynika z ich całkowitej długości), lecz to, jak istotne jest, aby wskazane sygnały dotarły w tym samym czasie. W zależności od szybkości przełączania sygnału, funkcji sygnału oraz materiałów użytych w płytce, dopuszczalna różnica może wynosić nawet 500 mils albo zaledwie 1 mil.

Na poniższym obrazie pokazano przykład reguły Matched Length skonfigurowanej tak, aby obejmowała xSignals w klasie xSignal PCIE, oraz sprawdzała różnicę długości w obrębie każdej pary różnicowej w tej klasie xSignals. Każda para w klasie musi mieć długości poprowadzonych ścieżek, które skutkują Delay Tolerance nie większym niż 2ps opóźnieniem pomiędzy dwiema sieciami w tej parze.

Zwróć uwagę, że ograniczenia (Constraints) reguły Matched Length wymagają wyboru pomiędzy dopasowaniem długości wszystkich sieci objętych regułą (Group Matched Lengths) a dopasowaniem dwóch sieci w obrębie każdej pary różnicowej w sieciach objętych regułą.

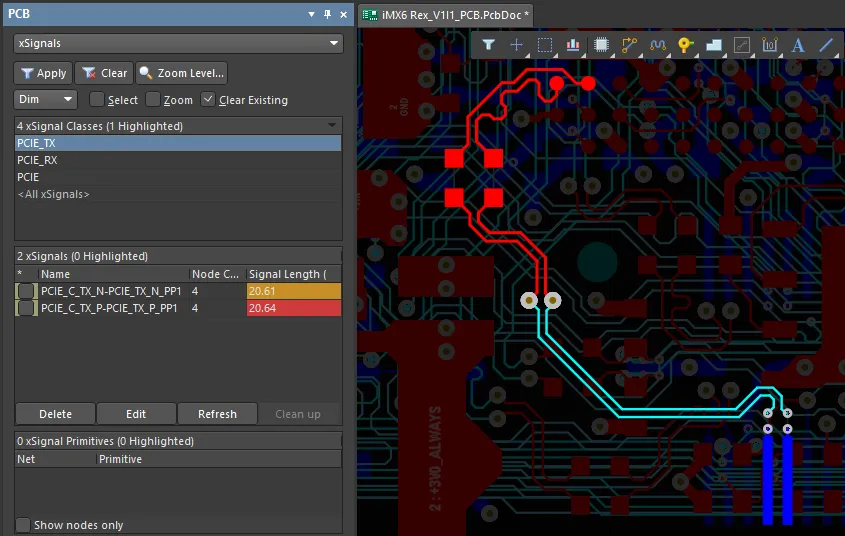

Poniższy obraz pokazuje klasę xSignal PCIE_TX wybraną w panelu oraz te xSignals zaznaczone w obszarze projektu.

Oprócz klasy PCIE zdefiniowane są także klasy dla par TX i RX. Zwróć uwagę, że jeden z xSignals TX nie spełnia odpowiedniej reguły dopasowania długości. ##

Jeśli planujesz strojenie długości (length tuning) xSignals, które obejmują pojedyncze sieci oraz pary różnicowe, utwórz następujące reguły:

- Regułę matched length, która definiuje wymagania dopasowania długości between nets and differential pairs in xSignals. Aby skonfigurować regułę tak, by testowała długość jednej sieci/pary względem długości innej sieci/pary, włącz opcję Group Matched Lengths .

- Drugą regułę matched length o wyższym priorytecie, która definiuje wymagania dopasowania długości within-pair . Aby skonfigurować regułę tak, by testowała długość jednego członu pary względem drugiego członu pary, włącz opcję Within Differential Pair Length .

Dobrą metodą strojenia długości takich xSignals jest:

- Poprowadź sieci i pary różnicowe xSignal.

- Wystrojenie długości pojedynczych sieci za pomocą polecenia Interactive Length Tuning .

- Wystrojenie długości between par za pomocą polecenia Interactive Differential Pair Length Tuning . Strojenie długości wykorzystuje najdłuższą długość sygnału w najdłuższej parze jako Target Length i dostraja najdłuższą sieć w parze do tej długości.

- Wystrojenie krótszej sieci within w każdej parze względem drugiej sieci w parze za pomocą polecenia Interactive Length Tuning .

- Teraz możesz użyć panelu PCB Rules and Violations , aby sprawdzić regułę/reguły within-pair Matched Net Length. Aby to zrobić, wybierz Matched Net Lengths w sekcji Rule Classes panelu, następnie kliknij prawym przyciskiem myszy wymaganą regułę Matched Length i wybierz polecenie Run DRC Rule <RuleName> z menu kontekstowego. W razie potrzeby dostosuj „akordeony” strojenia dla pojedynczych sieci.

- Następnie użyj panelu PCB Rules and Violations , aby sprawdzić regułę/reguły between-pair Matched Net Length, korzystając z właśnie opisanego procesu. W razie potrzeby dostosuj „akordeony” strojenia par różnicowych.

Reguła Length

Reguła projektowa Length służy do zapewnienia, że całkowita długość poprowadzenia mieści się w określonym zakresie. Reguła ta jest zwykle używana, aby upewnić się, że docelowe sieci nie są dłuższe niż określona długość — na przykład po to, by spełnić wymagania czasowe układu. Reguła Length respektuje zapytania (queries) typu xSignal wymienione powyżej.

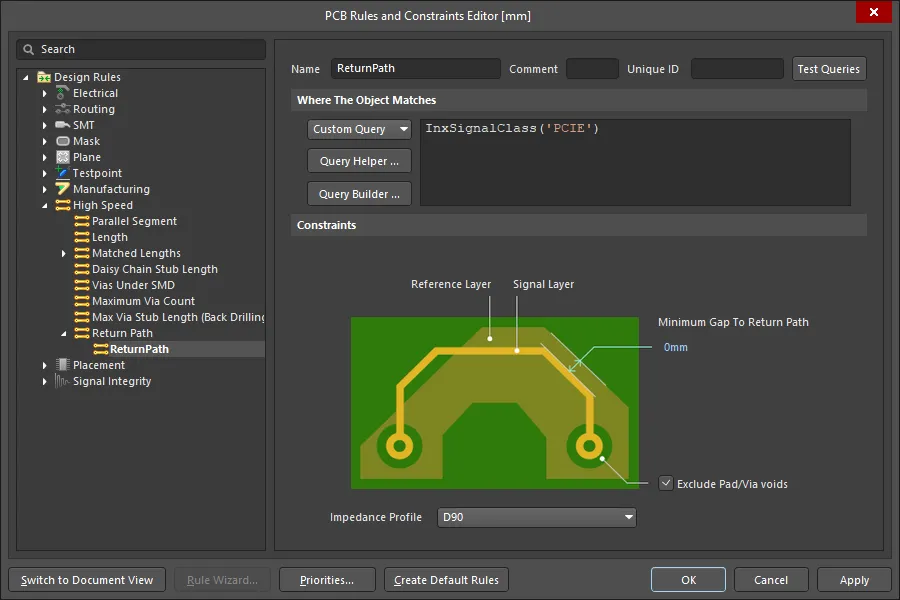

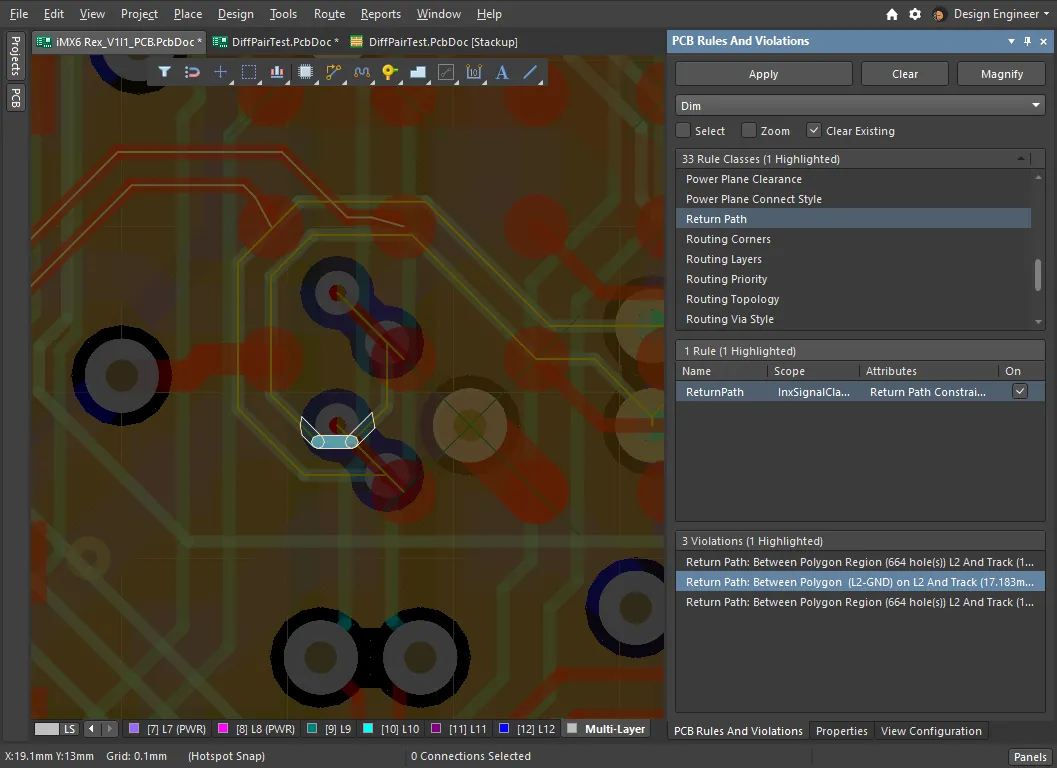

Reguła Return Path

Reguła projektowa Return Path sprawdza, czy istnieje ciągła ścieżka powrotu prądu sygnału na wskazanej warstwie odniesienia (reference layer) powyżej lub poniżej sygnałów objętych regułą. Ścieżka powrotu może być utworzona z wypełnień (fills), regionów (regions) i polygon pours umieszczonych na warstwie sygnałowej albo może to być warstwa plane.

Warstwy ścieżki powrotu to warstwy odniesienia zdefiniowane w wybranym profilu impedancji (Impedance Profile). Dodaj nową regułę Return Path w kategorii reguł High Speed.

Poniższy obraz pokazuje naruszenie reguły Return Path, gdzie polygon ścieżki powrotu xSignal ma otwór, przez który przechodzi przelotka (via).

Użycie panelu PCB Rules and Violations do zlokalizowania naruszenia reguły Return Path. ##

Użycie panelu PCB Rules and Violations do zlokalizowania naruszenia reguły Return Path. ##

Dokładne obliczenia długości

Kluczowym wymaganiem przy definiowaniu reguł dla projektów wysokich prędkości jest dokładne obliczanie długości tras. Tradycyjne podejście do obliczania długości sygnału polega na zsumowaniu długości linii środkowej (centerline) wszystkich segmentów użytych w trasie, a także odległości pionowej wynikającej z wysokości przelotek, która pierwotnie była wyznaczana na podstawie grubości płytki.

To podejście nie jest wystarczające dla projektu wysokich prędkości z wielu powodów, m.in.:

- Obiekty ułożone warstwowo i nakładające się — algorytm, który po prostu sumuje długości linii środkowej wszystkich obiektów w sieci, nie uwzględnia obiektów ułożonych warstwowo ani nakładających się.

- „Wędrująca” ścieżka wewnątrz obiektu — często występują obiekty trasowania całkowicie wewnątrz pada lub przelotki, co może fałszywie zwiększać długość, jak pokazano na pierwszym obrazie poniżej. Drugi obraz pokazuje poprawny sposób obliczania długości, gdy obiekt fill jest częścią trasowania.

- Długość via — przelotki blind i buried nie przechodzą przez wszystkie warstwy płytki, więc sama grubość płytki nie jest wystarczająco dokładna do wyznaczenia długości pionowej. Należy użyć rzeczywistej wysokości via, uwzględniając grubości miedzi i izolacji, przez które via przechodzi.

Kalkulator długości w edytorze PCB zwraca możliwie najdokładniejszą długość trasy.

Obliczenie długości jest wykonywane dokładnie wzdłuż linii środkowej najkrótszej ścieżki, jak pokazano na tych dwóch obrazach.

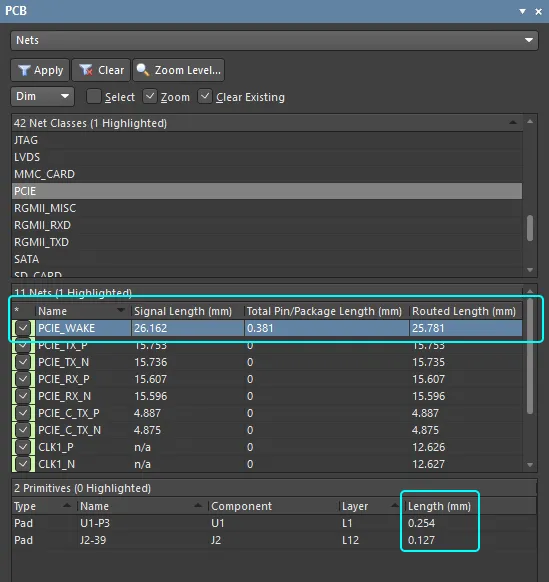

Dla przelotek obliczane są dokładne długości, na podstawie warstw, przez które przechodzą, oraz wymiarów stackupu. Obraz z panelu PCB w trybie Nets.

Opóźnienie pin-package

W każdym projekcie wysokich prędkości powyżej 500 MHz medium połączeniowe, czyli bond wire do struktury (die), wprowadza opóźnienie sygnału. To opóźnienie wewnątrz elementu nazywa się opóźnieniem pin-package (pin-package delay). Nawet jeśli dwa układy są w pełni zgodne pinowo z punktu widzenia projektu i PCB, czasy przelotu w obudowie (package flight times) będą się różnić między różnymi układami, więc trzeba je uwzględnić. Informacje o czasie przelotu można znaleźć w dokumencie IBIS 6 dla danego elementu. Informacje o Package Pins należy brać pod uwagę na etapie planowania I/O lub po syntezie w przypadku FPGA. Wszyscy producenci układów powinni być w stanie dostarczyć opóźnienia obudowy, które będą podane albo jako opóźnienie w pikosekundach, albo jako długość.

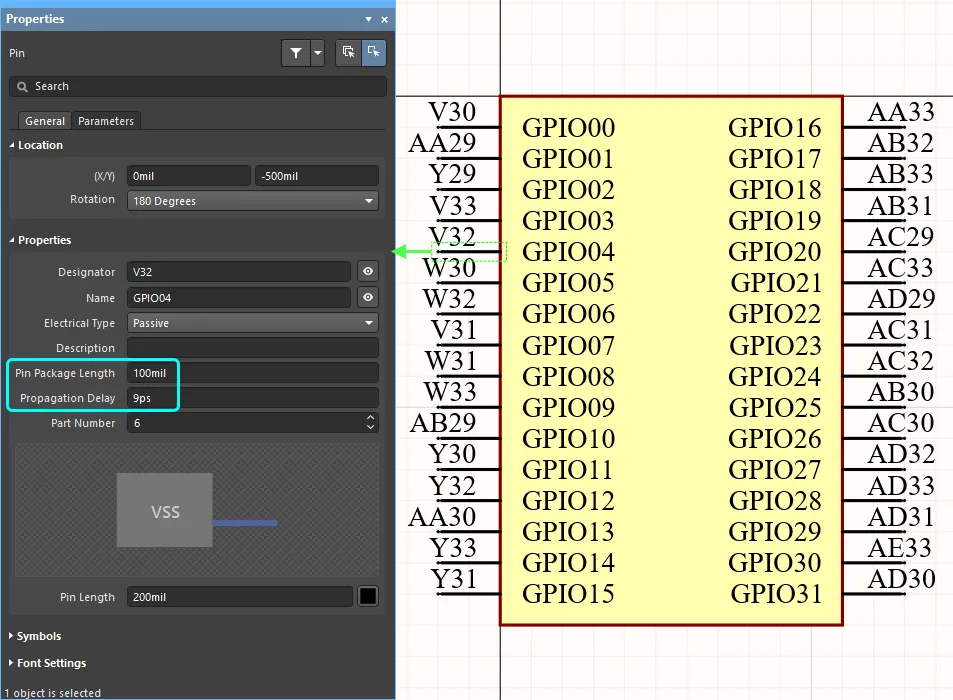

Opóźnienie można uwzględnić w projekcie jako Pin Package Length lub jako Propagation Delay, korzystając z odpowiednich pól dla pinu w edytorze schematu lub pada/via w edytorze PCB. Wprowadzone wartości są obsługiwane następująco:

Pin Package Length - wszystkie długości pin-package w obrębie każdej sieci są sumowane w edytorze PCB, dając Total Pin/Package Length, które jest uwzględniane w całkowitej Signal Length dla tej sieci. Zobacz tryb Nets panelu PCB, aby dowiedzieć się więcej o Signal Length.

Propagation Delay - wszystkie wartości opóźnienia zdefiniowane przez użytkownika dla pinów/padów i przelotek w każdej sieci są dodawane w edytorze PCB do opóźnienia trasowania (routing delay) dla tej sieci. Opóźnienie trasowania jest automatycznie obliczane przez solver pola Simbeor® wbudowany w Layer Stack Manager. Opóźnienia padów i przelotek nie są obliczane automatycznie, ale mogą być zdefiniowane przez użytkownika.

- Reguły Length i Matched Length mogą być konfigurowane w oparciu o Length lub Delay.

- Signal Length, Total Pin/Package Length oraz Delay mogą być wyświetlane w różnych trybach panelu PCB, w tym w trybie Nets mode, Differential Pairs Editor mode oraz xSignals mode. Kliknij prawym przyciskiem nagłówek kolumny w panelu PCB, aby włączyć/wyłączyć kolumny.

- Simbeor SFS (quasi-static field solver) firmy Simberian® jest używany do obliczania opóźnienia trasowania na podstawie właściwości fizycznych zdefiniowanych w Layer Stack Manager.

- Zdefiniowane przez użytkownika wartości Pin Package Length oraz Propagation Delay są od siebie niezależne; są dodawane do wartości Signal Length i Delay w sposób właśnie opisany. Ponieważ nie oddziałują na siebie, w razie potrzeby można podać obie wartości.

Uwzględnianie opóźnienia w schemacie

Długości pin-package mogą być zdefiniowane jako atrybut pinu komponentu na schemacie w panelu Properties w trybie Pin. Oprogramowanie domyślnie użyje jednostek dokumentu bazowego; w razie potrzeby wpisz jednostki wraz z wartością.

Wprowadź długość pin-package w wymaganych jednostkach.

- Właściwości pinów komponentu można także edytować w edytorze biblioteki lub na arkuszu schematu na karcie Pins panelu Properties w trybie Component. Kliknij

na tej karcie panelu, aby otworzyć Component Pin Editor, gdzie można edytować wszystkie właściwości wszystkich pinów w danym komponencie. Wartości można edytować bezpośrednio w siatce (zaznacz komórkę i wpisz nową wartość), a do przechodzenia do sąsiednich komórek można używać klawiszy kursora. Domyślne jednostki zostaną automatycznie dodane, jeśli nie zostaną wpisane.

na tej karcie panelu, aby otworzyć Component Pin Editor, gdzie można edytować wszystkie właściwości wszystkich pinów w danym komponencie. Wartości można edytować bezpośrednio w siatce (zaznacz komórkę i wpisz nową wartość), a do przechodzenia do sąsiednich komórek można używać klawiszy kursora. Domyślne jednostki zostaną automatycznie dodane, jeśli nie zostaną wpisane.

- Alternatywnie użyj panelu SCH List panel, aby skopiować/wkleić wiele wartości Pin/Pkg Lengths lub Propagation Delay z noty katalogowej do zestawu wybranych wyprowadzeń komponentu w edytorze biblioteki schematów (show image

![]() ). Oprócz wklejania zawartości schowka bezpośrednio do zaznaczonych komórek możesz także kliknąć prawym przyciskiem myszy w panelu, aby uzyskać dostęp do okna Smart Grid Paste dialog, co daje większą kontrolę nad procesem wprowadzania dodatkowych danych do pinów.

). Oprócz wklejania zawartości schowka bezpośrednio do zaznaczonych komórek możesz także kliknąć prawym przyciskiem myszy w panelu, aby uzyskać dostęp do okna Smart Grid Paste dialog, co daje większą kontrolę nad procesem wprowadzania dodatkowych danych do pinów.

Definiowanie opóźnienia w edytorze PCB

Wartości Pin Package Length oraz Propagation Delay są przenoszone do układu PCB — jak widać w trybie Pad panelu Properties.

Wartości Pin Package Length oraz Propagation Delay są przenoszone ze schematu do PCB, ale można je również zdefiniować bezpośrednio w PCB.

Sprawdzanie Pin/Package Length oraz Propagation Delay w panelu PCB

Wartość Pin/Pkg Length jest automatycznie uwzględniana w obliczeniach Signal Length, które są wyświetlane w różnych trybach panelu PCB. Ustaw panel w tryb Nets, aby sprawdzić (lub edytować) wartość Pin/Pkg Length dla pinów w wybranej sieci. Zwróć uwagę, że kolumna Routed Length odzwierciedla długość prowadzenia ścieżek, a kolumna Signal Length odzwierciedla długość prowadzenia ścieżek powiększoną o wszelkie Pin/Pkg Lengths w tej sieci.

Wartość Pin/Pkg Length i jej wpływ na Signal Length jest pokazany w trybie Nets panelu PCB.

Na poniższym obrazie kolumna propagacji Delay pokazuje, że są dwie pary xSignals, które nie spełniają reguły projektowej Matched Length. Ponieważ podświetlenie jest w kolumnie Delay, oznacza to, że reguła jest skonfigurowana do używania jednostek opóźnienia (Delay Units), a nie jednostek długości (Length Units).

Kolumna Delay pokazuje, że są dwie pary xSignals, które nie spełniają reguły projektowej Matched Length.

Kolumna Delay pokazuje, że są dwie pary xSignals, które nie spełniają reguły projektowej Matched Length.

Długość sygnału (Signal Length), całkowita długość Pin/Package (Total Pin/Package Length) oraz opóźnienie (Delay) mogą być wyświetlane w różnych trybach panelu PCB, w tym w trybie Nets mode, Differential Pairs Editor mode oraz xSignals mode. Kliknij prawym przyciskiem myszy nagłówek kolumny w panelu PCB, aby włączyć/wyłączyć kolumny.

Jak długość jest uwzględniana w xSignals

Wartość Pin/Pkg Length jest automatycznie uwzględniana w całkowitej długości xSignal gdy:

- Ten sygnał jest częścią definicji xSignal

-

Ten pad nie jest połączony w schemacie prowadzenia typu fly-by (do tego pada jest podłączona tylko jedna ścieżka)

Pady połączone w schemacie prowadzenia typu fly-by (z punktem wejścia i wyjścia) są wykluczane z obliczeń długości.

Terminologia związana z sieciami

W edytorze PCB używana jest następująca terminologia:

- Net – zbiór wyprowadzeń komponentów (węzłów) połączonych ze sobą. Układ tego, jak węzły łączą się ze sobą, nazywa się topologią; domyślna topologia to „shortest”.

- From-To – koncepcyjnie From-To przebiega pomiędzy dwoma węzłami w sieci. From-To można tworzyć tak, aby podążały za topologią lub układem węzłów w tej sieci. Na przykład topologia sieci może przebiegać od R1-1 do U1-5 do U3-2 do R5-2. Taka sieć może mieć trzy From-To: R1-1 do U1-5; U1-5 do U3-2; oraz U3-2 do R5-2. Jeśli topologia zostanie zmieniona, zmienią się również możliwe From-To. From-To tworzy się w trybie From-To panelu PCB albo klikając przycisk Generate, aby utworzyć je na podstawie topologii, albo wybierając dwa pady w sieci i klikając przycisk Add From To.

- xSignal – zdefiniowany przez użytkownika zestaw węzłów, zwykle podzbiór sieci (od tego węzła do tamtego węzła) lub połączenie dwóch sieci obejmujące element szeregowy, taki jak rezystor terminujący.