Routing z kontrolowaną impedancją

Wraz ze wzrostem szybkości przełączania urządzeń, prowadzenie ścieżek o kontrolowanej impedancji stało się gorącym tematem dla projektantów układów cyfrowych. Ta strona przedstawia, jak można użyć silnika analizy integralności sygnału do dopasowania impedancji komponentów oraz możliwości prowadzenia ścieżek o kontrolowanej impedancji w edytorze PCB.

W środowisku inżynierskim funkcjonuje powiedzenie: istnieją tylko dwa rodzaje inżynierów elektroniki zajmujących się projektowaniem cyfrowym — ci, którzy mieli problemy z integralnością sygnału, i ci, którzy dopiero je będą mieli. Jeszcze nie tak wiele lat temu termin integralność sygnału był zarezerwowany dla specjalistów i trzeba było się nim zajmować tylko w projektach wysokiej prędkości. Jednak szybkości przełączania urządzeń w tych szybkich projektach nie są już niczym wyjątkowym; bardzo szybko stają się normą. Wraz z rozwojem technologii układów scalonych i zmniejszaniem rozmiaru tranzystorów rośnie szybkość, z jaką mogą się one przełączać. To właśnie ta szybkość przełączania wpływa na integralność sygnałów cyfrowych.

Na szczęście wielu potencjalnych problemów z integralnością sygnału można uniknąć, stosując dobre zasady projektowe i realizując projekt jako płytkę o kontrolowanej impedancji. Osiągnięcie tego wymaga określonych możliwości narzędzi projektowych — potrzebne są narzędzia analityczne wykrywające sieci z potencjalnymi problemami dzwonienia i odbić oraz narzędzia do projektowania płytek, które umożliwiają uzyskanie właściwych impedancji prowadzenia ścieżek. Edytor PCB w Altium Designer posiada te możliwości.

Ta strona pomoże Ci zrozumieć, co powoduje problemy z integralnością sygnału i czy Twoja płytka prawdopodobnie będzie na nie narażona. Omówione zostaną również dwa podejścia projektowe, które należy zastosować, aby zminimalizować potencjalne problemy SI — dopasowanie impedancji komponentów oraz prowadzenie ścieżek o kontrolowanej impedancji.

Kiedy prowadzenie ścieżek staje się częścią obwodu

Wraz ze wzrostem szybkości przełączania urządzeń rosną również wymagania stawiane projektantowi obwodów drukowanych i producentowi płytek. Gdy długość zbocza przełączającego sygnału staje się krótsza niż długość ścieżki PCB, która go przenosi, ścieżkę trzeba traktować jako część obwodu. Taka ścieżka ma impedancję, określaną jako characteristic impedance (Zo).

Najlepszym sposobem zarządzania wpływem tych dodatkowych elementów obwodu jest zaprojektowanie prowadzenia ścieżki tak, aby impedancja charakterystyczna była stała na całej jej długości — technika ta nazywa się controlled impedance routing.

Impedancja prowadzenia ścieżki jest definiowana przez:

- Cross-sectional area of the trace - określaną na podstawie szerokości, wysokości (grubości miedzi) oraz nachylenia krawędzi ścieżki powstałych podczas procesu trawienia.

- Distance from the trace to the reference plane(s) - ścieżka powrotna energii sygnału jest równie ważna jak ścieżka samego sygnału. Ta ścieżka powrotna podąża za ścieżką sygnału w sąsiedniej płaszczyźnie odniesienia lub płaszczyznach odniesienia.

- Properties of the surrounding materials - energia sygnału nie jest zawarta wyłącznie w miedzi ścieżki; z powodu efektu naskórkowego przemieszcza się ona również przez materiał dielektryczny otaczający ścieżkę. Przenikalność elektryczna materiału dielektrycznego określa, jak bardzo dielektryk wpływa na przepływ tej energii.

Kalkulator impedancji Simbeor oblicza szerokość (lub szerokości) wymaganą do uzyskania określonej impedancji.

Czy potrzebuję prowadzenia ścieżek o kontrolowanej impedancji?

Pytasz, czy naprawdę trzeba zawracać sobie głowę prowadzeniem ścieżek o kontrolowanej impedancji?

W idealnej sytuacji cała energia wychodząca z pinu wyjściowego komponentu zostałaby sprzężona z podłączoną ścieżką na PCB, przepłynęłaby przez prowadzenie na płytce do pinu wejściowego obciążenia na drugim końcu i zostałaby przez to obciążenie pochłonięta. Jeśli całkowita energia nie zostanie pochłonięta przez obciążenie, pozostała energia może zostać odbita z powrotem do prowadzenia na PCB i popłynąć do pinu wyjściowego źródła. Ta odbita energia może oddziaływać z oryginalnym sygnałem, dodając się do niego lub odejmując od niego (w zależności od polaryzacji energii), co prowadzi do dzwonienia. Jeśli dzwonienie jest wystarczająco duże, wpłynie na integralność sygnału, powodując nieprzewidywalne, błędne działanie obwodu.

Skąd więc wiadomo, czy może do tego dojść? Jeśli pin źródłowy jest w stanie zakończyć przejście zbocza, zanim sygnał dotrze do pinu obciążenia, istnieją warunki, w których na projekt może wpływać energia odbita. Powszechnie stosowaną praktyczną zasadą do określenia, czy problemy SI są prawdopodobne, jest reguła „1/3 czasu narastania”. Zgodnie z tą regułą, jeśli ścieżka jest dłuższa niż 1/3 długości czasu narastania, mogą wystąpić odbicia (dzwonienie). Jeśli pin źródłowy ma czas narastania 1 nSec, ścieżkę dłuższą niż 0,33 nSec (około 2 cale w FR4) należy traktować jako linię transmisyjną, a więc jako potencjalne źródło problemów z integralnością sygnału. Jeśli Twoje urządzenia mają taki czas narastania i wiesz, że będziesz mieć ścieżki o takiej długości, możesz napotkać problemy z integralnością sygnału na PCB.

Jak kontrolować impedancje?

Jak uniknąć sytuacji, w której energia odbija się tam i z powrotem między źródłem a obciążeniem? Można tego uniknąć przez dopasowanie impedancji. Dopasowanie impedancji zapewnia, że cała energia jest sprzęgana ze źródła do prowadzenia ścieżki, a następnie z prowadzenia ścieżki do obciążenia. Prowadzenie płytki z uwzględnieniem impedancji określa się jako prowadzenie ścieżek o kontrolowanej impedancji, albo inaczej — płytka, w której impedancje zostały odpowiednio zarządzane, nazywana jest PCB o kontrolowanej impedancji.

Istnieją dwa odrębne elementy osiągnięcia dopasowania impedancji: pierwszy to dopasowanie komponentów, drugi to poprowadzenie płytki tak, aby uzyskać wymaganą impedancję.

Dopasowanie impedancji komponentów

Nie da się uzyskać PCB o kontrolowanej impedancji wyłącznie przez samo prowadzenie ścieżek. Najpierw należy sprawdzić impedancje komponentów i w razie potrzeby je dopasować.

Najlepiej jest wykrywać sieci, które mogą mieć potencjalne problemy z integralnością sygnału, już na etapie tworzenia schematu, tak aby wszelkie dodatkowe komponenty terminujące mogły zostać uwzględnione przed rozpoczęciem projektowania płytki. Ponieważ piny wyjściowe mają niską impedancję, a piny wejściowe wysoką, prawdopodobnie konieczne będzie dodanie do projektu komponentów terminujących w celu uzyskania dopasowania impedancji.

Analizę integralności sygnału można przeprowadzić na projekcie już na etapie tworzenia schematu. Po uruchomieniu polecenia Tools » Signal Integrity często pojawi się okno dialogowe Errors or Warnings, wskazujące, że nie wszystkim komponentom przypisano modele integralności sygnału. Silnik analizy integralności sygnału automatycznie wybierze modele domyślne na podstawie oznaczeń komponentów; kliknij Continue, aby użyć wartości domyślnych, lub Model Assignments, aby przejrzeć i zmienić modele. Do okna dialogowego Signal Integrity Model Assignments można uzyskać dostęp w dowolnym momencie za pomocą przycisku Model Assignments w panelu Signal Integrity.

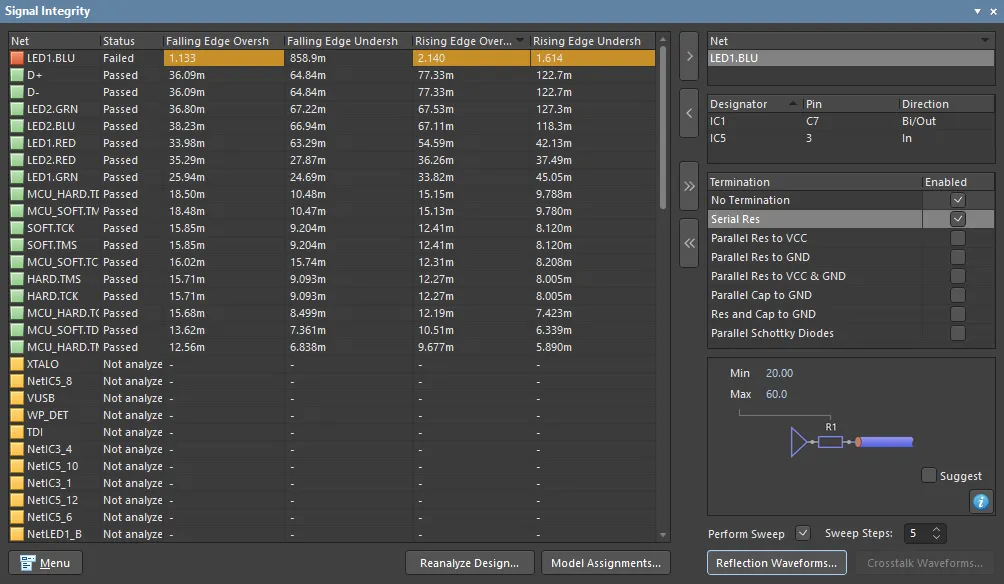

Analiza projektu

Po uruchomieniu polecenia Tools » Signal Integrity projekt jest analizowany, a wszelkie potencjalnie problematyczne sieci są identyfikowane w panelu Signal Integrity, jak pokazano poniżej.

Testowanie projektu pod kątem potencjalnych problemów z integralnością sygnału podczas tworzenia schematu.

Testowanie projektu pod kątem potencjalnych problemów z integralnością sygnału podczas tworzenia schematu.

Z poziomu panelu można przeprowadzić analizę odbić dla wybranej sieci (lub sieci). Po lewej stronie znajdują się wyniki analizy dla wszystkich sieci w projekcie. Wybierz sieć i kliknij przycisk ![]() (lub kliknij dwukrotnie nazwę sieci), aby przenieść tę sieć do pola Net po prawej stronie panelu, gdzie można przeprowadzić szczegółową analizę tej sieci, obejmującą:

(lub kliknij dwukrotnie nazwę sieci), aby przenieść tę sieć do pola Net po prawej stronie panelu, gdzie można przeprowadzić szczegółową analizę tej sieci, obejmującą:

- Sprawdzenie pinów w tej sieci, gdzie pojedyncze kliknięcie umożliwia przejście do tego pinu na schemacie, a podwójne kliknięcie pozwala sprawdzić i skonfigurować model przypisany do tego pinu.

- Włączenie jednej lub większej liczby teoretycznych opcji terminacji dla tej sieci.

- Przeprowadzenie analizy odbić dla sieci, co daje zestaw przebiegów pokazujących zachowanie na każdym pinie w tej sieci.

Panel umożliwia eksperymentowanie z możliwymi konfiguracjami i wartościami terminacji. Zwróć uwagę, że obszar Termination panelu Signal Integrity pokazany na powyższym obrazie ma włączoną opcję Serial Res. Sekcja panelu poniżej pokazuje szeregowy rezystor terminujący. To tutaj definiuje się minimalne i maksymalne teoretyczne wartości rezystancji szeregowej terminacji, które będą używane do analizy odbić (wyłącz pole wyboru Suggest, aby wprowadzić własne wartości).

Analiza wyników

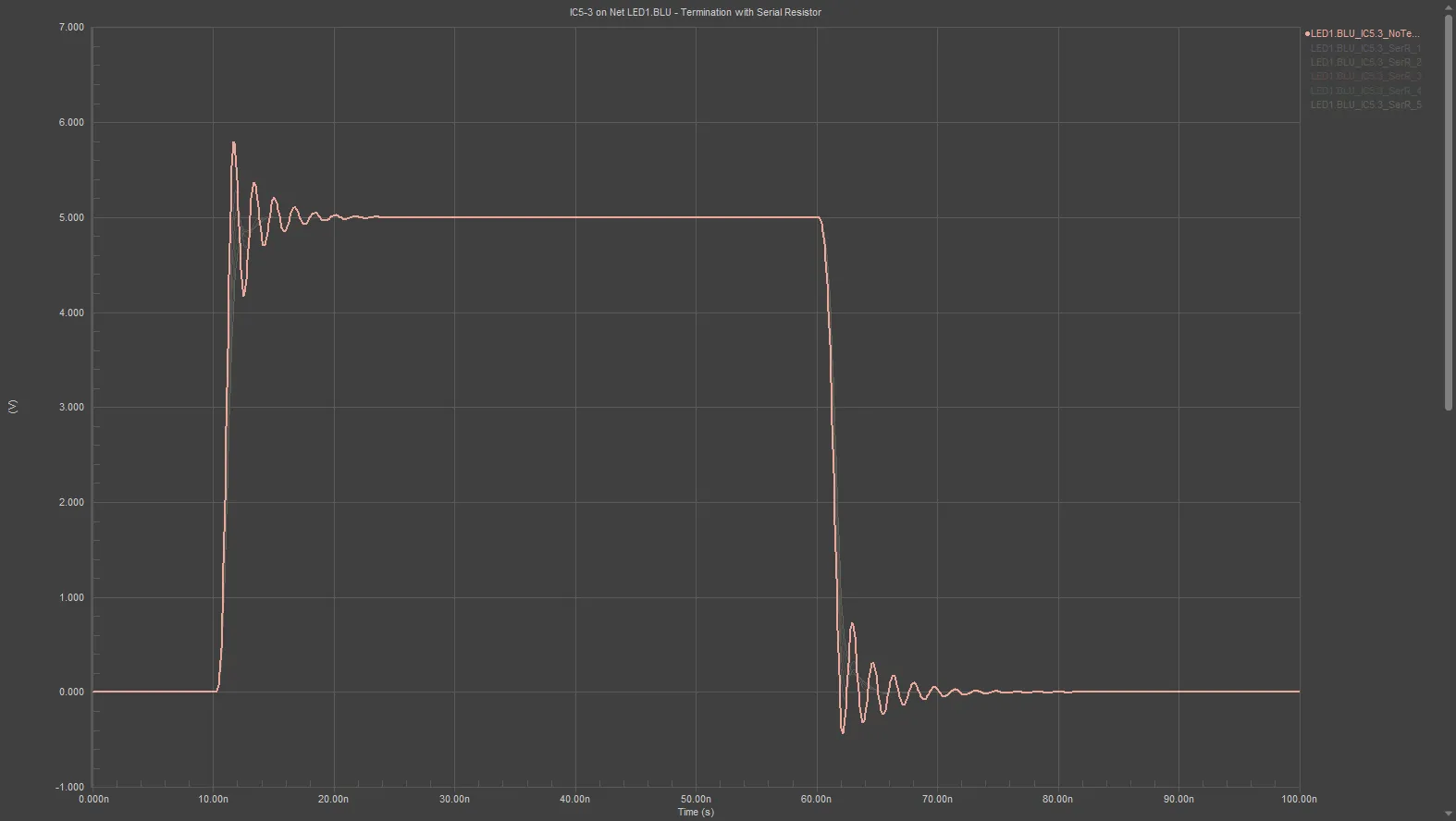

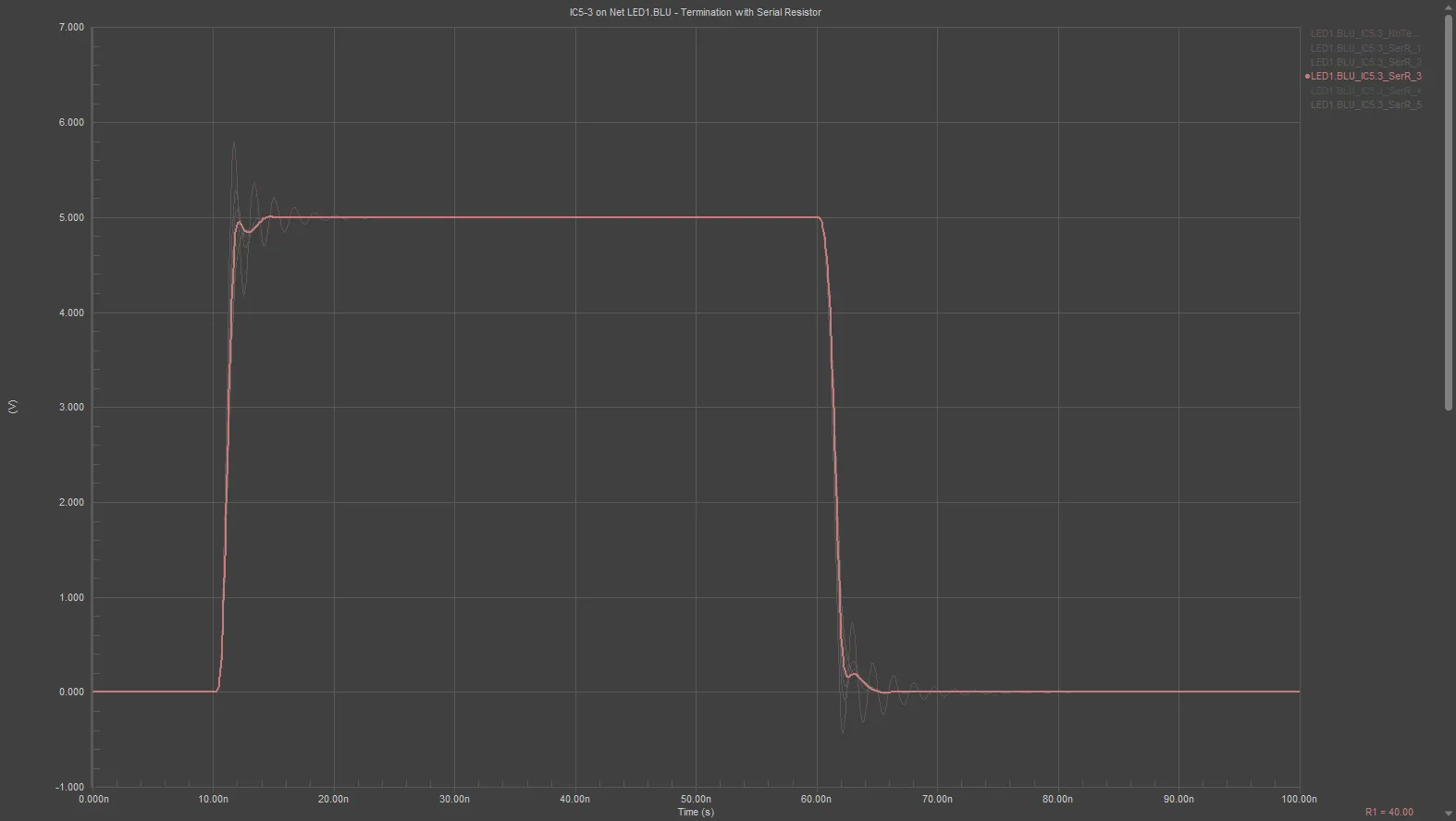

Po kliknięciu przycisku Reflection Waveforms wykonywana jest dokładna analiza odbić dla tej sieci, a wyniki są prezentowane w nowym oknie przebiegów (*.SDF).

Okno przebiegów będzie zawierać:

- Wykres dla każdej analizowanej sieci; klikaj karty u dołu okna, aby przełączać się między wykresami.

- Każdy wykres będzie zawierał przebieg dla każdego pinu w tej sieci, pokazujący zachowanie sygnału na danym pinie.

Poniższe obrazy przedstawiają dwa wykresy wyników dla pinu wejściowego sieci wybranej na obrazie z poprzedniego panelu. Pierwszy wykres pokazuje pin wejściowy w sieci bez terminacji; drugi wykres przedstawia sześć przebiegów: jeden dla oryginalnej sieci bez terminacji, a następnie pięć przebiegów z uwzględnieniem teoretycznej rezystancji terminacji szeregowej na pinie źródłowym.

Wykonano pięć przebiegów analizy odbić (Sweep Steps wartość opcji = 5), przy czym teoretyczny rezystor terminujący był zmieniany skokowo od Min = 20 omów do Max = 60 omów. Pięć przebiegów (pierwszy przy 20 omach, ostatni przy 60 omach) jest wymienionych po prawej stronie wykresu. Kliknięcie każdej etykiety podświetla dany wynik i wyświetla wartość teoretycznej rezystancji terminacji w prawym dolnym rogu. Dla tej sieci rezystancja terminacji szeregowej 40 omów dałaby wykres wybrany na obrazie po prawej stronie.

Wykres po lewej pokazuje analizę odbić dla sieci z potencjalnymi problemami integralności sygnału; wykres po prawej przedstawia tę samą sieć z dodanym teoretycznym rezystorem terminacji szeregowej o wartości około 40 omów.

Wykres po lewej pokazuje analizę odbić dla sieci z potencjalnymi problemami integralności sygnału; wykres po prawej przedstawia tę samą sieć z dodanym teoretycznym rezystorem terminacji szeregowej o wartości około 40 omów.

Co decyduje o impedancji ścieżki?

Drugą częścią uzyskania PCB o kontrolowanej impedancji jest poprowadzenie płytki w taki sposób, aby ścieżki miały zdefiniowaną impedancję. Na impedancję prowadzenia sygnałów wpływa wiele czynników, w tym wymiary ścieżek oraz właściwości materiałów użytych do wykonania PCB.

Edytor PCB zawiera elektromagnetyczny silnik Signal Integrity Simbeor® firmy Simberian. Dokładność modelu Simbeor została potwierdzona przy użyciu zaawansowanych algorytmów pełnofalowej analizy 3D, benchmarków i walidacji eksperymentalnej. Silnik Simbeor obsługuje wszystkie nowoczesne struktury i materiały płytek.

Wersja Simbeor

Simbeor SFS

Impedancje są obliczane przez Simbeor SFS, quasi-statyczny solver pola. Simbeor SFS to zaawansowany quasi-statyczny dwuwymiarowy solver pola oparty na metodzie momentów, którego poprawność potwierdzono przez analizę zbieżności, porównania i pomiary. Solver tworzy siatkę granic dielektryków i przewodników oraz rozwiązuje odpowiednie równania, aby zbudować zależne od częstotliwości macierze RLGC dla równań telegrafistów.

Simbeor SFS nie jest solverem pełnofalowym, ponieważ nie jest to potrzebne do oceny impedancji, opóźnienia ani tłumienia w połączeniach PCB ze względu na quasi-TEM charakter propagujących się tam fal. Takie fale można dokładnie symulować za pomocą parametrów RLGC wyodrębnionych przez quasi-statyczny dwuwymiarowy solver pola.

Unikalną właściwością solvera Simbeor SFS jest obsługa modeli chropowatości przewodnika. Należy pamiętać, że nie obsługuje on modelu przewodnika wielowarstwowego (platerowania), a chropowatość jest wspólna dla wszystkich przewodników. Solver jest quasi-statyczny, ponieważ rozwiązanie nie uwzględnia dyspersji wysokoczęstotliwościowej występującej w liniach mikropaskowych (większa koncentracja pól w dielektryku o wyższej stałej dielektrycznej przy wysokich częstotliwościach).

► Dowiedz się więcej o technologii elektromagnetycznej integralności sygnału Simberian

Obsługiwane struktury PCB

Impedancje można obliczać dla następujących struktur PCB:

- Mikropasek

- Symetryczny stripline

- Asymetryczny stripline

- Jednostronne i różnicowe struktury koplanarne

- Wiele sąsiadujących warstw dielektrycznych o różnych właściwościach dielektrycznych.

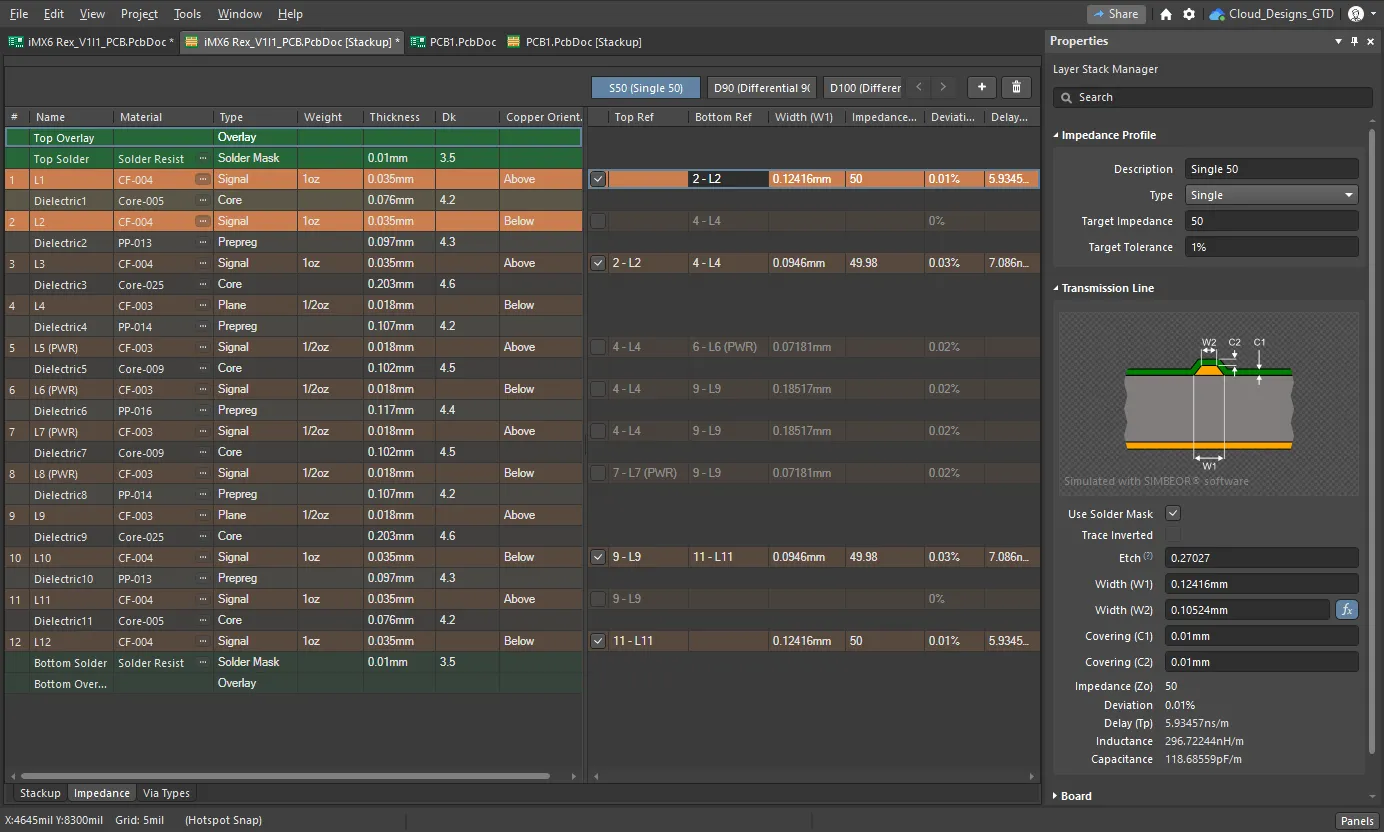

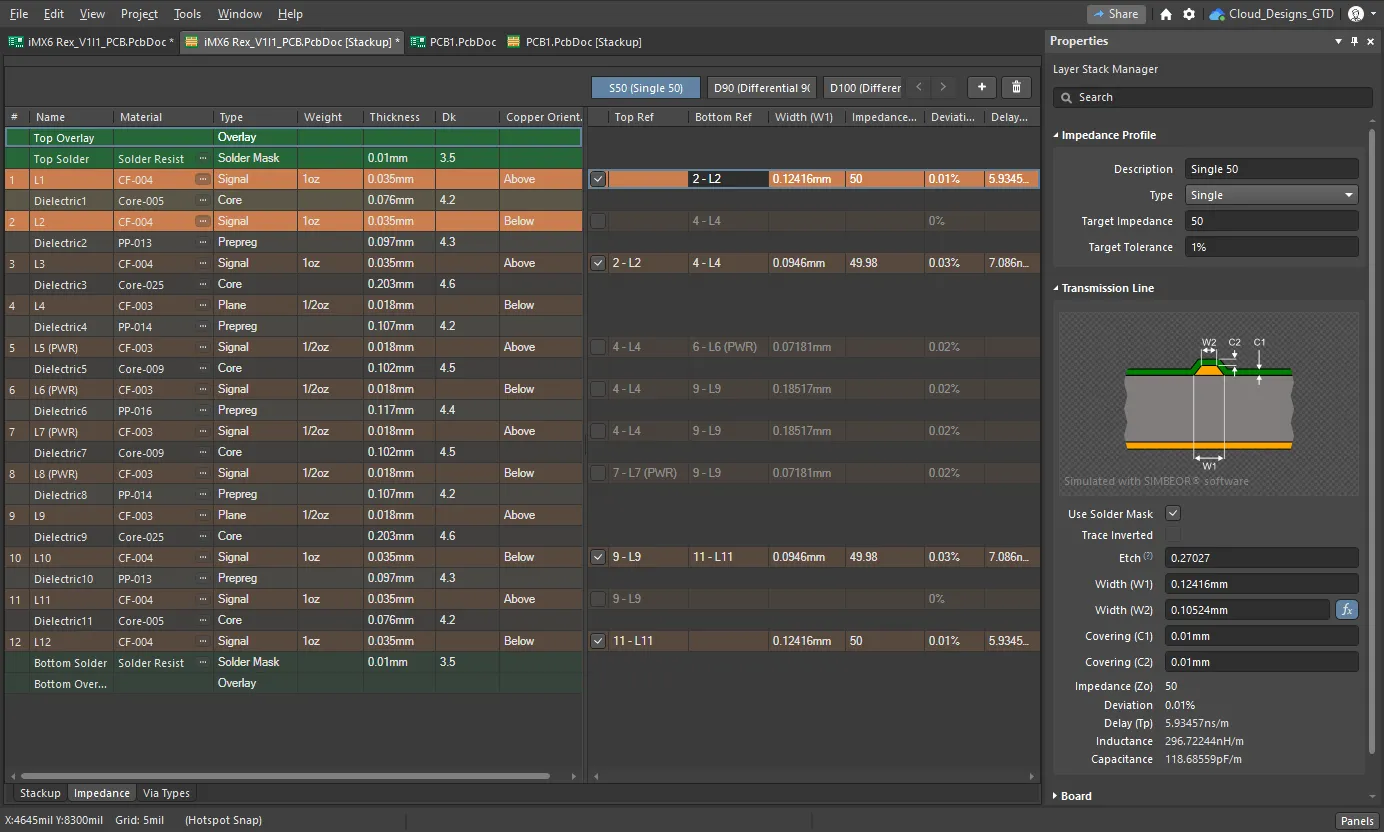

Konfigurowanie PCB do prowadzenia ścieżek o kontrolowanej impedancji

Prowadzenie ścieżek o kontrolowanej impedancji polega na skonfigurowaniu wymiarów ścieżek i właściwości materiałów płytki tak, aby uzyskać określoną impedancję. Odbywa się to w Layer Stack Manager edytora PCB. Aby otworzyć Layer Stack Manager,, wybierz Design » Layer Stack Manager z menu głównego. Layer Stack Manager otwiera się w edytorze dokumentów w taki sam sposób jak arkusz schematu, PCB i inne typy dokumentów.

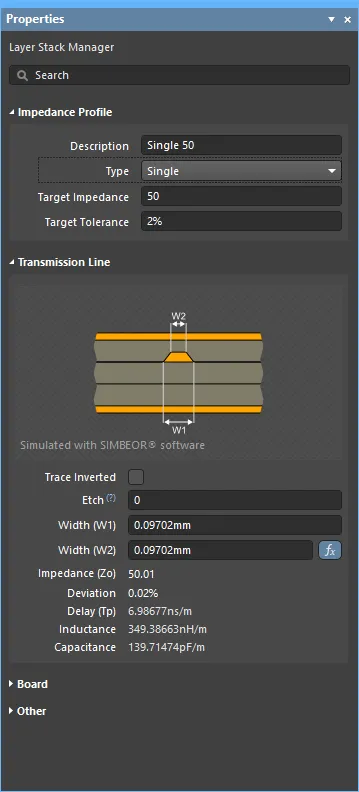

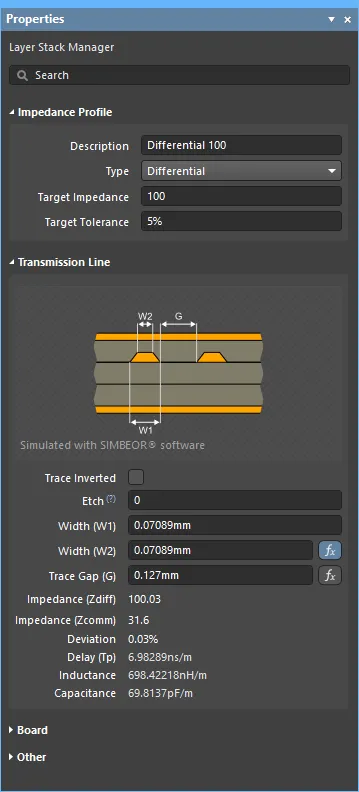

Szerokość ścieżki wymagana do uzyskania określonej impedancji jest obliczana jako część profilu impedancji, konfigurowanego na karcie Impedance w Layer Stack Manager.

Na podstawie:

- wartości Target Impedance, Target Tolerance i Roughness, które konfigurujesz na karcie Impedance, oraz

-

ustawień materiałowych zdefiniowanych na karcie Stackup, w tym:

- grubości warstwy sygnałowej,

- grubości otaczających warstw dielektrycznych (odległości od płaszczyzny/płaszczyzn odniesienia), oraz

- właściwości materiału dielektrycznego (przenikalność Dk i współczynnik strat Df).

Gdy są one poprawnie skonfigurowane, kalkulator impedancji ma wystarczające informacje, aby obliczyć:

- Szerokość ścieżki

- Obliczoną impedancję (Z)

- Impedancję trybu wspólnego (Zcomm)

- Odchylenie impedancji (Z Deviation)

- Opóźnienie propagacji (Tp)

- Indukcyjność na jednostkę długości (p.u.l.)

- Pojemność na jednostkę długości (p.u.l.)

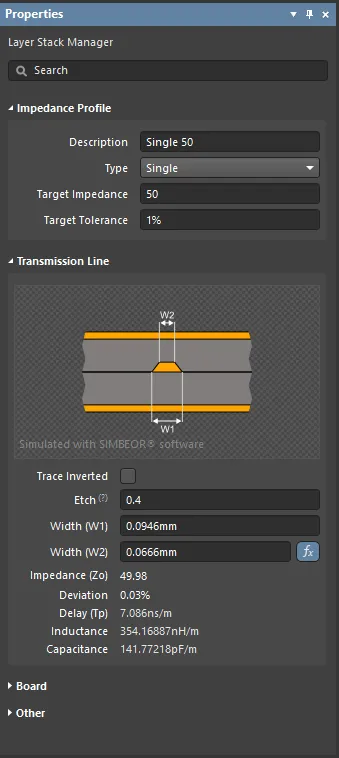

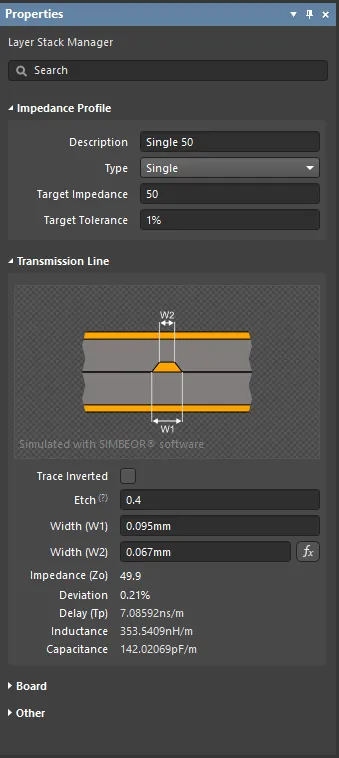

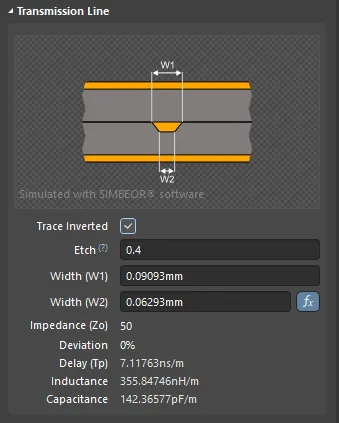

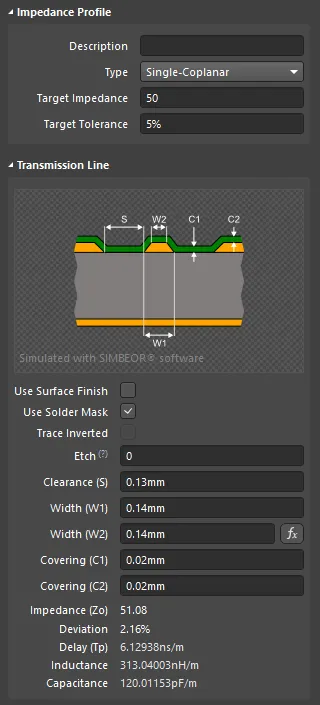

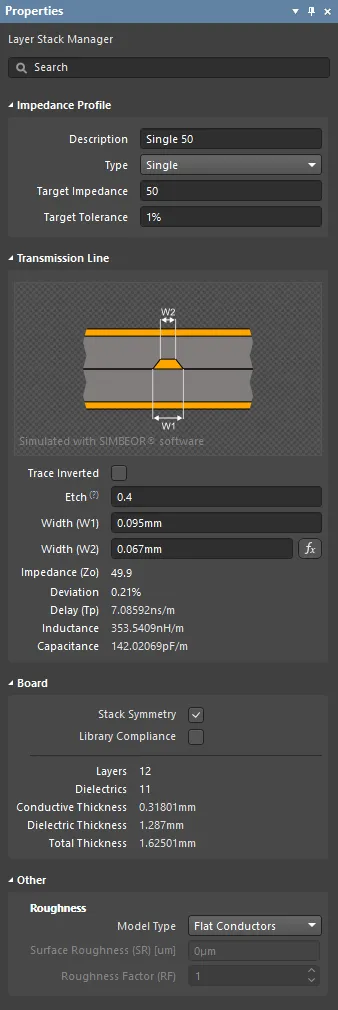

Obliczone wartości są wyświetlane w sekcji Transmission Line panelu Properties gdy na Layer Stack Manager wybrana jest karta Impedance, jak pokazano poniżej.

Profil impedancji 50Ω zdefiniowany dla pojedynczych sieci prowadzonych na warstwie górnej. Najedź kursorem na obraz, aby wyświetlić ustawienia tego samego profilu dla warstwy L3 (grafika dzięki uprzejmości FEDEVEL Open Source, www.fedevel.com).

Profil impedancji 50Ω zdefiniowany dla pojedynczych sieci prowadzonych na warstwie górnej. Najedź kursorem na obraz, aby wyświetlić ustawienia tego samego profilu dla warstwy L3 (grafika dzięki uprzejmości FEDEVEL Open Source, www.fedevel.com).

Konfigurowanie stosu warstw

Main page: Definiowanie stosu warstw

Warstwy miedzi i dielektryczne warstwy produkcyjne są konfigurowane na karcie Stackup w Layer Stack Manager.

- Warstwy są dodawane, usuwane i konfigurowane na tej karcie. W projekcie rigid-flex warstwy są również włączane i wyłączane na tej karcie.

-

Właściwości aktualnie wybranej warstwy można edytować bezpośrednio w siatce lub w panelu Properties. Kliknij przycisk

u dołu obszaru projektowego, aby włączyć panel.

u dołu obszaru projektowego, aby włączyć panel.

-

Kliknij prawym przyciskiem myszy w siatce warstw lub użyj poleceń Edit » Add Layer, aby dodać warstwę. Dodanie warstwy miedzi spowoduje również dodanie warstwy dielektrycznej, jeśli sąsiednia istniejąca warstwa także jest warstwą miedzi.

Jeśli opcja Stack Symmetry jest włączona w sekcji Board panelu Properties, warstwy są dodawane parami dopasowanymi, wyśrodkowanymi względem środkowej warstwy dielektrycznej. - Materiał warstwy można wpisać bezpośrednio do wybranej komórki Material albo wybrać w oknie dialogowym Select Material; kliknij przycisk wielokropka , aby je otworzyć.

- Do warstwy miedzi można dodać wykończenie powierzchni. Użyj podmenu Add Layer, aby dodać warstwę Surface Finish do aktualnie wybranej warstwy miedzi, a następnie kliknij przycisk wielokropka dla nowej warstwy wykończenia powierzchni, aby wybrać typ wykończenia.

- Wybraną warstwę można przesuwać w górę lub w dół w obrębie warstw tego samego typu za pomocą menu kontekstowego lub menu Edit.

- Obszar Board panelu Properties zawiera opcje wymuszania Stack Symmetry i Library Compliance. Więcej na ten temat poniżej.

- Obszar Board panelu Properties wyświetla podsumowanie aktualnie wybranego stosu warstw (lub podstosu w projekcie rigid/flex z wieloma stosami).

Uwagi dotyczące stosu warstw

Podstawowym wymaganiem kontroli impedancji jest zapewnienie ścieżki powrotu sygnału pod każdą ścieżką sygnałową. Silnik SI Simbeor obsługuje zarówno warstwy płaszczyzn, jak i warstwy sygnałowe pokryte poligonem. Te warstwy ścieżki powrotu powinny być rozmieszczone w całym stosie warstw płytki. Idealnie powinny być ułożone tak, aby co najmniej jedna warstwa ścieżki powrotu przylegała do każdej warstwy sygnałowej prowadzącej ścieżki o kontrolowanej impedancji. Sąsiednia warstwa ścieżki powrotu zapewnia drogę powrotu sygnału i, z powodów których nie będziemy tu omawiać, robi to niezależnie od napięcia DC rozprowadzanego przez tę płaszczyznę.

Prąd ścieżki powrotu płynący przez płaszczyznę będzie próbował podążać tą samą fizyczną drogą co ścieżka na warstwie sygnałowej, dlatego ważne jest, aby unikać wprowadzania nieciągłości, takich jak podział lub wycięcie w warstwie ścieżki powrotu pod dowolnym krytycznym prowadzeniem sygnału.

Oprócz wyboru odpowiedniej kolejności warstw sygnałowych i płaszczyzn należy również zdefiniować właściwości materiałowe każdej warstwy, w tym:

- Grubość miedzi

- Grubość dielektryka

- Stałą dielektryczną

Wartości te oraz szerokość ścieżki składają się na końcową impedancję. Uzyskanie wymaganej impedancji staje się więc procesem dostrajania wszystkich tych wartości. Pamiętaj, że możliwe wartości grubości miedzi i dielektryka mogą być również ograniczone przez materiały dostępne u producenta PCB.

► Dowiedz się więcej o możliwych stosach warstw

Definiowanie profili impedancji

Silnik Simbeor jest wbudowany w Layer Stack Manager edytora PCB (Design » Layer Stack Manager). Aby skonfigurować stos warstw do trasowania z kontrolowaną impedancją, przejdź do karty Layer Stack Manager's Impedance, gdzie możesz dodać i skonfigurować profil impedancji.

Profil impedancji 50Ω zdefiniowany dla pojedynczych sieci trasowanych na warstwie górnej. Najedź kursorem na obraz, aby wyświetlić ustawienia tego samego profilu dla warstwy L3.

Profil impedancji 50Ω zdefiniowany dla pojedynczych sieci trasowanych na warstwie górnej. Najedź kursorem na obraz, aby wyświetlić ustawienia tego samego profilu dla warstwy L3.

Uwagi dotyczące tworzenia i konfigurowania profilu impedancji:

- W Layer Stack Manager przełącz się na kartę Impedance, jak pokazano powyżej.

-

Kliknij przycisk

(lub przycisk

(lub przycisk  , jeśli profil jest już zdefiniowany), aby dodać nowy profil.

, jeśli profil jest już zdefiniowany), aby dodać nowy profil.

- Zdefiniuj wymagane Type, Target Impedance i Target Tolerance impedancji w panelu Properties. Description jest opcjonalny; będzie wyświetlany wszędzie tam, gdzie wyświetlana jest nazwa Profilu impedancji.

-

Siatka warstw jest podzielona na 2 obszary; warstwy w stackupie są wyświetlane po lewej stronie, a następnie dla każdej warstwy sygnałowej w stackupie po prawej stronie, w obszarze Profilu impedancji, wyświetlana jest odpowiednia warstwa. Użyj pola wyboru warstwy w obszarze Profilu, aby włączyć obliczanie impedancji dla tej warstwy. Korzystając z powyższego obrazu jako przykładu i odnosząc się do numeru warstwy pokazanego w skrajnej lewej kolumnie, warstwy

L1,L3,L10iL12mają zaznaczone pole wyboru warstwy, co włącza je do obliczeń impedancji. -

Gdy klikniesz włączoną warstwę w obszarze Profilu, wszystkie warstwy w stosie warstw zostaną wygaszone z wyjątkiem tych używanych do obliczania impedancji dla wybranej warstwy sygnałowej (jak pokazano na powyższym obrazie). Edytuj warstwę(-y) odniesienia tej warstwy w kolumnach Top Ref i Bottom Ref obszaru Impedance Profile . Zwróć uwagę, że warstwy odniesienia mogą mieć Type warstwy równe

Planelub Signal. Na przykład na powyższym obrazie warstwaL10w stackupie jest włączona do obliczeń impedancji, z ustawieniem Top Ref na9-L9, która jest warstwąPlane, oraz Bottom Ref ustawionym na11-L11, która jest warstwą Signal . Oprogramowanie zakłada, że jeśli warstwa sygnałowa jest używana jako płaszczyzna odniesienia, zawiera ciągłą płaszczyznę miedzi połączoną z siecią zasilania lub masy. - Włącz pole wyboru Impedance Profile dla każdej innej warstwy, która będzie prowadzić trasowanie z tą impedancją, i skonfiguruj płaszczyznę(-y) odniesienia. Najedź kursorem na powyższy obraz, aby wyświetlić Profil impedancji S50 dla warstwy L3.

- Jeśli obliczona szerokość ścieżki trasowania ma wartość, której nie można zamówić, możesz dostroić ustawienia szerokości i odstępu.

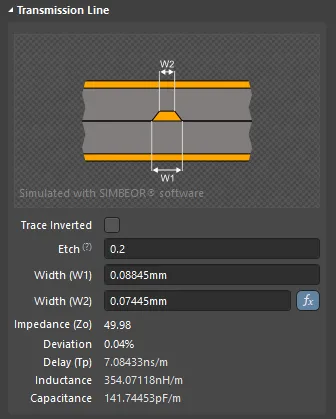

Dostrajanie ustawień szerokości i odstępu

Oprogramowanie oblicza szerokość ścieżki na podstawie docelowej impedancji i tolerancji. Nierzadko zdarza się, że obliczona szerokość ścieżki ma wartość, której nie można zamówić, na przykład 0,0683 mm. Producent PCB poinformuje, jakie grubości materiałów są dostępne i jaką precyzję może osiągnąć dla szerokości ścieżek. Następnie proces polega na rozpoczęciu od pożądanych wartości i testowaniu wpływu na obliczone wartości impedancji, gdy wymiary zostaną dostosowane do dostępnych.

Aby wesprzeć ten proces testowania i dostrajania ustawień, kalkulatory impedancji obsługują obliczenia impedancji w przód i wstecz. Domyślnym trybem jest obliczanie w przód (wprowadzasz impedancję, oprogramowanie oblicza szerokość). Ikona ![]() wskazuje obliczaną zmienną.

wskazuje obliczaną zmienną.

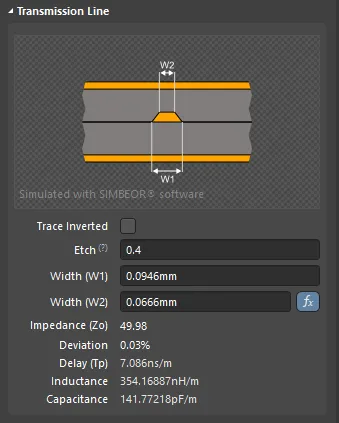

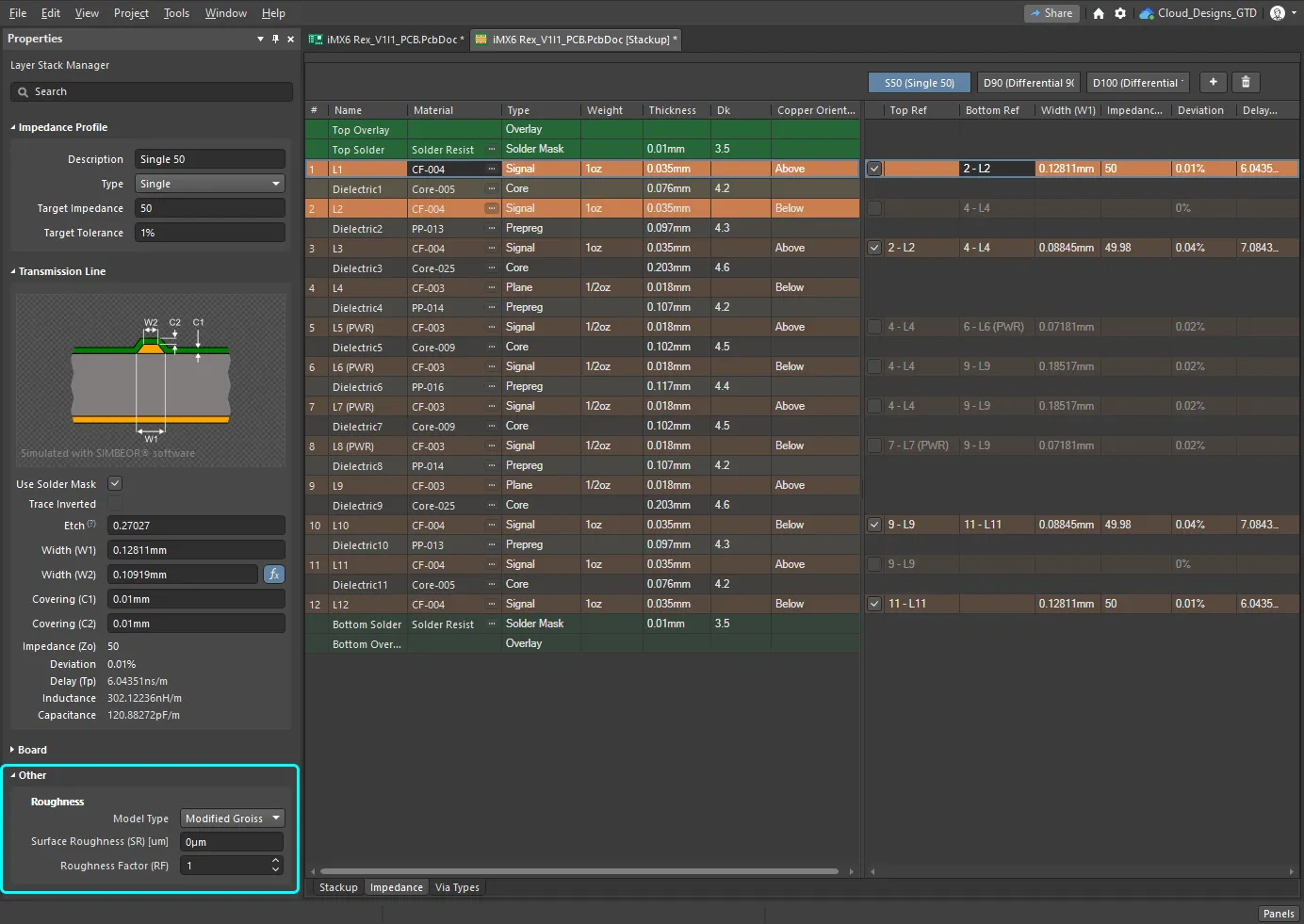

Docelowa impedancja 50Ω daje szerokość obliczoną w przód (W1) równą 94,6 µm. Obraz po prawej pokazuje obliczenie wsteczne, gdy szerokość (W1) jest ustawiona na 95 µm.

Docelowa impedancja 50Ω daje szerokość obliczoną w przód (W1) równą 94,6 µm. Obraz po prawej pokazuje obliczenie wsteczne, gdy szerokość (W1) jest ustawiona na 95 µm.

Aby odwrócić obliczenie i sprawdzić różne szerokości ścieżki dla wybranej warstwy, wpisz nową wartość Width (W1) i naciśnij klawisz Enter na klawiaturze. Obliczone wartości zostaną zaktualizowane, aby odzwierciedlić wpływ zmiany na tę szerokość. Kliknij przycisk ![]() , aby przywrócić kalkulator do trybu obliczania w przód. Wprowadzenie nowej wartości do Width (W2) zmieni wartość Etch.

, aby przywrócić kalkulator do trybu obliczania w przód. Wprowadzenie nowej wartości do Width (W2) zmieni wartość Etch.

Aby przeanalizować wyniki dla linii transmisyjnej pary różnicowej, wskaż obliczaną zmienną — Trace Width lub Trace Gap — klikając odpowiedni przycisk ![]() . Edytuj drugą zmienną, aby zmienić Target Impedance, albo alternatywnie zmień Target Impedance, aby sprawdzić wpływ na drugą zmienną.

. Edytuj drugą zmienną, aby zmienić Target Impedance, albo alternatywnie zmień Target Impedance, aby sprawdzić wpływ na drugą zmienną.

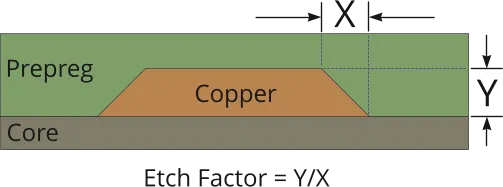

Współczynnik trawienia

Ścieżki sygnałowe na PCB są wytwarzane przez wytrawianie niepożądanej miedzi. Ponieważ środek trawiący zaczyna usuwać miedź od powierzchni, ta miedź pozostaje dłużej w kontakcie z wytrawiaczem. W rezultacie gotowe krawędzie ścieżki będą miały nachylenie, zmniejszając pole przekroju poprzecznego gotowej ścieżki, jak pokazano na poniższym obrazie.

Pole miedzi utraconej na krawędziach ścieżki (po obu stronach) podczas trawienia = X * Y

Wielkość tego nachylenia jest określana jako współczynnik trawienia, gdzie:

Etch Factor = Y/X

Jeśli Y = X, to Etch Factor = 1

Odnosząc się do obrazu pokazanego w panelu Properties:

Najedź kursorem na ?, aby wyświetlić wzór.

Najedź kursorem na ?, aby wyświetlić wzór.

Standardowa definicja współczynnika trawienia określa go jako stosunek trace thickness / amount of over-etching. Daje to następujący wzór:

Etch Factor = T/[0.5(W1-W2)]

Wadą tego podejścia jest to, że aby określić brak nadtrawienia (co oznacza, że krawędzie ścieżki są pionowe), trzeba by wprowadzić wartość inf (nieskończoność) dla współczynnika trawienia. Aby uprościć określanie wielkości trawienia, wzór został odwrócony, tak aby można było wprowadzić wartość 0 (zero), wskazującą brak nadtrawienia.

Etch = [0.5(W1-W2)]/T

Orientacja miedzi

Innym szczegółem produkcyjnym, który wpływa na współczynnik trawienia, jest orientacja miedzi. Ścieżki PCB powstają przez wytrawianie niepożądanej miedzi z ciągłej folii miedzianej laminowanej na podłożu dielektrycznym. Orientacja miedzi określa kierunek, w którym miedź wystaje od tego podłoża. Można też myśleć o tym jako o kierunku, z którego miedź jest trawiona — od góry lub od dołu.

Kliknij pole wyboru Trace Inverted, aby przełączyć orientację miedzi z Above na Below.

Kliknij pole wyboru Trace Inverted, aby przełączyć orientację miedzi z Above na Below.

Chropowatość powierzchni przewodnika

Powierzchnia każdej warstwy miedzi w płytce drukowanej ma pewien stopień chropowatości. Podczas produkcji PCB powierzchnia warstw miedzi jest poddawana obróbce w celu zwiększenia chropowatości, aby poprawić przyczepność między warstwami miedzi i dielektryka. Ta chropowatość powierzchni staje się istotnym czynnikiem wpływającym na impedancję przewodnika przy szybkościach przełączania powyżej 10 GB/s. Na podstawie szeroko zakrojonych badań i analiz eksperci branżowi doszli do wniosku, że chropowatość powierzchni można modelować za pomocą współczynnika korekcji chropowatości wyprowadzonego z wartości Surface Roughness i Roughness Factor.

RoughnessUstawienia są dostępne w trybie Layer Stack Manager panelu Properties . Te parametry są używane tylko dla warstw przewodzących.

Chropowatość powierzchni jest uwzględniana w obliczaniu impedancji charakterystycznej.

Chropowatość powierzchni jest uwzględniana w obliczaniu impedancji charakterystycznej.

Chropowatość:

-

Model Type - preferowany model do obliczania wpływu chropowatości powierzchni (więcej informacji o różnych modelach można znaleźć w artykułach poniżej). Dotyczy wszystkich warstw miedzi w podstosie.

-

Surface Roughness - wartość chropowatości powierzchni (dostępna u producenta). Wprowadź wartość od 0 do 10 µm, domyślnie 0,1 µm

-

Roughness Factor - charakteryzuje oczekiwany maksymalny wzrost strat przewodnika spowodowany efektem chropowatości. Wprowadź wartość od 1 do 100; wartość domyślna to 2.

Dalsza lektura

- Practical methodology for analyzing the effect of conductor roughness on signal losses and dispersion in interconnects: Y. Shlepnev, C. Nwachukwu, DesignCon2012.

- Unified approach to interconnect conductor surface roughness modeling: Y. Shlepnev, 2017 IEEE 26th Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS2017)

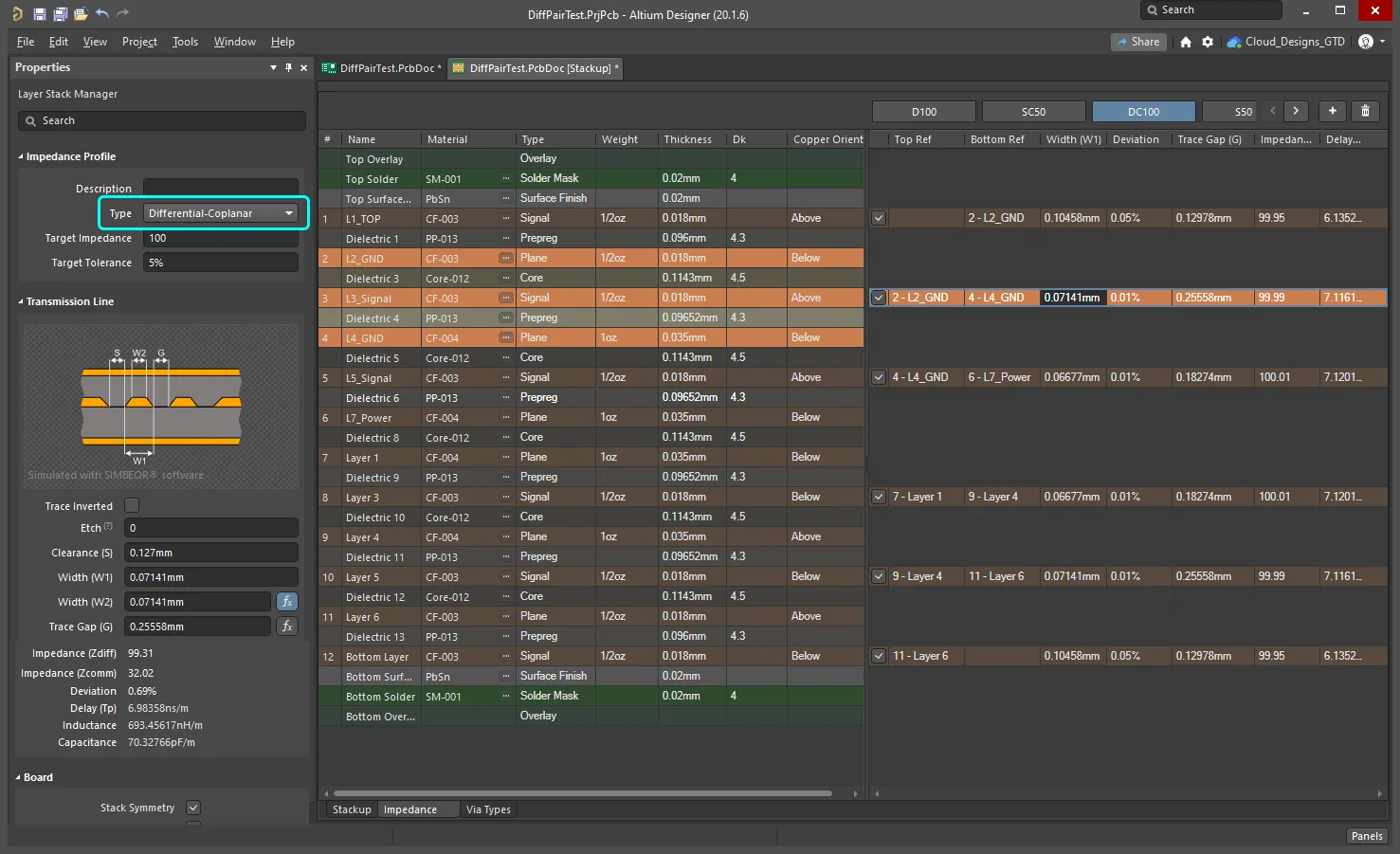

Obsługa struktur linii transmisyjnych koplanarnych

Kalkulator impedancji w Layer Stack Manager obsługuje pojedyncze i różnicowe struktury koplanarne. Utwórz nowy profil impedancji, a następnie wybierz Single-Coplanar lub Differential-Coplanar z listy rozwijanej Type Profilu impedancji.

Praca ze strukturami koplanarnymi:

- Tak jak w przypadku standardowych impedancji pojedynczych i różnicowych, wartości każdej zmiennej są automatycznie obliczane na podstawie zdefiniowanych przez użytkownika Target Impedance i Target Tolerance oraz właściwości fizycznych warstw płytki. Te automatycznie obliczone wartości można dostosować, wprowadzając nowe wartości do pól edycyjnych trybu Layer Stack Manager panelu Properties.

- Aby wskazać sieci sygnałowe, które mają być prowadzone w strukturze koplanarnej, skonfiguruj regułę projektową Szerokość prowadzenia (lub Prowadzenie par różnicowych) z włączoną opcją Use Impedance Profile i wybranym wymaganym profilem impedancji koplanarnej.

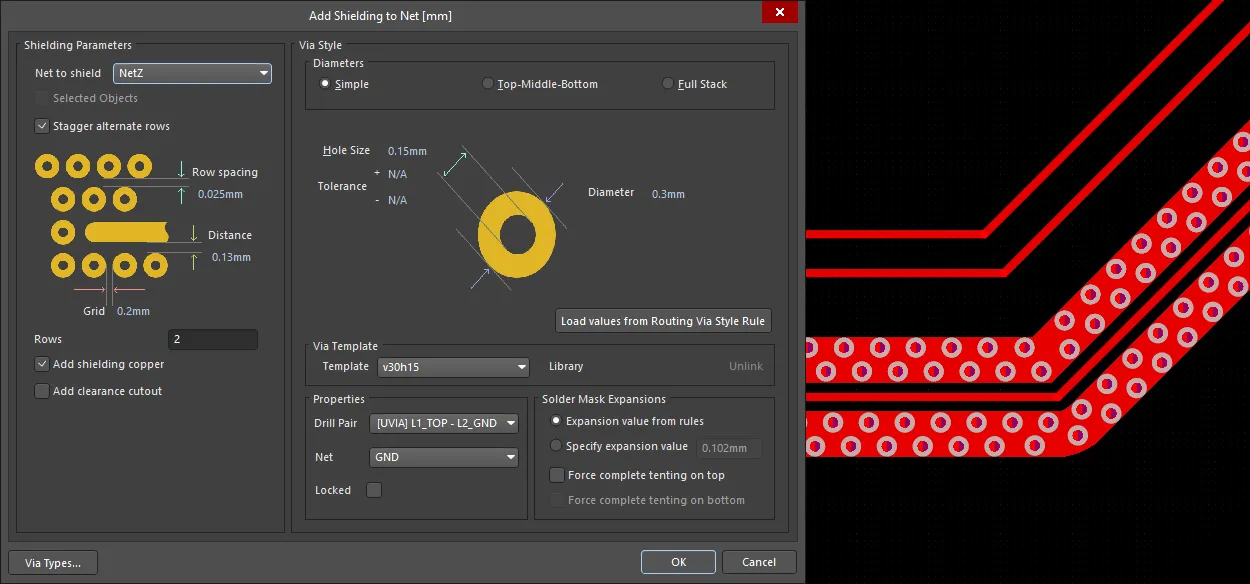

- Struktury koplanarne wymagają płaszczyzny odniesienia po obu stronach ścieżki sygnałowej; można ją utworzyć za pomocą umieszczonego poligonu lub, jeśli dodawane są przelotki stitching, poleceniem Add Shielding to Net (więcej informacji poniżej). Jeśli umieszczasz poligon, odstęp między tym poligonem a ścieżką sygnałową jest definiowany przez wartość Clearance (S) określoną przez kalkulator impedancji Simbeor (wyświetlaną w panelu Properties, pokazanym na ilustracjach powyżej i poniżej). Skonfiguruj regułę projektową Clearance design rule, aby kontrolować odstęp między poligonem odniesienia a ścieżką sygnałową (pokaż obraz).

-

Powszechną praktyką jest dodanie ogrodzenia z przelotek wzdłuż każdej strony ścieżki sygnałowej, gdy struktura koplanarna jest uziemiona. Użyj polecenia Tools » Via Stitching/Shielding » Add Shielding to Net w edytorze PCB, aby to zrobić. Oprócz umieszczania przelotek, po włączeniu opcji Add shielding copper to polecenie może również umieścić poligon wokół prowadzenia sygnału, aby objąć ogrodzenie z przelotek, jak pokazano na ilustracji po prawej poniżej.

► Dowiedz się więcej o Via Shielding

Kalkulator impedancji określa właściwości sygnału i odstępy (pierwsza ilustracja); użyj tego odstępu w ustawieniu Distance funkcji via shielding.

Kalkulator impedancji określa właściwości sygnału i odstępy (pierwsza ilustracja); użyj tego odstępu w ustawieniu Distance funkcji via shielding.

Wybór materiału warstwy

W projekcie z kontrolowaną impedancją wybór materiałów użytych w stosie warstw jest bardzo ważny.

Na przykład najczęściej stosowanym materiałem do produkcji PCB jest żywica epoksydowa wzmacniana włóknem szklanym (fiberglass), z folią miedzianą połączoną z każdą stroną. Gęstość splotu tkaniny z włókna szklanego wpływa na wartość i stabilność stałej dielektrycznej Dk (przenikalności) oraz tangensa strat Df. Tkanina z włókna szklanego jest otoczona żywicą — procentowa zawartość żywicy również ma znaczenie dla właściwości materiału.

Dostępny jest szeroki zakres splotów włókna szklanego. Aby pomóc zapewnić przewidywalność i parametry materiałów na bazie włókna szklanego używanych w produkcji PCB, IPC opracowało standard dotyczący splotów:

IPC standard IPC-4412B: Specification for Finished Fabric Woven from "E" Glass for Printed Boards

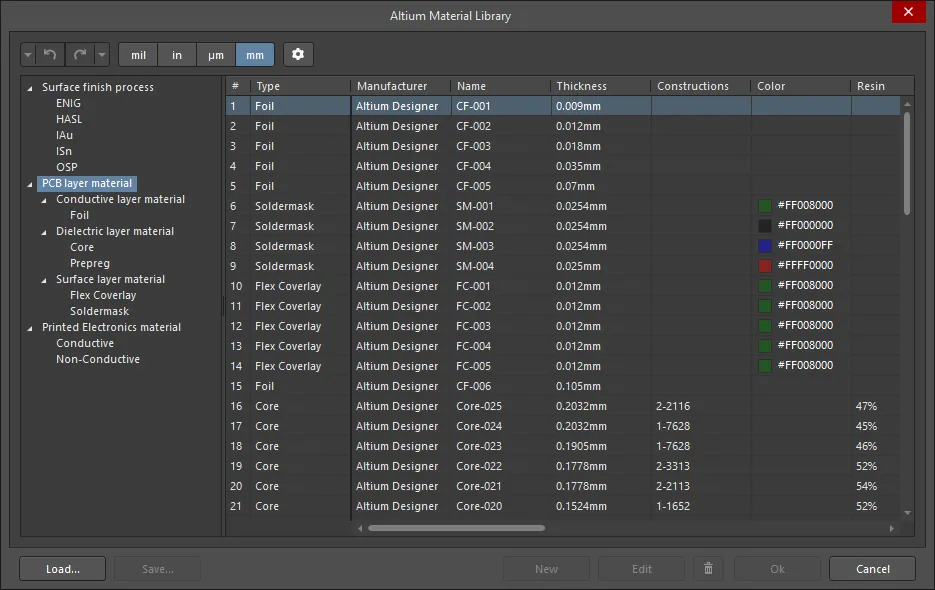

Biblioteka materiałów

Jako projektant możesz albo edytować właściwości materiału bezpośrednio w Layer Stack Manager , albo wybierać materiały z Altium Material Library.

Całą bibliotekę można przeglądać (i rozszerzać) w oknie dialogowym Altium Material Library dialog (Tools » Material Library).

Materiały są zorganizowane w kategorie zastosowań, dostępne przez strukturę drzewa po lewej stronie okna dialogowego. Poniżej tego poziomu każda kategoria zastosowań jest podzielona na kategorie funkcjonalne, takie jak Conductive layer material, Dielectric layer material, i Surface Layer Material iw kategorii PCB layer material.

Dodawanie, zapisywanie i wczytywanie materiału

Nowy materiał można dodać do biblioteki, gdy w drzewie wybrana jest konkretna kategoria materiału. Materiały zdefiniowane w zewnętrznej bibliotece materiałów można wczytać (przycisk Load), a materiał zdefiniowany przez użytkownika, dodany w oknie dialogowym Altium Material Library, można również zapisać do biblioteki użytkownika (przycisk Save). Zapisywany jest tylko materiał zdefiniowany przez użytkownika.

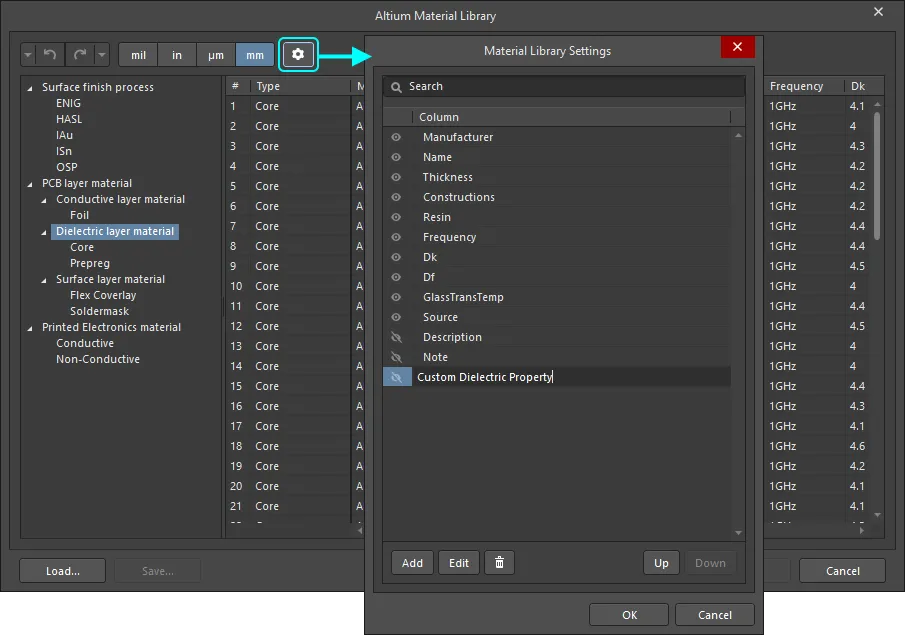

Dodawanie niestandardowych właściwości do materiału

Do materiałów opisanych w bibliotece (domyślnych i zdefiniowanych przez użytkownika) można dodawać niestandardowe właściwości. Aby dodać niestandardową właściwość, najpierw wybierz odpowiedni węzeł w drzewie po lewej stronie, aby określić materiał(y), do których ma zostać dodana, a następnie kliknij przycisk ![]() , aby otworzyć okno dialogowe Material Library Settings.

, aby otworzyć okno dialogowe Material Library Settings.

Wymaganą wartość można następnie dodać do wybranego materiału w oknie dialogowym Altium Material Library; wybierz wiersz i kliknij przycisk Edit.

Panel Properties

Gdy aktywna jest karta Impedance dokumentu Layer Stack, panel Properties umożliwia skonfigurowanie wymagań profilu impedancji. Wymagany profil impedancji można następnie wybrać w regułach projektowych Routing Width lub Differential Pairs Routing.

-

Impedance Profile

- Description – wprowadź znaczący opis. To pole jest opcjonalne i będzie wyświetlane wszędzie tam, gdzie wyświetlana jest nazwa profilu impedancji.

- Type – użyj listy rozwijanej, aby wybrać typ impedancji. Dostępne opcje to Single, Differential, Single-Coplanar i Differential-Coplanar.

- Target Impedance – wprowadź impedancję, którą chcesz uzyskać.

- Target Tolerance – wprowadź tolerancję, którą chcesz uzyskać. Należy skonsultować się z producentem płytek, aby ustalić realistyczną wartość tolerancji, którą może on zapewnić.

-

Transmission Line

- Trace inverted – włącz tę opcję, aby odwrócić ścieżkę, jak pokazano w panelu Properties. Ta opcja jest taka sama jak opcja Copper Orientation wyświetlana, gdy aktywna jest karta Stackup, i określa kierunek, w którym miedź jest laminowana na rdzeń. Orientacja miedzi definiuje kierunek, w którym miedź wystaje od podłoża. Można też myśleć o tym jako o kierunku, z którego miedź jest trawiona — od góry lub od dołu.

-

Etch – współczynnik trawienia to

= T/[(W1-W2)/2], co zmniejsza całkowitą powierzchnię przekroju ścieżki o kwadrat grubości miedzi. Skonsultuj się z producentem płytek w sprawie informacji o Etch tworzonym przez jego procesy.

-

Width (W1) / (W2) – W1 to szerokość prowadzonej ścieżki, W2 to szerokość górnej powierzchni tej ścieżki po wytrawieniu, z uwzględnieniem współczynnika Etch. Dostępna jest funkcja obliczeń w przód/wstecz dla szerokości ścieżki. Domyślnie szerokość jest obliczana na podstawie wprowadzonej wartości Target Impedance (obliczenie w przód). Ta szerokość może mieć wartość, której producent nie będzie w stanie uzyskać, na przykład 5.978, i będzie oczekiwał bardziej sensownej wartości, takiej jak 6.0. Możesz wpisać 6.0 w polu Width i nacisnąć Enter na klawiaturze, aby ponownie obliczyć wyliczone wartości (Impedance, Deviation itd.). Przycisk

zmieni kolor na szary (stanie się nieaktywny) i przejdziesz do trybu obliczeń wstecz. Jeśli klikniesz przycisk, aby go uaktywnić, ponownie przejdziesz do trybu obliczeń w przód, a Width (W1) wróci do wartości obliczonej. Ta funkcja pozwala analizować realistyczne, możliwe do wyprodukowania opcje szerokości. Ręczne wprowadzenie wartości dla W2 zaktualizuje współczynnik trawienia odpowiednio do tej wartości.

zmieni kolor na szary (stanie się nieaktywny) i przejdziesz do trybu obliczeń wstecz. Jeśli klikniesz przycisk, aby go uaktywnić, ponownie przejdziesz do trybu obliczeń w przód, a Width (W1) wróci do wartości obliczonej. Ta funkcja pozwala analizować realistyczne, możliwe do wyprodukowania opcje szerokości. Ręczne wprowadzenie wartości dla W2 zaktualizuje współczynnik trawienia odpowiednio do tej wartości.

- Impedance – oprogramowanie oblicza impedancję na podstawie właściwości materiałów użytych do wykonania płytki (miedź, rdzeń i prepreg) oraz pola przekroju ścieżki (określonego przez szerokość, grubość i współczynnik trawienia ścieżki).

- Deviation – jest to miara różnicy między tym, co było zamierzone (impedancja docelowa), a tym, co uzyskano (impedancja obliczona). Oprogramowanie oblicza odchylenie impedancji (to, co faktycznie zostanie uzyskane na podstawie wprowadzonych materiałów i wymiarów) na podstawie właściwości materiałów użytych do wykonania płytki (miedź, rdzeń i prepreg) oraz pola przekroju ścieżki (określonego przez szerokość, grubość i współczynnik trawienia ścieżki).

- Delay – jest to czas potrzebny, aby sygnał przemieścił się od nadajnika do odbiornika.

- Inductance – kalkulator impedancji używa wartości Impedance do obliczenia indukcyjności na jednostkę długości.

- Capacitance – kalkulator impedancji używa wartości Impedance do obliczenia pojemności na jednostkę długości.

-

Board

- Stack Symmetry – włącz, aby dodawać warstwy w dopasowanych parach wyśrodkowanych wokół środkowej warstwy dielektrycznej. Po włączeniu stos warstw jest natychmiast sprawdzany pod kątem symetrii względem centralnej warstwy dielektrycznej. Jeśli jakakolwiek para warstw znajdujących się w równej odległości od centralnej warstwy odniesienia dielektryka nie jest identyczna, otworzy się okno dialogowe Stack is not symmetric dialog.

- Library Compliance – po włączeniu, dla każdej warstwy wybranej z Material Library bieżące właściwości warstwy są sprawdzane względem wartości definicji tego materiału w bibliotece.

- Substack – te informacje dotyczą aktualnie wybranego podstosu (warstwy, dielektryk, grubości itp.). Po przełączeniu z jednego podstosu na inny informacje te będą odpowiednio aktualizowane (dla aktualnie wybranego podstosu).

- Stack Name – wprowadź znaczącą nazwę podstosu. To pole jest przydatne, gdy obszar stosu warstw X/Y ma przypisany podstos warstw.

- Is Flex – włącz, jeśli podstos jest elastyczny.

- Layers – łączna liczba warstw.

- Dielectrics – łączna liczba dielektryków.

- Conductive Thickness – grubość warstwy(‑w) przewodzącej(‑ych). Miedziane warstwy sygnałowe są określane jako warstwy przewodzące.

- Dielectric Thickness – grubość warstwy(‑w) dielektrycznej(‑ych).

- Total Thickness – całkowita grubość płytki.

- Other

-

Roughness – pokazuje chropowatość warstw przewodzących.

- Model Type – preferowany model do obliczania wpływu chropowatości powierzchni (więcej informacji o różnych modelach znajduje się w artykułach poniżej). Dotyczy wszystkich warstw miedzi w stosie (czy powinno to być w podstosie?).

- Surface Roughness – wartość chropowatości powierzchni (dostępna u producenta PCB). Wprowadź wartość od 0 do 10 µm, domyślnie 0,1 µm

- Roughness Factor – charakteryzuje oczekiwany maksymalny wzrost strat przewodnika spowodowany efektem chropowatości. Wprowadź wartość od 1 do 100; wartość domyślna to 2.

Konfigurowanie reguł projektowych

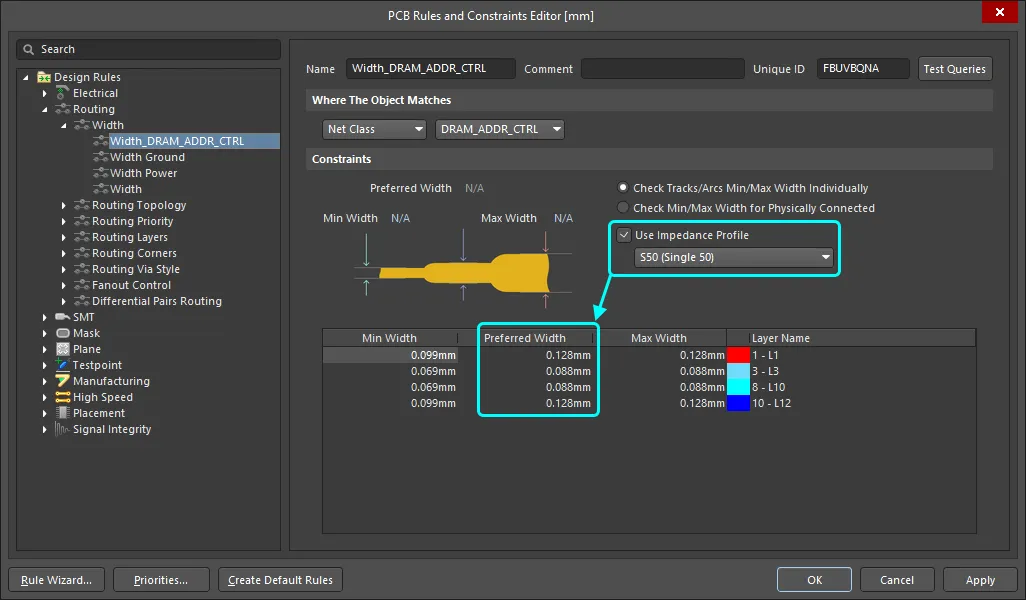

Impedancja ścieżki jest określana przez szerokość i wysokość ścieżki oraz właściwości otaczających materiałów dielektrycznych. Na podstawie właściwości materiałów zdefiniowanych w Layer Stack Manager wymagane szerokości ścieżek są obliczane podczas tworzenia każdego profilu impedancji. W zależności od właściwości materiałów szerokość może się zmieniać przy zmianie warstwy prowadzenia. To wymaganie, polegające na zmianie szerokości przy zmianie warstw prowadzenia, jest automatycznie obsługiwane przez odpowiednią regułę projektową routingu skonfigurowaną w PCB Rules and Constraints Editor (Design » Rules).

W przypadku większości projektów płytek określony zestaw sieci będzie prowadzony z kontrolowaną impedancją. Typowym podejściem jest utworzenie klasy sieci lub klasy par różnicowych obejmującej te sieci, a następnie utworzenie reguły routingu, która jest skierowana do tej klasy, jak pokazano na poniższych ilustracjach.

Zwykle ręcznie definiuje się Min, Max i Preferred Widths, albo w górnych ustawieniach ograniczeń, aby zastosować je do wszystkich warstw, albo indywidualnie dla każdej warstwy w siatce warstw. W przypadku routingu z kontrolowaną impedancją zamiast tego włącza się opcję Use Impedance Profile, a następnie wybiera wymagany Profil impedancji z listy rozwijanej. Po wykonaniu tej czynności obszar Constraints reguły ulegnie zmianie. Pierwszą zauważalną zmianą będzie to, że obszar dostępnych warstw nie będzie już pokazywał wszystkich warstw sygnałowych na płytce. Będzie teraz pokazywał tylko warstwy włączone w wybranym Profilu impedancji. Wartości Preferred Width (oraz odstęp pary różnicowej) zostaną zaktualizowane tak, aby odzwierciedlały szerokości (i odstępy) obliczone dla każdej warstwy. Tych wartości Preferred nie można edytować, ale wartości Min i Max już tak. Ustaw je na odpowiednio mniejsze/większe wartości. Sieci można następnie prowadzić interaktywnie w zwykły sposób.

Reguła projektowa szerokości routingu

Dla sieci jednostronnych szerokość routingu jest definiowana przez regułę projektową Routing Width.

Po wybraniu opcji Use an Impedance Profile dostępne warstwy i wartości Preferred Width są kontrolowane przez wybrany profil.

Po wybraniu opcji Use an Impedance Profile dostępne warstwy i wartości Preferred Width są kontrolowane przez wybrany profil.

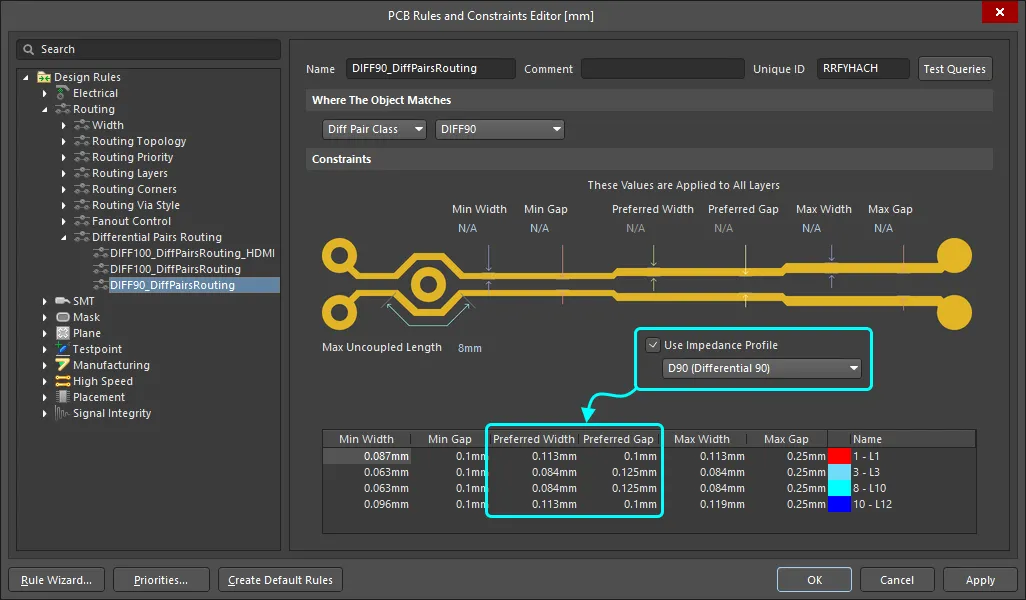

Reguła projektowa routingu par różnicowych

Routing par różnicowych jest kontrolowany przez regułę projektową Differential Pair Routing.

Dla pary różnicowej dostępne warstwy, Preferred Width i Preferred Gap są kontrolowane przez wybrany profil.

Dla pary różnicowej dostępne warstwy, Preferred Width i Preferred Gap są kontrolowane przez wybrany profil.

► Dowiedz się więcej o Differential Pair Routing

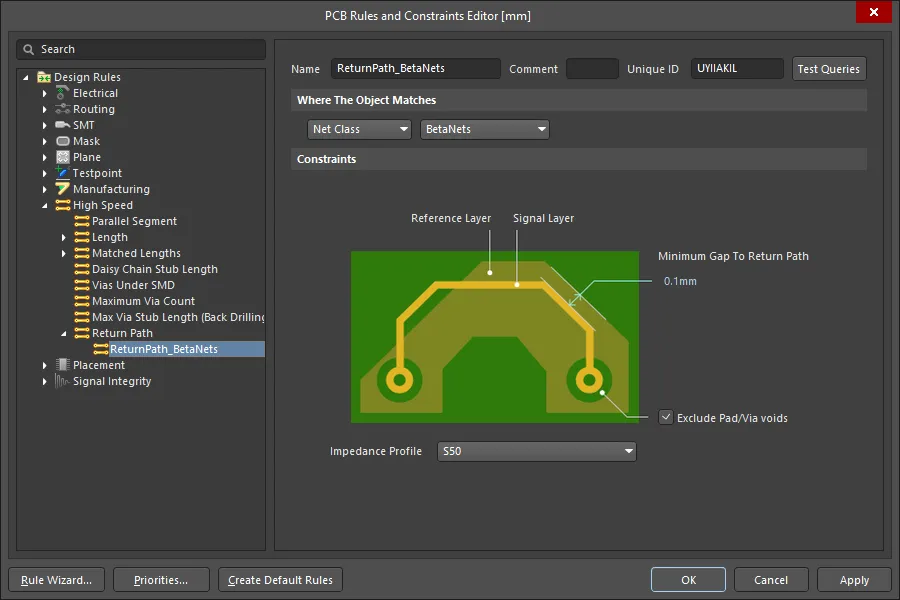

Reguła projektowa ścieżki powrotnej

Przerwy lub przewężenia w ścieżce powrotnej mogą być wykrywane przez regułę projektową Return Path. Reguła projektowa Return Path sprawdza ciągłość ścieżki powrotu sygnału na wyznaczonej warstwie(‑wach) odniesienia powyżej lub poniżej sygnału(‑ów) objętych regułą. Ścieżka powrotna może być utworzona z wypełnień, regionów i pól polygon pour umieszczonych na referencyjnej warstwie sygnałowej lub warstwie plane.

Warstwy ścieżki powrotnej to warstwy odniesienia zdefiniowane w Impedance Profile wybranym w regule projektowej Return Path. Warstwy te są sprawdzane, aby upewnić się, że określone Minimum Gap (szerokość poza krawędzią sygnału) istnieje wzdłuż ścieżki sygnału. Dodaj nową regułę projektową Return Path w kategorii reguł High Speed.

Warstwy ścieżki powrotnej są zdefiniowane w wybranym Impedance Profile, a szerokość ścieżki (poza krawędzią sygnału) jest definiowana przez Minimum Gap.

Warstwy ścieżki powrotnej są zdefiniowane w wybranym Impedance Profile, a szerokość ścieżki (poza krawędzią sygnału) jest definiowana przez Minimum Gap.

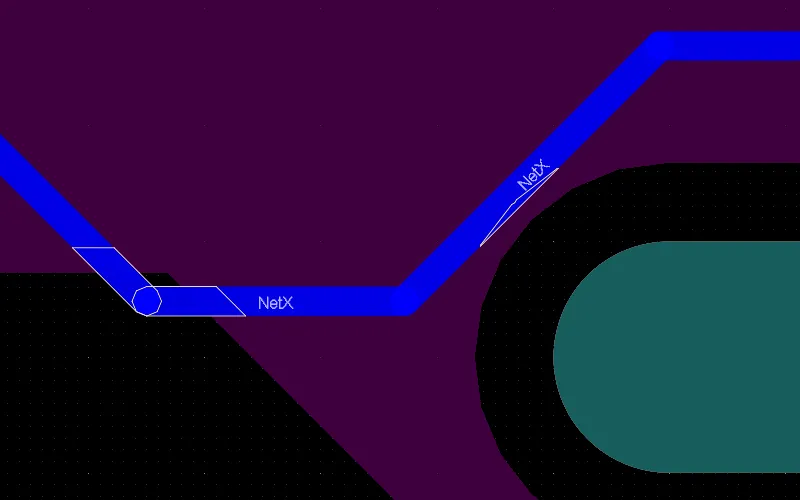

Poniższy obraz pokazuje błędy ścieżki powrotnej wykryte dla sygnału, NetX przy ustawieniu Minimum Gap równym 0.1mm. Błędy Return Path można łatwiej zlokalizować, konfigurując DRC Violation Display Style tak, aby pokazywał Violation Details, ale nie Violation Overlay (pokaż obraz) w oknie dialogowym Preferences. Spowoduje to podświetlenie dokładnych miejsc, w których reguła nie została spełniona, zamiast całych obiektów naruszających regułę.

► Dowiedz się więcej o High Speed Design in Altium Designer

Prowadzenie sieci z wymaganą impedancją

Podczas prowadzenia płytki i zmiany warstw oprogramowanie automatycznie dostosuje szerokość ścieżki do rozmiaru potrzebnego do uzyskania określonej impedancji. To interaktywne prowadzenie z kontrolowaną impedancją znacznie upraszcza projektowanie PCB z kontrolowaną impedancją.

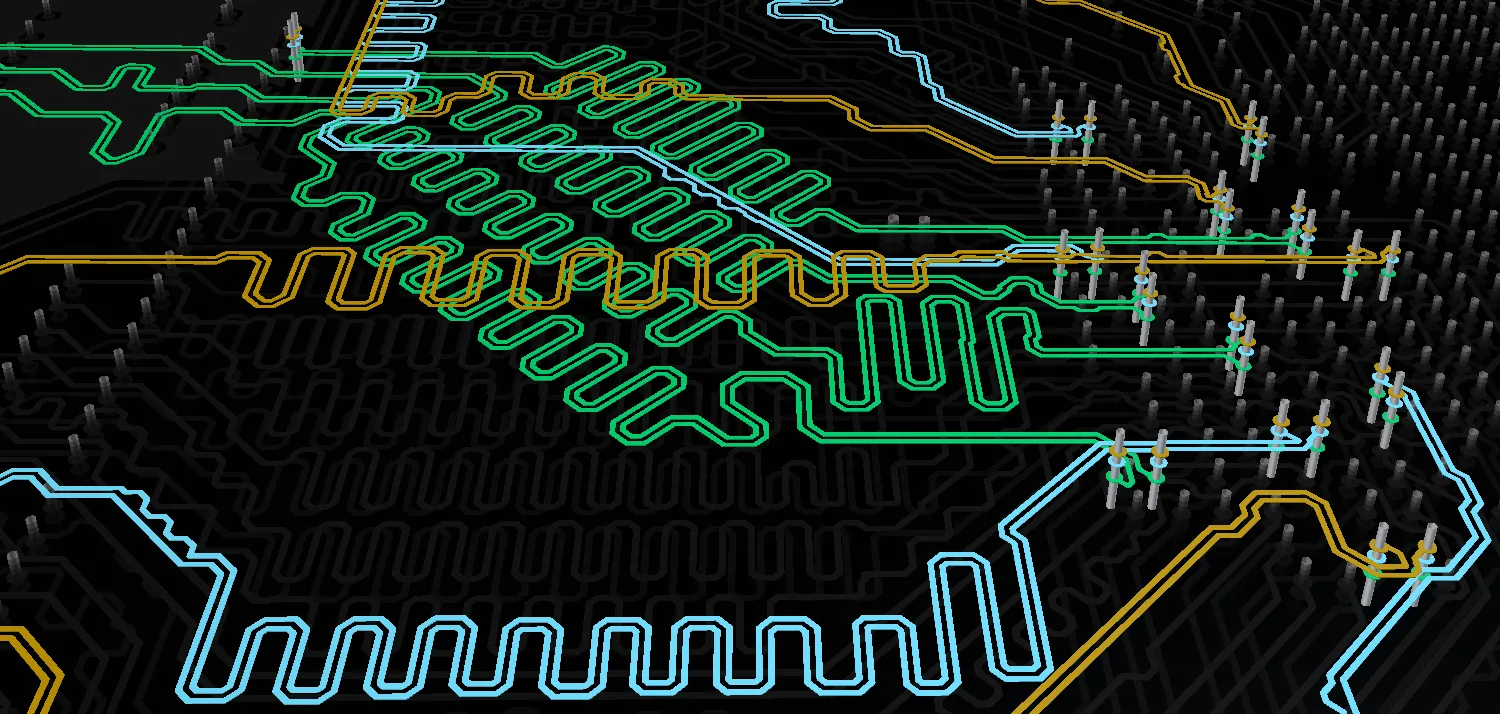

Dostrajanie długości ścieżek

Dwa z głównych wyzwań podczas prowadzenia projektu wysokiej szybkości to kontrolowanie impedancji ścieżek oraz dopasowanie długości krytycznych sieci. Routing z kontrolowaną impedancją zapewnia, że sygnał opuszczający pin wyjściowy jest poprawnie odbierany przez docelowe piny wejściowe. Dopasowanie długości ścieżek zapewnia, że sygnały krytyczne czasowo docierają do swoich pinów docelowych w tym samym czasie. Strojenie i dopasowywanie długości ścieżek jest również istotnym elementem routingu par różnicowych.

Do routingu dodano wzory akordeonowe, aby zapewnić dopasowanie długości par różnicowych.

Do routingu dodano wzory akordeonowe, aby zapewnić dopasowanie długości par różnicowych.

Polecenia Interactive Length Tuning i Interactive Diff Pair Length Tuning (menu Route) zapewniają dynamiczny sposób optymalizacji i kontrolowania długości sieci lub par różnicowych, umożliwiając wstawianie wzorów falowych o zmiennej amplitudzie (akordeonów) zgodnie z dostępną przestrzenią, regułami i przeszkodami w projekcie.

► Dowiedz się więcej o Length Tuning

Testowanie integralności sygnałowej poprowadzonej płytki

W taki sam sposób, w jaki testowano sieci podczas tworzenia schematu przy założonej długości i impedancji routingu, po zakończeniu routingu należy powtórzyć ten proces na płytce, aby sprawdzić potencjalne niedopasowania impedancji i problemy z odbiciami. Uruchom polecenie Signal Integrity z menu Tools edytora PCB. Ponieważ PCB jest częścią projektu, właściwości materiałów i wymiary zdefiniowane w Layer Stack Manager oraz rzeczywiste szerokości ścieżek na płytce zostaną użyte do obliczenia impedancji wykorzystywanych w testach integralności sygnałowej.

Uzyskanie określonych impedancji

Poza iteracyjnym procesem dostrajania wymiarów, przez który przechodzisz, aby uzyskać prawidłowe impedancje, istnieją inne czynniki wpływające na końcową impedancję uzyskaną na wyprodukowanej PCB. Obejmują one spójność i stabilność materiału dielektrycznego użytego w PCB, a także spójność i jakość procesu trawienia. Jeśli potrzebujesz PCB z kontrolowaną impedancją, powinieneś omówić to z producentem PCB. Niektórzy producenci mogą doradzić w zakresie geometrii ścieżek, jeśli dostarczysz im preferowany stackup. Wielu z nich będzie również w stanie dodać kupon testowy impedancji na każdym produkowanym panelu — można go użyć do pomiaru rzeczywistych impedancji uzyskanych na płytce.

Dodatkowe materiały i zasoby

Ten artykuł stanowi wprowadzenie do tematu integralności sygnałowej i projektowania PCB z kontrolowaną impedancją. Skorzystaj z poniższych linków, aby dowiedzieć się więcej i uzyskać dostęp do materiałów opracowanych przez uznanych ekspertów branżowych.

Tłumaczenie SI

Tłumaczenie SI