Тестирование — важная часть процесса изготовления печатной платы. После изготовления плату обычно проверяют, чтобы убедиться в отсутствии коротких замыканий и обрывов цепей. После полной установки всех компонентов плату нередко тестируют повторно, чтобы подтвердить целостность сигналов и работоспособность устройства. Чтобы облегчить этот процесс, принципиально полезно иметь на плате схему точек — Testpoints — к которым тестовое оборудование может прикасаться щупами и выполнять необходимые проверки.

Расположение тестпоинтов на плате зависит от факторов, включая режим тестирования (в том числе тестирование «голой» платы после изготовления, внутрисхемное тестирование после сборки и т. п.) и метод тестирования (включая автоматизированное тестирование с использованием flying probe и фикстур типа bed-of-nails, ручное тестирование и т. п.). Например, при тестировании «голой» платы после изготовления плата не заселена компонентами, поэтому все площадки и переходные отверстия являются «доступными» для назначения тестпоинтов. Однако при внутрисхемном тестировании после сборки используемые места для тестпоинтов почти всегда будут другими. Поскольку плата заселена, у вас может больше не быть доступа щупом к площадкам компонентов и уж точно не будет доступа к площадкам и переходным отверстиям под компонентом!

Altium Designer предоставляет мощную систему для работы с тестпоинтами и повышения тестопригодности ваших плат, позволяя при необходимости отдельно назначать тестпоинты для тестирования «голой» платы после изготовления и/или для внутрисхемного тестирования после сборки. Тестпоинты можно назначать вручную или более упорядоченно и автоматически, используя диалог Testpoint Manager dialog.

Продумывание стратегии тестпоинтов

Прежде чем переходить к назначению площадок и переходных отверстий в качестве мест тестпоинтов, полезно сделать шаг назад и подумать, что именно требуется. Ниже приведены лишь некоторые рекомендации, которые стоит учесть при определении стратегии внедрения тестпоинтов в проект:

- При выборе стороны платы, на которой будут разрешены тестпоинты, следует учитывать процессы тестирования и используемые фикстуры. Например, будет ли плата прозваниваться только с нижней стороны, только с верхней или с обеих сторон.

- Тестпоинт под компонентом (на той же стороне платы, что и компонент) обычно используется на этапе тестирования «голой» платы. Это следует учитывать при планировании мест тестпоинтов для тестирования собранной платы.

- Рекомендуется располагать все тестпоинты только на одной стороне платы, при необходимости используя переходные отверстия, чтобы этого добиться. Причина в том, что двухсторонняя (двухголовочная) тестовая оснастка обходится дороже, чем односторонняя (одноголовочная).

- Чем более нестандартен и сложен рисунок тестпоинтов, тем дороже будет настроить оснастку для тестирования платы. Лучшая философия — разработать методологию, обеспечивающую универсальную тестопригодность. Хорошо отработанная и адаптируемая политика тестпоинтов позволит эффективно и экономично тестировать разные проекты.

- Следует тщательно продумать требования к тентингу переходных отверстий в проекте. Тентинг переходного отверстия, назначенного как тестпоинт, фактически заблокирует контакт тестового щупа. Даже частичный тентинг с использованием паяльной маски Liquid Photo Imageable (LPI) вызовет проблемы с контактом, поскольку жидкая маска будет стремиться «утекать» через отверстие. Для временного тентинга таких назначенных переходных отверстий действительно можно использовать снимаемую (peelable) паяльную маску, но это часто оказывается довольно дорого.

- Тесно консультируйтесь с производством и сборочным подрядчиком, чтобы при задании тестпоинтов были учтены любые специфические параметры. Это могут быть зазоры «тестпоинт–тестпоинт» и «тестпоинт–компонент», которые могут быть строже, чем обычные зазоры при размещении и трассировке.

В следующих разделах подробнее рассматриваются тестирование после изготовления и тестирование после сборки, включая конкретные ограничения и соображения по тестпоинтам для каждого случая.

Тестирование после изготовления (Fabrication Testing)

Тестирование после изготовления относится к проверке печатной платы на предсборочном этапе производства, до установки каких-либо компонентов на плату. Поэтому его часто называют тестированием «голой» платы (bare-board testing). Такой метод тестирования обычно включает использование устройства flying probe для проверки «сеть за сетью» (net-by-net). По сути, два щупа программируются на совместную работу: один подаёт импульсный сигнал в сеть, а другой обнаруживает наличие (или отсутствие) этого сигнала.

Два распространённых сценария тестирования «голой» платы:

- Проверка того, что намеренно непрерывная медь от конца до конца проводит чистый сигнал (при максимальном допустимом пороге импеданса) без обрывов.

- Проверка того, что сети не замкнуты друг на друга.

Testpoint Location Constraints

- Выделенные площадки/переходные отверстия под тестпоинты обычно не требуются для тестирования после изготовления. Поскольку плата ещё не загружена компонентами, щупы имеют свободный доступ к площадкам компонентов. Так как на этом этапе площадки, как правило, не покрыты паяльной маской, тестпоинты обычно располагают непосредственно на самих площадках.

- Тестирование flying probe не ограничено сеткой, поскольку такие устройства способны позиционироваться с высокой точностью.

- Каждая пара точек ограничена минимальным расстоянием — из‑за физических размеров головок щупов.

Exceptions and other Considerations

- Для компонентов с малым шагом выводов может быть невозможно (или даже непрактично) касаться щупом одной площадки компонента. Такие медные элементы могут быть микроскопическими и хрупкими, поэтому иногда рекомендуется избегать контакта с тестовыми щупами. В таких случаях дизайнеру имеет смысл добавить на плату выделенные тестовые площадки/переходные отверстия.

- При тестировании «голой» платы также может использоваться фикстура bed-of-nails. Обычно это характерно для крупносерийного производства, где применение такой оснастки требует меньше времени на тестирование, чем flying probe. Однако тестирование bed-of-nails может накладывать более жёсткие ограничения на расположение тестпоинтов и, если оснастка не является индивидуально изготовленной, часто требует, чтобы тестпоинты соответствовали определённой сетке.

- Бывают случаи, когда flying probe не тестирует совместно определённые пары точек. Обычно это происходит, когда нет опасности короткого замыкания (или перекрёстных наводок) между сетями, поскольку сети не соседствуют друг с другом (все объекты обеих сетей взаимно разделены своим физическим расположением).

Тестирование после сборки (Assembly Testing)

Тестирование после сборки относится к проверке печатной платы на послесборочном этапе производства, после того как плата заселена всеми компонентами, указанными в соответствующей ведомости материалов (BOM). Поэтому его часто называют внутрисхемным или электрическим тестированием (in-circuit/electrical testing). Такой метод тестирования обычно включает (но вовсе не ограничивается!) использованием вручную сконфигурированной фикстуры bed-of-nails. В зависимости от типа теста, выполняемого с помощью оснастки, плата может быть запитана или нет.

Два распространённых сценария внутрисхемного тестирования после сборки:

- Одновременно касаться щупом одного выделенного тестпоинта для каждой сети (или интересующей сети). Это делается путём подачи импульса в каждую точку по отдельности и фиксации результатов приёма сигнала всеми остальными щупами.

- Проверка конкретных компонентов/шин, чтобы убедиться, что само устройство работает корректно. Это специализированные тесты, которые могут выполняться различными методами. В простейшем случае фикстура bed-of-nails может использоваться для проверки между площадками компонента.

Testpoint Location Constraints

- Расположение тестпоинтов обычно должно соответствовать требованию минимального шага/расстояния. Тестовое оборудование, например головки щупов в фикстуре bed-of-nails, имеет габариты, ограничивающие их взаимную близость. Если не используется индивидуальная оснастка, расположение тестпоинтов часто требуется на определённой сетке. Изготовление индивидуальной оснастки дороже и занимает больше времени, чем настройка многоразовой фикстуры bed-of-nails.

- Может требоваться размещать тестпоинты с соблюдением минимального зазора относительно корпусов компонентов. Головки щупов большинства фикстур обычно имеют больший диаметр ближе к оснастке и сужаются по мере приближения к стержню щупа. Более высокие компоненты требуют большего зазора. Поэтому лучше учитывать максимальную высоту компонентов на плате и задавать общий зазор по корпусу, исходя из этого наихудшего случая.

- Может требоваться размещать тестпоинты с соблюдением минимального зазора относительно края платы. Процесс контакта платы парой щупов flying probe или массивом щупов bed-of-nails может быть жёстким для самой платы, и под нагрузкой автоматизированного тестирования плата может в некоторой степени прогибаться. По этой причине риск повреждения тонких, хрупких плат снижается, когда тестпоинты расположены на расстоянии от краёв платы.

- Как правило, для каждой сети на этапе проектирования требуется добавить выделенную, доступную для щупа площадку/переходное отверстие тестпоинта по нескольким причинам:

- Оголённые медные площадки компонентов обычно становятся недоступными из‑за установленных компонентов.

- Если плата специально не спроектирована с учётом тестирования, площадки компонентов и переходные отверстия, скорее всего, не будут располагаться на требуемой сетке тестпоинтов.

- Даже если площадка компонента сама по себе кажется подходящей в качестве места тестпоинта, ограничения по зазору до корпуса компонента часто не позволяют её использовать.

Exceptions and other Considerations

- Хотя фикстуры bed-of-nails — распространённый метод тестирования после сборки, он далеко не единственный. Среди различных альтернатив есть случаи, когда используются устройства flying probe — с осторожностью, чтобы не столкнуться с установленными компонентами.

- При выполнении электрического теста конкретного компонента контактные площадки компонента могут быть в той или иной степени доступны для тестового щупа. Однако важно учитывать, что корпус компонента часто закрывает центральную часть таких площадок. Иными словами, после сборки платы доступная часть площадки редко включает её центральную точку.

Поддержка тестовых точек на площадках и переходных отверстиях

Altium Designer обеспечивает полную поддержку тестовых точек, позволяя задавать площадки (сквозные или SMD) и/или переходные отверстия (via), которые будут использоваться как места тестовых точек при тестировании на этапе изготовления и/или сборки. Pad or Via назначается для использования в качестве тестовой точки путём задания соответствующих свойств тестовой точки и ответа на два ключевых вопроса:

- Должна ли площадка/переходное отверстие использоваться как тестовая точка для изготовления и/или сборки?

- С какой стороны платы площадка/переходное отверстие должно использоваться как тестовая точка — Top, Bottom или с обеих сторон?

Эти свойства можно найти в панели Properties, когда в рабочей области проектирования выбран объект площадки (см. Pad Properties) или переходного отверстия (см. Via Properties) соответственно.

Выбранная площадка или переходное отверстие задаётся для использования в качестве тестовой точки через соответствующие доступные для него параметры в панели Properties.

Выбранная площадка или переходное отверстие задаётся для использования в качестве тестовой точки через соответствующие доступные для него параметры в панели Properties.

Чтобы упростить процесс и исключить необходимость вручную задавать свойства тестовых точек для площадок/переходных отверстий, Altium Designer предоставляет метод автоматического назначения тестовых точек на основе определённых правил проектирования с использованием

Testpoint Manager. Это автоматическое назначение в каждом случае устанавливает соответствующие свойства тестовой точки для площадки/переходного отверстия. Также доступна возможность вручную задавать тестовые точки — по сути, «вручную» на уровне отдельных площадок/переходных отверстий — что даёт полный контроль над применяемой на плате схемой тестовых точек.

При открытии PCB-проектов, созданных в версии ПО до релиза Summer 09, любые включённые параметры тестовых точек станут включёнными Fabrication testpoint options.

Правила проектирования тестовых точек

Ограничения PCB-проекта следует продумать и реализовать как хорошо отлаженный набор design rules. Чтобы реализовать успешную схему тестовых точек — когда все определённые тестовые точки доступны и могут использоваться в тестировании голой платы и/или внутрисхемном тестировании — необходимо задать управляющие ограничения. Для этого в системе Design Rules редактора PCB можно определить следующие типы правил:

Открывайте и задавайте правила этих типов в диалоге PCB Rules and Constraints Editor dialog (Design » Rules).

Определяйте отдельные правила проектирования, чтобы ограничить, какие площадки и/или переходные отверстия в проекте могут использоваться как тестовые точки для изготовления (Fabrication) и для сборки (Assembly), а также какие цепи (nets) требуют тестовых точек.

Определяйте отдельные правила проектирования, чтобы ограничить, какие площадки и/или переходные отверстия в проекте могут использоваться как тестовые точки для изготовления (Fabrication) и для сборки (Assembly), а также какие цепи (nets) требуют тестовых точек.

Правила Testpoint Style и Usage идентичны по набору ограничений для обоих режимов тестирования (изготовление и сборка). Правило стиля по сути задаёт ограничения, которым должна соответствовать площадка или переходное отверстие, чтобы рассматриваться как кандидат на выбор в качестве места тестовой точки. Правило использования задаёт, какие цепи требуют тестовую точку.

Ограничения по умолчанию для правил Testpoint Usage (сверху) и Testpoint Style (снизу).

Ограничения по умолчанию для правил Testpoint Usage (сверху) и Testpoint Style (снизу).

При определении правила стиля область действия (scope) правила можно быстро сформировать так, чтобы она нацеливалась на точные объекты площадок и/или переходных отверстий для рассмотрения в качестве тестовых точек, используя параметры, доступные в области Rule Scope Helper.

Правила проектирования тестовых точек используются Testpoint Manager, автотрассировщиком (Autorouter), процессами Online и Batch DRC, а также при генерации выходных данных.

Существуют правила Fabrication и Assembly Testpoint Style и Testpoint Usage по умолчанию. Следует проверить, соответствуют ли эти правила требованиям вашей платы, и при необходимости внести изменения. Если требуется несколько правил одного типа, используйте приоритет правил проектирования, чтобы правила с более узкой областью действия применялись первыми (например, при запуске DRC).

Чтобы Testpoint Manager мог успешно назначать тестовые точки, должно always существовать как минимум одно соответствующее правило Testpoint Style с областью действия All.

При открытии PCB-проектов или импорте правил проектирования, созданных в версии ПО до релиза Summer 09, правила Testpoint Style станут правилами Fabrication Testpoint Style, а правила Testpoint Usage станут правилами Fabrication Testpoint Usage.

Управление тестовыми точками

Ручное назначение тестовых точек может быть кропотливой и трудоёмкой задачей, а на сложной плате, содержащей сотни компонентов (и на обеих сторонах платы), — тем более. Для упрощённого управления тестовыми точками в проектах плат Altium Designer оснащает PCB Editor инструментом Testpoint Manager. Testpoint Manager позволяет назначать тестовые точки — для тестирования голой платы на этапе изготовления и/или внутрисхемного тестирования при сборке — в автоматическом режиме на основе определённых правил проектирования. Это автоматическое назначение в каждом случае устанавливает соответствующие свойства тестовой точки для площадки/переходного отверстия.

Доступ осуществляется через команду Tools » Testpoint Manager в главном меню.

Быстро и эффективно управляйте требованиями к тестовым точкам для изготовления и сборки с помощью Testpoint Manager.

Быстро и эффективно управляйте требованиями к тестовым точкам для изготовления и сборки с помощью Testpoint Manager.

Используйте диалог для автоматического назначения и очистки тестовых точек из одного удобного места. Список всех цепей (nets) в проекте приводится в области Testpoint Net Status с индикацией статуса покрытия тестовыми точками — Complete или Incomplete — как для тестирования голой платы (fabrication), так и для внутрисхемного тестирования при сборке (assembly). Нажимайте кнопки Fabrication Testpoints или Assembly Testpoints либо щёлкните правой кнопкой мыши в таблице, чтобы получить доступ к командам назначения или очистки соответствующего типа тестовой точки. Обратите внимание: вы можете вручную выбирать цепи в верхней области диалога, чтобы выборочно назначать/очищать тестовые точки.

Независимо от того, назначаются ли тестовые точки для части или для всех цепей проекта, Testpoint Manager следует правилам стиля и использования, определённым для тестовых точек изготовления и сборки. Чтобы увидеть порядок, в котором выполняется поиск подходящих объектов, нажмите кнопку Search Order.

Чтобы изменить порядок, щёлкните правой кнопкой мыши по элементу в списке порядка поиска и используйте команды всплывающего меню либо сочетания Shift+Up Arrow и Shift+Down Arrow, чтобы переместить элемент вверх или вниз по списку.

Если у цепи назначена тестовая точка, нарушающая применимое правило проектирования тестовых точек, это будет указано

Illegal в области

Testpoint Net Status диалога

Testpoint Manager. Используйте функциональность Design Rule Check редактора PCB, чтобы

проверить корректность назначенных тестовых точек.

Область Status Summaries предоставляет полную сводку статуса тестовых точек для платы для обоих режимов тестирования. Эта область обновляется после каждого действия назначения или очистки. Для более детальной информации используйте область Assignment Results. Она, например, покажет количество задействованных верхних/нижних площадок/переходных отверстий при назначении/очистке, а также укажет на ошибки.

Проверка корректности тестовых точек

Определённые правила тестовых точек для изготовления и сборки учитываются в рамках функции Design Rule Checking (DRC) редактора PCB. Проверку Online и/или Batch DRC для различных типов правил можно включить в диалоге Design Rule Checker dialog (Tools » Design Rule Check).

Включайте правила проектирования тестовых точек в процессы Online или Batch DRC.

Включайте правила проектирования тестовых точек в процессы Online или Batch DRC.

Поля запросов, связанные с тестовыми точками

Для поддержки различных тестовых точек изготовления и сборки, которые могут быть назначены в проекте, доступны следующие ключевые слова для использования при нацеливании на тестовые точки с помощью логических выражений запросов. Каждое из них можно найти в категории PCB Functions - Fields при использовании Query Helper:

IsAssyTestpoint - является тестовой точкой сборки (assembly).IsFabTestpoint - является тестовой точкой изготовления (fabrication).IsTestpoint - является тестовой точкой на стороне Top или Bottom.Testpoint - является ли тестовой точкой на стороне Top или Bottom?TestpointAssy - является ли тестовой точкой сборки (assembly)?TestpointAssyBottom - является ли тестовой точкой сборки на стороне Bottom?TestpointAssyTop - является ли тестовой точкой сборки на стороне Top?TestpointBottom - является ли тестовой точкой на стороне Bottom?TestpointFab - является ли тестовой точкой изготовления (fabrication)?TestpointFabBottom - является ли тестовой точкой изготовления на стороне Bottom?TestpointFabTop - является ли тестовой точкой изготовления на стороне Top?TestpointTop - является ли тестовой точкой на стороне Top?

Создавайте логические выражения запросов, чтобы при необходимости нацеливаться на тестовые точки в проекте и возвращать их. Примеры логических выражений запросов, нацеленных на тестовые точки изготовления и сборки:

(ObjectKind = 'Pad') And (TestpointAssy = 'True')

Нацеливается на все площадки, являющиеся тестовыми точками сборки.IsPad And (TestpointAssyTop = 'True')

Нацеливается на все площадки, являющиеся тестовыми точками сборки на стороне Top.(ObjectKind = 'Pad') And (TestpointFab = 'True')

Нацеливается на все площадки, являющиеся тестовыми точками изготовления.((IsPad Or IsVia)) And (TestpointAssy = 'True')

Нацеливается на все площадки и переходные отверстия, являющиеся тестовыми точками сборки.((IsPad Or IsVia)) And IsFabTestpoint

Нацеливается на все площадки и переходные отверстия, являющиеся тестовыми точками изготовления.

Формирование отчётов по тестовым точкам

Altium Designer включает специализированные генераторы отчётов для формирования отчётов по тестовым точкам изготовления и сборки соответственно. Эти два генератора отчётов используют соответствующие свойства тестовых точек для примитивов площадок и переходных отверстий в проекте.

Отчёт по тестовым точкам изготовления будет использовать только настройки Fabrication testpoint settings для площадок и переходных отверстий. Отчёт по тестовым точкам сборки будет использовать только Assembly testpoint settings.

Отчёты можно сформировать двумя способами:

- Непосредственно из PCB-документа, используя команды File » Fabrication Outputs » Test Point Report и File » Assembly Outputs » Test Point Report.

- С помощью корректно настроенных выходных данных, определённых в файле Output Job Configuration (

*.OutJob).

Добавляйте и настраивайте выходные данные отчётов по тестовым точкам изготовления и сборки в самодостаточном и универсальном файле Output Job Configuration. После определения получайте отчёты нажатием одной кнопки!

Добавляйте и настраивайте выходные данные отчётов по тестовым точкам изготовления и сборки в самодостаточном и универсальном файле Output Job Configuration. После определения получайте отчёты нажатием одной кнопки!

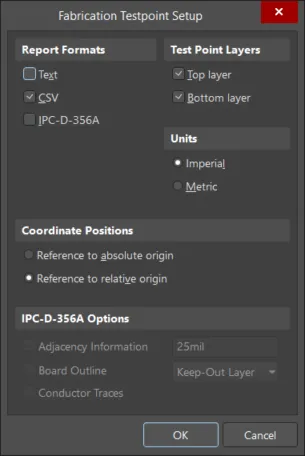

Независимо от способа формирования отчёта, сами параметры отчёта задаются в одном и том же диалоге. Для отчёта по тестовым точкам изготовления используется диалог Fabrication Testpoint Setup dialog. Для отчёта по тестовым точкам сборки используется диалог Assembly Testpoint Setup dialog. Параметры отчёта в этих диалогах идентичны.

Задавайте параметры отчёта, включая формат генерируемого файла, в соответствующем диалоге настройки отчёта.

Настройки, заданные в диалоге Testpoint Setup при генерации выходных данных напрямую из PCB, отличаются и не связаны с настройками, определёнными для того же типа выходных данных в файле Output Job Configuration. В первом случае настройки сохраняются в файле проекта, тогда как во втором — в файле Output Job.

Параметры в области Coordinate Positions диалога позволяют экспортировать координаты тестпоинтов во всех форматах отчётов относительно абсолютного начала координат платы или относительно текущего начала координат платы.

Все типы отчётов по тестпоинтам поддерживают встроенные массивы плат. При экспорте из PCB-документа, содержащего несколько встроенных массивов плат, формируется несколько файлов нетлиста IPC-D-356A.

Роль файла нетлиста IPC-D-356A

Один из трёх вариантов форматов выходных отчётов по тестпоинтам — это файл нетлиста IPC-D-356A. Обычно он используется для режима тестирования при изготовлении «голой» платы. IPC-файл затем постобрабатывается в команды, которые управляют установкой летающих щупов (flying probe).

Независимо от того, какие именно элементы явно обозначены как точки тестирования в файле IPC-D-356A, производители плат, как правило, могут использовать данные файла для выполнения нужного им типа тестирования; однако, в зависимости от обстоятельств и содержимого файла, для этого может потребоваться некоторое ручное вмешательство.