Il collaudo è una parte importante del processo di produzione della scheda. Dopo la fabbricazione, la scheda viene in genere testata per verificare l’assenza di cortocircuiti o circuiti aperti. Una volta completamente popolata con tutti i suoi componenti, la scheda viene spesso testata nuovamente per garantire l’integrità del segnale e il corretto funzionamento del dispositivo. Per agevolare questo processo, è fondamentalmente utile disporre di uno schema di punti sulla scheda - Testpoints - che l’apparecchiatura di test possa sondare ed eseguire i test richiesti.

La posizione dei testpoint su una scheda dipende da fattori che includono la modalità di collaudo (tra cui il collaudo di fabbricazione della scheda nuda, il collaudo in-circuit dell’assemblaggio, ecc.) e il metodo di collaudo (tra cui il collaudo automatizzato mediante flying probe e fixture bed-of-nails, il collaudo manuale, ecc.). Ad esempio, durante il collaudo di fabbricazione della scheda nuda, la scheda non è popolata e quindi tutti i pad e le via sono “utilizzabili” ai fini dell’assegnazione dei testpoint. Le posizioni usate per i testpoint durante il collaudo in-circuit dell’assemblaggio, tuttavia, saranno quasi sempre diverse. Poiché la scheda è popolata, potresti non avere più accesso con la sonda ai pad dei componenti e certamente nessun accesso ai pad e alle via sotto un componente!

Altium Designer offre un sistema potente per gestire le esigenze relative ai testpoint e migliorare la testabilità delle schede, consentendo di assegnare separatamente i testpoint per il collaudo di fabbricazione della scheda nuda e/o per il collaudo in-circuit dell’assemblaggio, secondo necessità. I testpoint possono essere assegnati manualmente oppure, in modo più rapido e automatizzato, utilizzando la finestra di dialogo Testpoint Manager.

Considerare la strategia dei testpoint

Prima di procedere con l’assegnazione di pad e via da usare come posizioni dei testpoint, è una buona idea fermarsi un momento e riflettere su ciò che è richiesto. Di seguito sono riportati solo alcuni suggerimenti da considerare quando si definisce una strategia per incorporare i testpoint in un progetto:

- Quando si sceglie il lato della scheda su cui saranno consentiti i testpoint, occorre tenere conto dei processi di collaudo e delle fixture associate che verranno utilizzate. Ad esempio, la scheda verrà sondata solo dal lato inferiore, solo dal lato superiore oppure da entrambi i lati.

- Un testpoint sotto un componente (sullo stesso lato della scheda del componente) viene solitamente usato nella fase di collaudo della scheda nuda. Questo aspetto deve essere preso in considerazione quando si pianificano le posizioni dei testpoint per il collaudo della scheda assemblata.

- È consigliabile posizionare tutti i testpoint su un solo lato della scheda, utilizzando le via per ottenere questo risultato se necessario. Il motivo è che una fixture di test a doppia testa comporta un costo maggiore rispetto a una fixture di test a testa singola.

- Quanto più il pattern dei testpoint è non standard e complesso, tanto più costoso sarà configurare una fixture con cui testare la scheda. La filosofia migliore è sviluppare una metodologia che porti a una testabilità generica. Una politica sui testpoint ben definita e adattabile consentirà di testare progetti diversi in modo efficiente ed economico.

- Occorre valutare con attenzione eventuali requisiti di tenting delle via del progetto. Applicare il tenting a una via designata come testpoint bloccherà di fatto il contatto della sonda di test. Anche un tenting parziale mediante solder mask Liquid Photo Imageable (LPI) causerà problemi di contatto, poiché il liquido della maschera tenderà a defluire attraverso il foro della via. Una solder mask peelable può effettivamente essere usata per fornire un tenting temporaneo di tali via designate, ma questo può spesso risultare piuttosto costoso.

- Consulta attentamente i fornitori di fabbricazione e assemblaggio per assicurarti che eventuali parametri di progetto specifici siano presi in considerazione nella definizione dei testpoint. Questi potrebbero includere le distanze testpoint-testpoint e testpoint-componente, che possono essere più restrittive rispetto alle normali distanze di posizionamento e sbroglio.

Le sezioni seguenti esaminano più da vicino il collaudo di fabbricazione e quello di assemblaggio, incluse le specifiche limitazioni dei testpoint e le considerazioni associate a ciascuno.

Collaudo di fabbricazione

Il collaudo di fabbricazione riguarda il test di una scheda a circuito stampato nella fase pre-assemblaggio della produzione, prima che qualsiasi componente venga montato sulla scheda. Per questo motivo viene spesso chiamato collaudo della scheda nuda. Questo metodo di collaudo può tipicamente prevedere l’uso di un dispositivo flying probe per eseguire test net-by-net. In sostanza, due sonde vengono programmate per operare in modo coordinato: una per inviare un segnale attraverso una net e l’altra per rilevare la presenza (o l’assenza) di tale segnale.

Due scenari di test comuni per il collaudo di fabbricazione della scheda nuda sono:

- Verificare che il rame contiguo intenzionale da un’estremità all’altra trasporti un segnale pulito (al di sotto di una soglia massima di impedenza consentita) senza circuiti aperti.

- Verificare che le net non siano in cortocircuito tra loro.

Testpoint Location Constraints

- Pad/via dedicati ai testpoint di solito non sono necessari per il collaudo di fabbricazione. Poiché la scheda non è ancora caricata con i componenti, le sonde hanno libero accesso ai pad dei componenti. Dato che in questa fase i pad tendono a essere privi di solder mask, i testpoint sono tipicamente posizionati direttamente sui pad stessi.

- I test flying probe non sono vincolati da una griglia, poiché i dispositivi flying probe sono in grado di raggiungere posizioni molto precise.

- Ogni coppia di posizioni è vincolata da una separazione minima, dovuta alle dimensioni fisiche del corpo delle teste di sonda.

Exceptions and other Considerations

- Per i dispositivi a passo fine, potrebbe non essere possibile (o nemmeno pratico) sondare il pad di un singolo componente. Tali elementi in rame possono essere minuscoli e delicati, quindi occasionalmente si raccomanda di evitare il contatto con le sonde di test. In questi casi, può essere una buona idea che il progettista aggiunga alla scheda pad/via di test dedicati.

- Una fixture bed-of-nails può essere utilizzata anche durante il collaudo di fabbricazione della scheda nuda. Questo avviene tipicamente nelle produzioni ad alto volume, dove l’uso di tale fixture comporta tempi di test inferiori rispetto a un flying probe. Tuttavia, il collaudo bed-of-nails può comportare vincoli più rigidi sulla posizione dei testpoint e, se la fixture di test non è personalizzata, spesso richiederà che i testpoint siano conformi a una specifica griglia.

- Ci sono casi in cui specifiche coppie di posizioni dei testpoint non vengono testate in modo coordinato da un flying probe. Questo avviene tipicamente quando non vi è pericolo di cortocircuito (o diafonia) tra le net, poiché le net non sono adiacenti tra loro (tutti gli oggetti di entrambe le net sono reciprocamente separati dalla loro prossimità fisica).

Collaudo di assemblaggio

Il collaudo di assemblaggio riguarda il test di una scheda a circuito stampato nella fase post-assemblaggio della produzione, dopo che la scheda è stata popolata con tutti i componenti specificati nella relativa Bill of Materials (BOM). Per questo motivo viene spesso chiamato collaudo in-circuit o elettrico. Questo metodo di collaudo prevede tipicamente (ma non è affatto limitato a questo!) l’uso di una fixture bed-of-nails configurata manualmente. A seconda del tipo di test eseguito mediante la fixture, la scheda può essere alimentata oppure no.

Due scenari di test comuni per il collaudo in-circuit dell’assemblaggio sono:

- Sondare simultaneamente un testpoint dedicato per ciascuna net (o net di interesse). Questo viene fatto inviando un segnale attraverso ciascuna sonda individualmente e rilevando i risultati di ricezione del segnale da parte di tutte le altre sonde.

- Testare componenti/bus specifici per assicurarsi che il dispositivo stesso funzioni correttamente. Si tratta di test specializzati che possono essere eseguiti utilizzando una varietà di metodi di collaudo. Nel caso più semplice, una fixture bed-of-nails può essere usata per testare attraverso i pad dei componenti.

Testpoint Location Constraints

- Le posizioni dei testpoint devono tipicamente rispettare un requisito di spaziatura minima. Le apparecchiature di test, come le teste di sonda delle fixture bed-of-nails, hanno dimensioni del corpo che ne limitano la vicinanza reciproca. A meno che non venga utilizzata una fixture personalizzata, spesso è richiesto che le posizioni dei testpoint si trovino su una specifica griglia. Fabbricare una fixture personalizzata è più costoso e richiede più tempo rispetto alla configurazione di una fixture bed-of-nails riutilizzabile.

- I testpoint possono dover essere posizionati rispettando una distanza minima dai corpi dei componenti. Le teste di sonda della maggior parte delle fixture di test tendono a essere più grandi nella parte più vicina alla fixture, restringendosi fino a una dimensione minore man mano che si avvicinano allo stelo della sonda. I componenti più alti richiedono maggiore distanza. È quindi preferibile considerare l’altezza massima dei componenti sulla scheda e definire una distanza complessiva dal corpo che tenga conto di questo scenario peggiore.

- Le posizioni dei testpoint possono dover essere collocate rispettando una distanza minima dal bordo della scheda. Il processo di contatto della scheda con una coppia flying probe o con una matrice di sonde bed-of-nails può essere gravoso per la scheda stessa, che può flettersi in una certa misura sotto lo sforzo del collaudo automatizzato. Per questo motivo, il rischio di danni alle schede sottili e fragili è ridotto al minimo quando i testpoint sono posizionati a una certa distanza dai bordi della scheda.

- Di solito è necessario aggiungere in fase di progettazione un pad/via di testpoint dedicato e accessibile alla sonda per ciascuna net, per diversi motivi:

- I pad dei componenti in rame nudo sono generalmente resi inaccessibili dalla presenza dei componenti montati.

- A meno che la scheda non sia progettata specificamente tenendo conto del collaudo, è improbabile che i pad dei componenti e le via siano posizionati sulla griglia richiesta per i testpoint.

- Anche se il pad di un componente sembra di per sé adatto a essere usato come posizione di testpoint, i vincoli di distanza dal corpo del componente spesso ne impediscono l’uso.

Exceptions and other Considerations

- Sebbene le fixture bed-of-nails siano un metodo comune di collaudo di assemblaggio, non sono affatto il metodo esclusivo. Tra le varie alternative vi sono casi in cui vengono utilizzati dispositivi flying probe, con attenzione a non entrare in collisione con i componenti montati.

- Quando si esegue un test elettrico su un componente specifico, i pad del componente potrebbero essere accessibili in una certa misura da una sonda di test. Tuttavia, è importante notare che il corpo del componente spesso oscura il centro di tali pad. In altre parole, dopo l’assemblaggio della scheda, la parte accessibile del pad raramente include la posizione centrale del pad.

Supporto per i testpoint di pad e via

Altium Designer offre un supporto completo per i testpoint, consentendo di specificare pad (foro passante o SMD) e/o via da utilizzare come posizioni di testpoint nei test di fabbricazione e/o di assemblaggio. Un Pad or Via viene designato per l’uso come testpoint impostando le relative proprietà del testpoint e rispondendo a due domande chiave:

- Il pad/via deve essere utilizzato come testpoint di fabbricazione e/o di assemblaggio?

- Su quale lato della scheda il pad/via deve essere utilizzato come testpoint: Top, Bottom o entrambi?

Queste proprietà sono disponibili nel pannello Properties, quando nello spazio di progettazione è selezionato rispettivamente un oggetto pad (vedere Pad Properties) o via (vedere Via Properties).

Un pad o una via selezionati vengono specificati per l’uso come testpoint tramite le relative opzioni disponibili nel pannello Properties.

Un pad o una via selezionati vengono specificati per l’uso come testpoint tramite le relative opzioni disponibili nel pannello Properties.

Per semplificare il processo ed evitare di dover impostare manualmente le proprietà di testpoint di pad/via, Altium Designer fornisce un metodo per assegnare automaticamente i testpoint in base a regole di progettazione definite e utilizzando il

Testpoint Manager. Questa assegnazione automatica imposta, in ciascun caso, le proprietà di testpoint pertinenti per il pad/via. Hai anche la possibilità di specificare manualmente i testpoint, in sostanza definendoli singolarmente a livello di pad/via, ottenendo così il pieno controllo sullo schema di testpoint adottato per la tua scheda.

Quando si aprono progetti PCB creati con una versione del software precedente alla release Summer 09, tutte le opzioni di testpoint abilitate diventeranno opzioni di Fabrication testpoint abilitate.

Regole di progettazione dei testpoint

I vincoli di un progetto PCB dovrebbero essere studiati e implementati come un insieme ben definito di design rules. Per implementare uno schema di testpoint efficace, in cui tutti i testpoint definiti possano essere accessibili e utilizzati nell’ambito dei test della scheda nuda e/o in-circuit, è necessario stabilire vincoli di controllo. A tal fine, i seguenti tipi di regole possono essere definiti come parte del sistema di Design Rules del PCB Editor:

Accedi e definisci regole di questi tipi dalla finestra di dialogo PCB Rules and Constraints Editor dialog (Design » Rules).

Definisci regole di progettazione separate per vincolare quali pad e/o via nel progetto possono essere utilizzati come testpoint di Fabrication e di Assembly e quali net richiedono testpoint.

Definisci regole di progettazione separate per vincolare quali pad e/o via nel progetto possono essere utilizzati come testpoint di Fabrication e di Assembly e quali net richiedono testpoint.

Le regole Testpoint Style e Usage sono identiche, in termini di vincoli, tra le due modalità di test (fabrication e assembly). La regola di stile specifica essenzialmente i vincoli che un pad o una via devono soddisfare per poter essere considerati per la selezione come posizione di testpoint. La regola di utilizzo specifica quali net richiedono un testpoint.

Vincoli predefiniti per le regole Testpoint Usage (in alto) e Testpoint Style (in basso).

Vincoli predefiniti per le regole Testpoint Usage (in alto) e Testpoint Style (in basso).

Quando si definisce una regola di stile, l’ambito della regola può essere creato rapidamente per indirizzare con precisione gli oggetti pad e/o via da considerare come testpoint, utilizzando le opzioni disponibili nell’area Rule Scope Helper.

Le regole di progettazione dei testpoint vengono utilizzate dal Testpoint Manager, dall’Autorouter, dai processi DRC Online e Batch e anche durante la generazione degli output.

Esistono regole predefinite Fabrication e Assembly Testpoint Style e Testpoint Usage. È consigliabile verificare se queste regole soddisfano i requisiti della scheda e apportare le modifiche necessarie. Se sono richieste più regole dello stesso tipo, utilizza l’aspetto di priorità delle design rules per assicurarti che le regole con ambito più specifico vengano applicate per prime, ad esempio durante l’esecuzione di un DRC.

Affinché il Testpoint Manager possa assegnare correttamente i testpoint, deve always esistere almeno una regola Testpoint Style corrispondente con un ambito di All.

Quando si aprono progetti PCB o si importano design rules create con una versione del software precedente alla release Summer 09, le regole Testpoint Style diventeranno regole Fabrication Testpoint Style e le regole Testpoint Usage diventeranno regole Fabrication Testpoint Usage.

Gestione dei testpoint

L’assegnazione manuale dei testpoint può essere un lavoro lungo e laborioso, e ancora di più su una scheda complessa popolata con centinaia di componenti, su entrambi i lati della scheda. Per consentire una gestione più efficiente dei testpoint nei progetti di schede, Altium Designer mette a disposizione del PCB Editor un Testpoint Manager. Il Testpoint Manager consente di assegnare i testpoint, per i test di fabbricazione della scheda nuda e/o per i test in-circuit di assemblaggio, in modo automatico, sulla base delle design rules definite. Questa assegnazione automatica imposta, in ciascun caso, le proprietà di testpoint pertinenti per il pad/via.

L’accesso avviene scegliendo il comando Tools » Testpoint Manager dai menu principali.

Gestisci in modo rapido ed efficiente i requisiti dei testpoint di fabrication e assembly utilizzando il Testpoint Manager.

Gestisci in modo rapido ed efficiente i requisiti dei testpoint di fabrication e assembly utilizzando il Testpoint Manager.

Usa la finestra di dialogo per assegnare e cancellare automaticamente i testpoint da un’unica comoda posizione. Nell’area Testpoint Net Status viene fornito un elenco di tutte le net del progetto, con uno stato che indica la copertura dei testpoint, ossia Complete oppure Incomplete, sia per i test di fabbricazione della scheda nuda sia per i test in-circuit di assemblaggio. Fai clic sui pulsanti Fabrication Testpoints o Assembly Testpoints, oppure fai clic con il pulsante destro nella griglia, per accedere ai comandi di assegnazione o cancellazione di quel tipo di testpoint. Nota che puoi selezionare manualmente le net nella regione superiore della finestra di dialogo per assegnare/cancellare selettivamente i testpoint.

Sia che vengano assegnati testpoint per alcune o per tutte le net di un progetto, il Testpoint Manager segue le regole di stile e di utilizzo definite per i testpoint di fabrication e assembly. Per vedere l’ordine con cui vengono cercati gli oggetti validi, fai clic sul pulsante Search Order.

Per modificare l’ordine, fai clic con il pulsante destro su una voce nell’elenco dell’ordine di ricerca e usa i comandi del menu contestuale, oppure le scorciatoie Shift+Up Arrow e Shift+Down Arrow per spostarla verso l’alto o verso il basso nell’elenco.

Se una net ha un testpoint assegnato che viola una regola di progettazione dei testpoint applicabile, ciò sarà indicato

Illegal nell’area

Testpoint Net Status della finestra di dialogo

Testpoint Manager. Usa la funzionalità Design Rule Check del PCB editor per

verificare la validità dei testpoint assegnati.

L’area Status Summaries fornisce un riepilogo completo dello stato dei testpoint per la scheda, per entrambe le modalità di test. Questa area si aggiorna a ogni operazione di assegnazione o cancellazione eseguita. Per un livello di dettaglio più basso, usa l’area Assignment Results. Questa fornirà dettagli, ad esempio, sul numero di pad/via top/bottom coinvolti in un’assegnazione/cancellazione, insieme a un’indicazione degli errori.

Verifica della validità dei testpoint

Le regole definite per i testpoint di fabrication e assembly vengono seguite nell’ambito della funzionalità Design Rule Checking (DRC) del PCB Editor. Il controllo DRC Online e/o Batch può essere abilitato per i vari tipi di regole dalla finestra di dialogo Design Rule Checker dialog (Tools » Design Rule Check).

Includi le regole di progettazione dei testpoint nei processi DRC Online o Batch.

Includi le regole di progettazione dei testpoint nei processi DRC Online o Batch.

Campi di query relativi ai testpoint

A supporto dei vari testpoint di fabrication e assembly che possono essere assegnati in un progetto, sono disponibili le seguenti parole chiave da utilizzare quando si indirizzano i testpoint tramite espressioni logiche di query. Ognuna delle seguenti si trova nella categoria PCB Functions - Fields, quando si utilizza il Query Helper:

IsAssyTestpoint - è un testpoint di assembly.IsFabTestpoint - è un testpoint di fabrication.IsTestpoint - è un testpoint sul lato Top o Bottom.Testpoint - è un testpoint sul lato Top o Bottom?TestpointAssy - è un testpoint di assembly?TestpointAssyBottom - è un testpoint di assembly sul lato Bottom?TestpointAssyTop - è un testpoint di assembly sul lato Top?TestpointBottom - è un testpoint sul lato Bottom?TestpointFab - è un testpoint di fabrication?TestpointFabBottom - è un testpoint di fabrication sul lato Bottom?TestpointFabTop - è un testpoint di fabrication sul lato Top?TestpointTop - è un testpoint sul lato Top?

Crea espressioni logiche per query per individuare e restituire i testpoint nel progetto secondo necessità. Alcuni esempi di espressioni logiche di query che individuano testpoint di fabrication e assembly sono:

(ObjectKind = 'Pad') And (TestpointAssy = 'True')

Individua tutti i pad che sono testpoint di assembly.IsPad And (TestpointAssyTop = 'True')

Individua tutti i pad che sono testpoint di assembly sul lato Top.(ObjectKind = 'Pad') And (TestpointFab = 'True')

Individua tutti i pad che sono testpoint di fabrication.((IsPad Or IsVia)) And (TestpointAssy = 'True')

Individua tutti i pad e le via che sono testpoint di assembly.((IsPad Or IsVia)) And IsFabTestpoint

Individua tutti i pad e le via che sono testpoint di fabrication.

Generazione di report dei testpoint

Altium Designer include generatori di report dedicati per la generazione, rispettivamente, di report dei testpoint di fabrication e di assembly. Questi due generatori di report utilizzano le proprietà di testpoint pertinenti per le primitive pad e via in un progetto.

Un report dei testpoint di fabrication utilizzerà solo le impostazioni di Fabrication testpoint di pad e via. Un report dei testpoint di assembly utilizzerà solo le impostazioni di Assembly testpoint.

I report possono essere generati in due modi:

- Direttamente dall’interno del documento PCB, utilizzando i comandi File » Fabrication Outputs » Test Point Report e File » Assembly Outputs » Test Point Report.

- Utilizzando output opportunamente configurati definiti in un file Output Job Configuration (

*.OutJob).

Includi e configura gli output dei report dei testpoint di fabrication e assembly all’interno di un file Output Job Configuration autonomo e versatile. Una volta definiti, puoi ottenere i report con la semplice pressione di un pulsante!

Includi e configura gli output dei report dei testpoint di fabrication e assembly all’interno di un file Output Job Configuration autonomo e versatile. Una volta definiti, puoi ottenere i report con la semplice pressione di un pulsante!

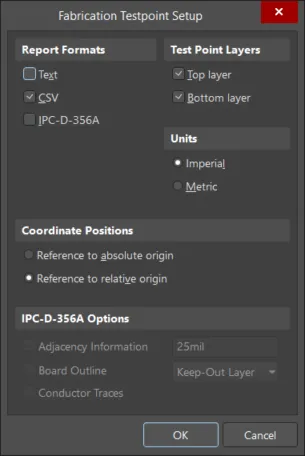

Indipendentemente dal metodo utilizzato per generare un report, le opzioni del report stesso sono definite nella stessa finestra di dialogo. Per un report dei testpoint di fabrication, si utilizza la finestra di dialogo Fabrication Testpoint Setup dialog. Per un report dei testpoint di assembly, si utilizza la finestra di dialogo Assembly Testpoint Setup dialog. Le opzioni del report sono identiche tra queste finestre di dialogo.

Definisci le opzioni del report, incluso il formato del file generato, utilizzando la relativa finestra di configurazione del report.

Le impostazioni definite in una finestra di dialogo Testpoint Setup quando si genera l’output direttamente dal PCB sono distinte e separate da quelle definite per lo stesso tipo di output in un file di configurazione Output Job. Nel primo caso, le impostazioni vengono memorizzate nel file di progetto, mentre nel secondo vengono memorizzate nel file Output Job.

Le opzioni nella sezione Coordinate Positions di una finestra di dialogo consentono di esportare le posizioni dei testpoint in tutti i formati di report rispetto all’origine assoluta della scheda oppure all’origine corrente della scheda.

Tutti i tipi di report dei testpoint supportano gli array di schede incorporati. Quando si esporta da un documento PCB che contiene più array di schede incorporati, vengono prodotti più file netlist IPC-D-356A.

Ruolo del file netlist IPC-D-356A

Uno dei tre formati di output del report dei testpoint è un file netlist IPC-D-356A. Questo file viene generalmente utilizzato per la modalità di collaudo della fabbricazione bare-board. Il file IPC viene post-elaborato in comandi che pilotano un dispositivo di collaudo flying probe.

Indipendentemente da quali caratteristiche siano specificamente identificate come posizioni dei test point in un file IPC-D-356A, le aziende che si occupano della fabbricazione delle schede possono generalmente utilizzare i dati del file per ottenere qualsiasi tipo di collaudo desiderino, anche se, a seconda delle circostanze e del contenuto del file, potrebbe essere necessario un intervento manuale.