제조 규칙 유형

Manufacturing 범주의 설계 규칙은 아래에 설명되어 있습니다.

Manufacturing 범주의 설계 규칙.

최소 환형 링(Minimum Annular Ring)

기본 규칙: 필요하지 않음

이 규칙은 패드 또는 비아에 필요한 최소 환형 링(annular ring)을 지정합니다. 환형 링은 패드/비아 홀의 가장자리에서 패드/비아의 가장자리까지 방사 방향으로 측정됩니다(또한 land perimeter라고도 함).

제약(Constraints)

Minimum Annular Ring 규칙의 기본 제약

Minimum Annular Ring (x-y) - 이 규칙이 대상으로 하는 패드/비아 주변 환형 링의 최소값.

규칙 적용(Rule Application)

온라인 DRC 및 배치 DRC.

참고(Notes)

- 서로 다른 제작 업체는 다양한 제조 기술과 장비를 사용할 것이 분명합니다. 일반적인 성능의 업체는 최소 환형 링 10mil을 허용하는 설계 사양을 제공할 수 있습니다. 고성능 업체는 그 수치를 5mil까지 낮출 수 있습니다. 패드 및 비아 홀이 기계 드릴이 아니라 레이저 드릴로 가공된다면, 최소 환형 링 값은 더 낮아질 수도 있습니다.

- 설계 중인 보드의 등급(class) 또한 최소 환형 링에 필요한 값에 영향을 줍니다. 예를 들어, 고신뢰성 전자 제품을 의미하는 IPC Class 3 표준 설계의 경우 요구되는 최소 환형 링은 2mil입니다.

- 제작 업체의 통상 허용 기준보다 환형 링을 더 줄여야 한다면, 해당 영향을 받는 패드와 비아의 사용을 가능한 한 제한하세요. 이러한 환형 링 사양을 사용하는 패드와 비아가 보드에 많을수록 제작 공정 중 보드가 불량이 될 가능성이 커집니다.

- 환형 링이 전혀 없으면, 예를 들어 패드/비아 배럴에서 나온 솔더가 흘러붙을 구리가 없기 때문에 솔더 접합 품질이 나빠질 수 있습니다.

- 표준은 환형 링의 최소값을 정의하지만, 이 값들은 더 낮출 수도 있습니다. 이러한 값이 해당 수준으로 정의된 이유는 드릴 브레이크아웃(drill breakout)을 방지하기 위함입니다. 이 현상은 환형 링 값이 낮을 때 비교적 흔합니다. 드릴 브레이크아웃은 여러 제조 파라미터(예: 홀 위치, 홀 크기, 필름 팽창)가 서로 불리하게 상호작용하여, 홀이 연결된 구리 트랙을 절단하는 위치로 드릴링되는 결과로 발생합니다.

- 보드 성능을 희생하지 않으면서 제어된 드릴 브레이크아웃을 허용하는 것도 가능합니다. 이를 달성하는 한 가지 방법은 필요한 패드와 비아에 티어드롭(teardrop)을 적용하는 것입니다. 티어드로핑(또는 filleting, 혹은 tapering)은 연결된 트랙과의 접합부에서 패드/비아에 추가 랜드 면적을 부여하는 과정입니다. 이 추가 면적은 브레이크아웃이 발생하더라도 패드-트랙(또는 비아-트랙) 연결을 보호합니다.

-

Minimum Annular Ring 설계 규칙 위반은, 패드/비아 형상이 패드/비아 홀보다 작은 레이어에서 연결을 가진 패드 및 비아에 대해 감지됩니다(예: Properties 패널에서 패드/비아 형상을 수동으로 구성했거나, Remove Unused Pad Shapes 도구를 사용해 제거한 경우).

예각(Acute Angle)

기본 규칙: 필요하지 않음

이 규칙은 동일한 넷(net) 내의 어떤 객체들 사이에서도 허용되는 최소 각도를 지정합니다. Acute Angle 규칙은 넷에만 적용됩니다. 하나의 넷에서 어떤 객체에 의해 생성되는 모든 예각을 찾습니다. 이 규칙은 본질적으로 (같은 레이어에서) 넷에 속한 모든 프리미티브로부터 윤곽(contour)을 만든 다음, 이 윤곽을 분석하여 예각 제한 값보다 작은 각도를 만들 수 있는 지점이 있는지 확인합니다.

제약(Constraints)

Acute Angle 규칙의 기본 제약

- Minimum Angle - 동일한 넷 내 객체들 사이에서 생성되는 최소 허용 각도를 지정합니다.

- Check Tracks Only - 이 옵션을 활성화하면 DRC가 트랙 객체에 대해서만 예각을 검사하도록 강제합니다.

규칙 적용(Rule Application)

온라인 DRC 및 배치 DRC.

홀 크기(Hole Size)

기본 규칙: 필요함

이 규칙은 설계 내 패드와 비아의 최대/최소 홀 크기를 지정합니다. 홀 크기는 제작 시 패드/비아를 관통해 드릴링되는 홀의 직경입니다.

제약(Constraints)

Hole Size 규칙의 기본 제약

-

Measurement Method - 최소/최대 홀 크기를 정의하는 데 사용되는 방법을 지정합니다:

- Absolute - 최소/최대 홀 크기 값은 절대값으로 지정됩니다.

- Percent - 최소/최대 홀 크기는 패드/비아 크기에 대한 백분율로 표현됩니다.

- Minimum - 설계 내 패드 및 비아에 대한 최소 홀 크기 값입니다. 선택한 측정 방법에 따라 값은 절대값(기본값 = 1mil) 또는 패드/비아 크기에 대한 백분율(기본값 = 20%)로 표시됩니다.

- Maximum - 설계 내 패드 및 비아에 대한 최대 홀 크기 값입니다. 선택한 측정 방법에 따라 값은 절대값(기본값 = 100mil) 또는 패드/비아 크기에 대한 백분율(기본값 = 80%)로 표시됩니다.

규칙 적용(Rule Application)

온라인 DRC 및 배치 DRC.

레이어 페어(Layer Pairs)

기본 규칙: 필요함

이 규칙은 사용된 비아 타입이 현재 정의된 비아 타입과 일치하는지 확인합니다. 사용된 비아 타입은 보드에서 발견된 비아와 패드로부터 결정됩니다. 허용되는 비아 타입은 Layer Stack Manager의 Via Types 탭에서 정의됩니다.

제약(Constraints)

Layer Pairs 규칙의 기본 제약

Enforce layer pairs settings – 검사를 수행할지 여부를 지정합니다.

규칙 적용(Rule Application)

온라인 DRC, 배치 DRC, 그리고 대화형 라우팅 중.

홀-홀 간격(Hole To Hole Clearance)

기본 규칙: 필요함

이 규칙은 드릴 홀의 제조 호환성을 검사하도록 보장합니다. 활성화하면 동일 위치에 여러 비아/패드가 있거나, 패드/비아 홀이 서로 겹치는 경우를 표시합니다. 또한 적층 마이크로비아(stacked micro vias)를 허용할지 여부를 결정하는 옵션도 있습니다.

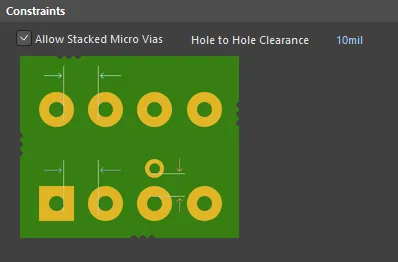

제약(Constraints)

Hole To Hole Clearance 규칙의 기본 제약

-

Allow Stacked Micro Vias - 이 옵션을 활성화하면 마이크로비아를 적층할 수 있습니다.

- Hole To Hole Clearance - 설계에서 패드/비아 홀 사이에 허용되는 최소 간격 값.

규칙 적용(Rule Application)

온라인 DRC 및 배치 DRC.

최소 솔더 마스크 슬리버(Minimum Solder Mask Sliver)

기본 규칙: 필요함

이 규칙은 이후 단계에서 제조 문제를 일으킬 수 있는 솔더 마스크의 좁은 구간을 식별하는 데 도움이 됩니다. 보드 전반에 걸쳐 솔더 마스크의 최소 폭이 확보되도록, 이 규칙은 어떤 두 솔더 마스크 오프닝 사이의 거리가 사용자가 지정한 최소값 이상인지(같거나 더 큰지) 확인합니다. 여기에는 패드, 비아, 그리고 솔더 마스크 레이어에 존재하는 모든 프리미티브가 포함됩니다. 또한 Top과 Bottom 면을 독립적으로 검사합니다.

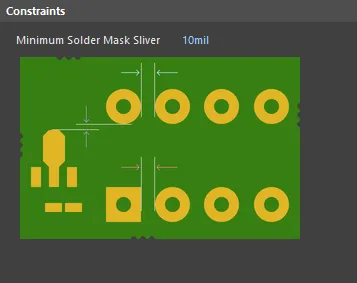

제약(Constraints)

Minimum Solder Mask Sliver 규칙의 기본 제약

Minimum Solder Mask Sliver - 허용되는 솔더 마스크의 최소 폭을 지정합니다.

규칙 적용(Rule Application)

온라인 DRC 및 배치 DRC.

실크-솔더 마스크 간격(Silk To Solder Mask Clearance)

기본 규칙: 필요함

이 규칙은 모든 실크스크린 프리미티브와 모든 솔더 마스크 프리미티브, 또는 (솔더 마스크 오프닝을 통해 노출된) 노출 구리 레이어 프리미티브 사이의 간격을 검사합니다. 이 검사는 그 거리가 제약에서 지정한 값 이상인지(같거나 더 큰지) 보장합니다.

많은 제조업체는 실크스크린을 구리 패드에 맞춰서가 아니라 마스크 오프닝에 맞춰 일상적으로 제거(또는 ‘클리핑’)합니다. 하지만 그렇게 하면 실크스크린 텍스트가 읽기 어려워질 수 있습니다. DRC를 통해 이러한 경우를 잡아낼 수 있으면, 제조로 보드를 보내기 전에 문제가 되는 실크스크린 텍스트를 조정할 수 있습니다.

제약(Constraints)

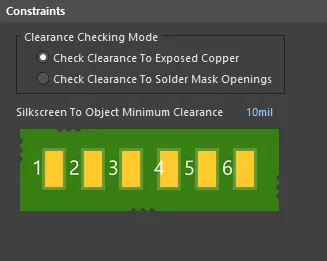

Silk To Solder Mask Clearance 규칙의 기본 제약

-

Clearance Checking Mode - 간격 검사 모드를 선택합니다:

- Check Clearance To Exposed Copper - 이 모드에서는 실크스크린(Top/Bottom Overlay 레이어) 객체와, 솔더 마스크 오프닝을 통해 노출된 부품 패드의 구리 사이에서 간격을 검사합니다.

- Check Clearance To Solder Mask Openings- 이 모드에서는 실크스크린(Top/Bottom Overlay 레이어) 객체와, 패드/비아 또는 Solder Mask Expansion 옵션이 활성화된 솔더 마스크 포함 구리 객체처럼 솔더 마스크를 포함하는 객체에 의해 생성된 솔더 마스크 오프닝 간의 클리어런스를 검사합니다.

- Silkscreen To Object Minimum Clearance - 선택한 클리어런스 검사 모드에 따라, 실크스크린 객체와 노출된 구리 또는 솔더 마스크 오프닝 사이의 최소 허용 클리어런스를 지정합니다.

규칙 적용

온라인 DRC 및 배치 DRC.

Silk To Silk Clearance

기본 규칙: 필요

이 규칙은 실크스크린 레이어에서 텍스트와 다른 객체 사이에 허용되는 최소 클리어런스를 정의합니다.

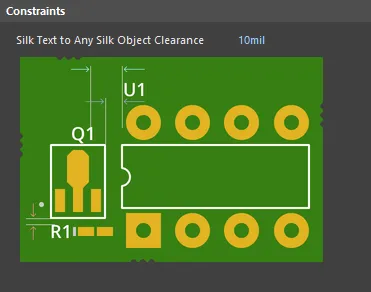

제약조건

Silk To Silk Clearance 규칙의 기본 제약조건

Silk Text to Any Silk Object Clearance - 임의의 두 실크스크린 객체 사이의 최소 허용 클리어런스를 지정합니다.

규칙 적용

온라인 DRC 및 배치 DRC.

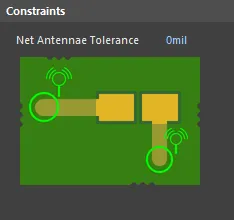

Net Antennae

기본 규칙: 필요

이 규칙은 설계의 넷(net) 레벨에서 동작하여, 끝이 열린 트랙/아크 프리미티브 또는 비아로 종단되어 결과적으로 안테나를 형성하는 끝이 열린 트랙/아크를 플래그 처리합니다.

제약조건

Net Antennae 규칙의 기본 제약조건

Net Antennae Tolerance - 끝이 열린 트랙/아크 프리미티브(또는 비아로 종단되는 것)의 스텁(stub)에 대해 허용되는 최대 길이.

규칙 적용

온라인 DRC 및 배치 DRC.

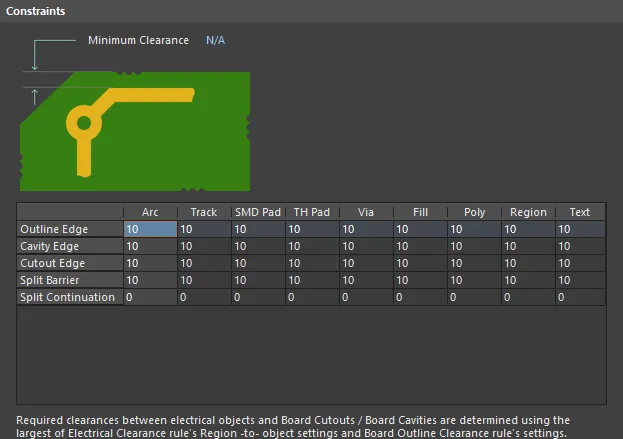

Board Outline Clearance

기본 규칙: 필요하지 않음

이 규칙은 제작되는 설계 객체에서 보드의 에지까지 허용되는 최소 클리어런스를 정의합니다. 모든 객체-에지 조합에 대해 단일 클리어런스 값을 지정할 수도 있고, 전용 Minimum Clearance Matrix를 사용하여 서로 다른 페어링에 대해 서로 다른 클리어런스를 정의할 수도 있습니다. Board Outline과 Board Edge는 보드의 외곽 에지를 설명하기 위해 서로 바꿔 사용되는 일반 명칭입니다. edge 용어는 이미지 아래 표에 정의되어 있습니다. Board Outline Clearance 설계 규칙은 전기 레이어와 오버레이(실크스크린) 레이어에서 객체-에지 클리어런스를 검사합니다.

제약조건

Board Outline Clearance 규칙의 기본 제약조건

| Edge Type | 정의 |

|---|---|

| Outline Edge | 보드의 가장 바깥(외곽) 에지 |

| Cavity Edge | 사용자 정의 캐비티의 에지 |

| Cutout Edge | 사용자 정의 컷아웃의 에지 |

| Split Barrier | Split Line이 이 레이어에서 보드의 에지를 정의할 때, 이 에지는 Split Line Barrier라고 합니다 |

| Split Continuation | 이 레이어가 Split Line을 넘어 계속될 때, 이 에지는 Split Line Continuation(투과 가능한 경계)이라고 합니다. 특정 객체 종류가 Split Continuation을 가로지를 수 있도록 하려면 클리어런스 값을 0으로 설정하십시오. 0은 해당 객체 종류에 대해 이것이 연속 레이어이며 객체가 스플릿 라인을 위반(통과)할 수 있음을 의미합니다. 이 기법을 사용하면 예를 들어 라우팅된 트랙이 한 Layer Stack Region에서 다른 영역으로 이동할 수 있습니다. |

- Minimum Clearance - 필요한 최소 클리어런스 값입니다. 여기에 입력한 값은 Minimum Clearance Matrix의 모든 셀에 복제됩니다. 반대로, 매트릭스에서 하나 이상의 객체 페어링에 대해 다른 클리어런스 값을 입력하면, 보드 전체에 단일 클리어런스 값이 적용되지 않음을 반영하기 위해 Minimum Clearance 제약조건이 N/A로 변경됩니다.

- Minimum Clearance Matrix - 설계에서 다양한 객체-에지 클리어런스 조합 간의 클리어런스를 미세 조정할 수 있는 기능을 제공합니다.

클리어런스 매트릭스 작업

매트릭스에서 클리어런스 값을 정의하는 방법은 다음과 같습니다:

- 단일 셀 편집 - 특정 객체 페어링에 대한 최소 클리어런스를 변경합니다.

-

다중 셀 편집 - 여러 객체 페어링에 대한 최소 클리어런스를 변경합니다:

- 열에서 여러 셀을 선택하려면 Ctrl+Click, Shift+Click, Click+Drag을 사용합니다.

- 행에서 여러 개의 연속된 셀을 선택하려면 Shift+Click, Click+Drag을 사용합니다.

- 여러 행과 열에 걸쳐 여러 개의 연속된 셀을 선택하려면 Click+Drag를 사용합니다

- 행 헤더를 클릭하면 해당 행의 모든 셀을 빠르게 선택할 수 있습니다.

- 열 헤더를 클릭하면 해당 열의 모든 셀을 빠르게 선택할 수 있습니다.

필요한 선택(단일 셀 또는 다중 셀)을 완료한 후 현재 값을 변경하는 것은 필요한 새 값을 입력하기만 하면 됩니다. 새로 입력한 값을 적용하려면 다른 셀을 클릭해 포커스를 이동하거나 Enter를 누르십시오. 선택된 모든 셀이 새 값으로 업데이트됩니다.

규칙 적용

온라인 DRC, 배치 DRC, 대화형 라우팅 및 자동 라우팅.

AI로 번역됨

AI로 번역됨