Electrical Rule Types

Altium Essentials: PCB Design Rules Creation

This content is part of the official Altium Professional Training Program. For full courses, materials and certification, visit Altium Training.

Правила проектирования категории Electrical описаны ниже.

Категория правил проектирования Electrical.

Зазор

Правило по умолчанию: обязательно

Это правило определяет минимально допустимый зазор между любыми двумя примитивными объектами на медном слое. Можно задать либо одно значение зазора, либо разные зазоры для разных пар объектов с помощью специального Minimum Clearance Matrix. Последний вариант в сочетании с областью действия правила обеспечивает гибкость, позволяя создать компактный и целенаправленный набор правил зазоров, отвечающий даже самым строгим требованиям.

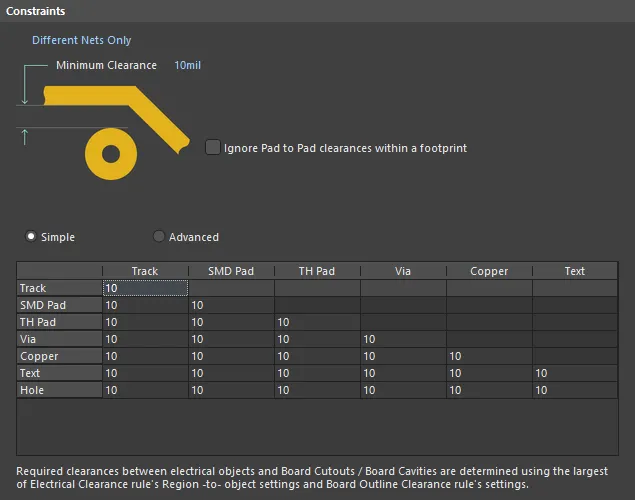

Ограничения

Область действия правила возвращает набор объектов, к которому затем применяются описанные ниже ограничения:

-

Connective Checking - набор объектов цепей, возвращаемый областью действия правила, затем может быть дополнительно сужен следующими способами:

-

Different Nets Only- ограничение применяется между любыми двумя примитивными объектами, принадлежащими разным цепям (например, двумя дорожками на двух разных цепях). -

Same Net Only- ограничение применяется между любыми двумя примитивными объектами, принадлежащими одной и той же цепи (например, между переходным отверстием и контактной площадкой на одной цепи или двумя сегментами дорожки в одной цепи). -

Any Net- ограничение применяется между любыми двумя примитивными объектами, принадлежащими любой цепи в проекте. Это наиболее полный из трех вариантов, охватывающий случаи, когда объекты принадлежат одной и той же или разным цепям. - Different Differential Pair - ограничение применяется между любыми двумя примитивными объектами, принадлежащими разным цепям разных дифференциальных пар (например, дорожка в DiffPair1 и дорожка в DiffPair2). Правило не применяется между примитивами двух цепей в одной и той же дифференциальной паре (например, DiffPair1_P и DiffPair1_N). Используйте это ограничение для настройки зазора между дифференциальными парами.

-

Same Differential Pair - ограничение применяется между любыми двумя примитивными объектами, принадлежащими разным цепям одной и той же дифференциальной пары (например, дорожка в TX_P и дорожка в TX_N). Используйте это ограничение для настройки зазора, когда цепи в дифференциальной паре должны располагаться ближе друг к другу, чем допускается общим зазором.

Подробнее о проверке зазоров дифференциальных пар

-

- Ignore Pad to Pad Clearances within a footprint - включите/выключите этот параметр, чтобы указать, следует ли игнорировать зазоры между площадками в пределах одного и того же посадочного места компонента. По умолчанию этот параметр отключен.

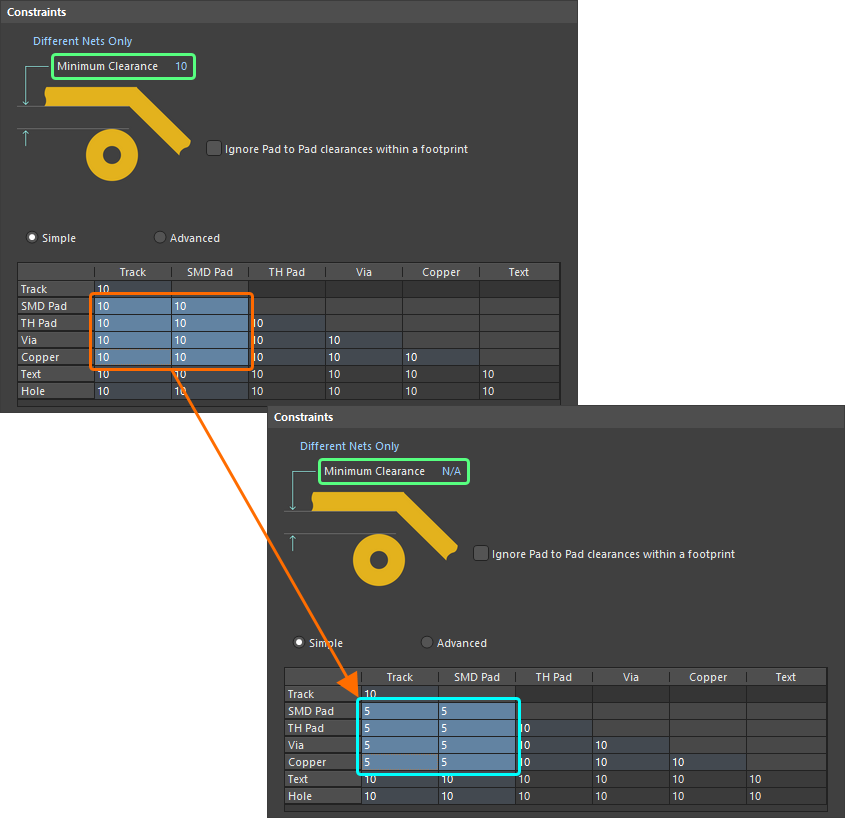

- Minimum Clearance - значение требуемого минимального зазора. Введенное здесь значение будет продублировано во всех ячейках матрицы Minimum Clearance. И наоборот, если для одной или нескольких пар объектов в матрице введено другое значение зазора, ограничение Minimum Clearance изменится на N/A, что будет отражать тот факт, что единое значение зазора не применяется ко всей плате.

- Minimum Clearance Matrix - позволяет точно настраивать зазоры между различными комбинациями объектов в проекте.

Работа с матрицей зазоров

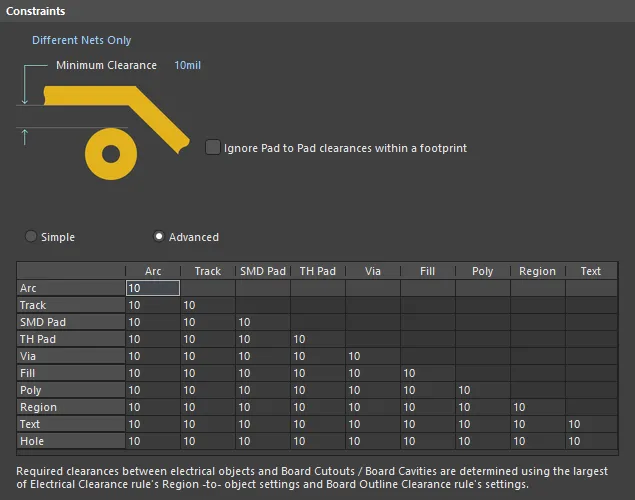

Для многих пользователей между примитивами Track и Arc нет большой разницы. А когда речь идет об объектах Fill, Region и Polygon, большинство пользователей воспринимают их просто как еще одну «медь». С учетом этого матрица минимальных зазоров для правила Clearance была улучшена и теперь может работать в двух режимах:

- Simple - в этом режиме объекты Track и Arc (включая объекты Track Keepout и Arc Keepout) объединяются в одну запись Track. Объекты Fill, Poly и Region (включая объекты Fill Keepout и Region Keepout) объединяются в одну запись Copper. Режим Simple является режимом по умолчанию независимо от того, открывается ли существующий проект или новый.

- Advanced - этот режим представляет собой традиционную матрицу, в которой показаны все объекты.

Значения зазоров в матрице можно задавать следующими способами:

- Редактирование одной ячейки - для изменения минимального зазора для конкретной пары объектов. Щелкните по ячейке, чтобы выбрать ее для редактирования.

-

Редактирование нескольких ячеек - для изменения минимального зазора для нескольких пар объектов:

- Используйте Ctrl+Click, Shift+Click и Click+Drag, чтобы выбрать несколько ячеек в столбце.

- Используйте Shift+Click и Click+Drag, чтобы выбрать несколько смежных ячеек в строке.

- Используйте Click+Drag, чтобы выбрать несколько смежных ячеек в нескольких строках и столбцах.

- Щелкните по заголовку строки, чтобы быстро выбрать все ячейки в этой строке.

- Щелкните по заголовку столбца, чтобы быстро выбрать все ячейки в этом столбце.

После выполнения нужного выбора (одной ячейки или нескольких ячеек) изменение текущего значения сводится к вводу нового требуемого значения. Чтобы подтвердить вновь введенное значение, либо щелкните в другой ячейке, либо нажмите Enter. Все ячейки в выделении будут обновлены новым значением.

Пример редактирования нескольких ячеек. Обратите внимание, что поскольку теперь для одной или нескольких пар объектов существуют разные значения зазора, ограничение Minimum Clearance изменилось на N/A, что отражает тот факт, что единое значение зазора больше не применяется ко всем комбинациям зазоров между объектами.

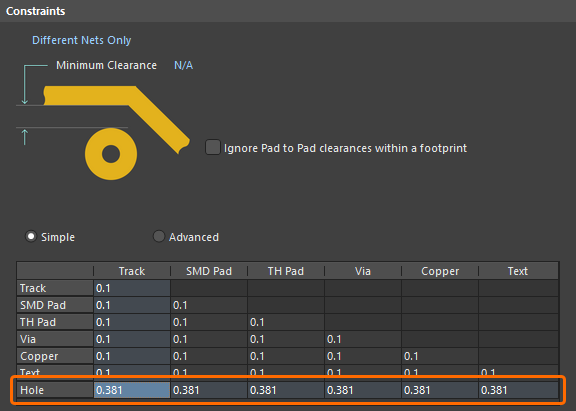

Проверка зазора от отверстия до объекта

Проектировщики могут проверять зазоры между краями просверленных отверстий и соседними медными объектами на сигнальных слоях. Это особенно полезно для предотвращения прокладки дорожки слишком близко к просверленному отверстию, где в противном случае могли бы сказаться возможные отклонения сверла в процессе изготовления платы. Строка в нижней части матрицы минимальных зазоров правила Clearance используется для задания требуемых зазоров.

Установите значения зазора, чтобы выявлять любые медные объекты, расположенные слишком близко к краям просверленных отверстий в проекте.

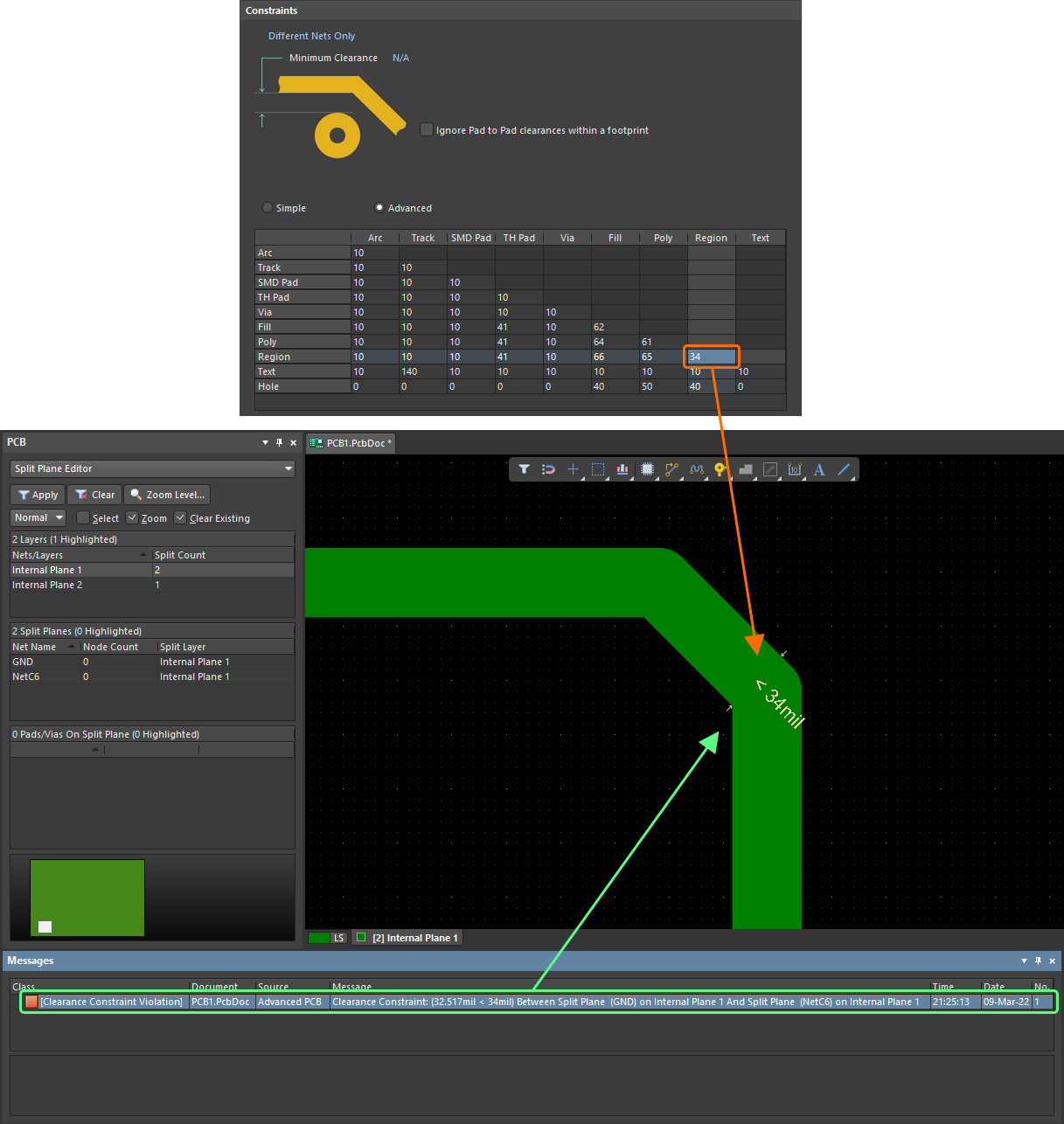

Проверка зазоров для split plane

Проектировщики также могут проверять зазоры между областями split plane на внутренних plane-слоях. Способ задания зазора зависит от режима, в котором используется матрица минимальных зазоров:

- Simple mode - укажите требуемое значение зазора split plane-to-split plane с помощью ячейки Copper-Copper.

- Advanced mode - укажите требуемое значение зазора split plane-to-split plane с помощью ячейки Region-Region.

Нарушение будет отображаться в виде:

Clearance Constraint: (<CurrentClearance> < <DefinedClearance>) Between Split Plane (<NetName>) on <InternalPlaneLayerName> And Split Plane (<NetName>) on <InternalPlaneLayerName>,

например:

Clearance Constraint: (32.36mil < 34mil) Between Split Plane (GND) on Internal Plane 1 And Split Plane (NetC6) on Internal Plane 1

Проверка зазоров между областями split plane на внутреннем слое. В этом случае значение зазора 34mil было введено в ячейку Region-Region, поскольку зазоры задаются с использованием режима Advanced матрицы.

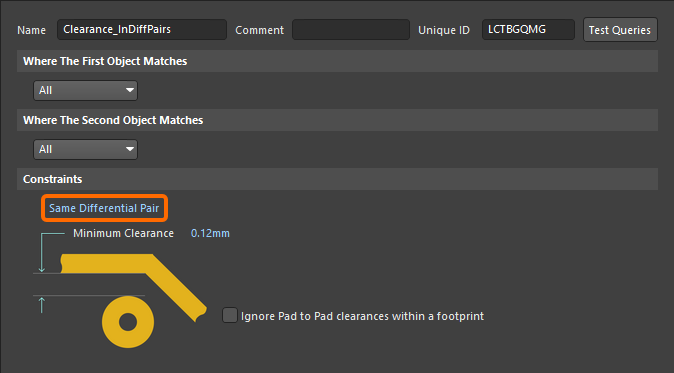

Проверка зазоров для дифференциальных пар

Дифференциальные пары создают особые сложности при проектировании и часто требуют задания как зазора within-pair, так и зазора pair-to-pair, а также, возможно, третьего правила для управления зазором pair-to-all other nets. Для поддержки этого в области Constraints предусмотрен раскрывающийся список, где можно выбрать параметры Same Differential Pair и Different Differential Pair.

Например, если цепи внутри дифференциальных пар требуют меньшего зазора, чем общий зазор платы, этого можно добиться с помощью параметра ограничения Same Differential Pair, как показано ниже. Обратите внимание, что хотя область действия правила применяется к объектам цепей All в проекте, настройка Constraint ограничивает его применение только объектами в Same Differential Pair.

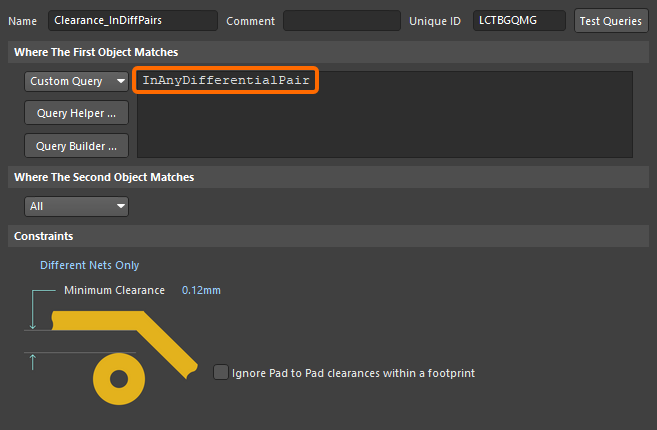

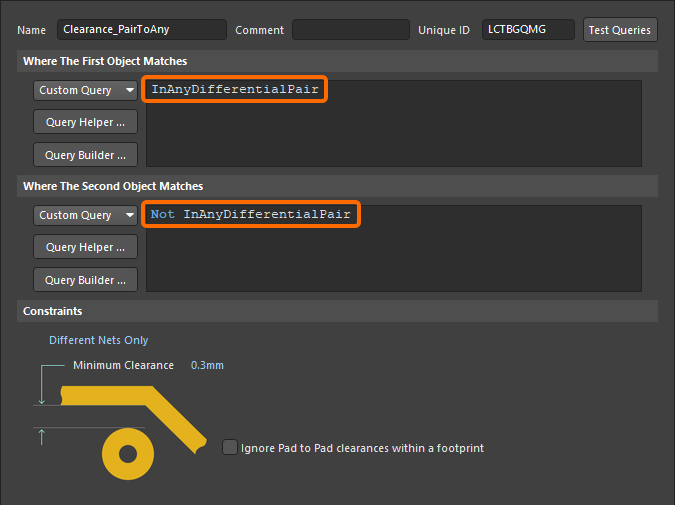

Того же результата можно добиться, если ограничить область действия правила только объектами дифференциальных пар (например, InAnyDifferentialPair), как показано ниже. Обратите внимание, что это правило также будет применяться между цепью в дифференциальной паре и любым другим объектом цепи в проекте, поэтому такой подход следует использовать только в том случае, если у вас есть другие правила с более высоким приоритетом, определяющие требования DiffPairNet-to-DiffPairNet и/или DiffPairNet-to-Any. Если используется этот подход, приоритет правил для дифференциальных пар также должен быть настроен правильно: правило с более жестким требованием по зазору должно иметь более высокий приоритет.

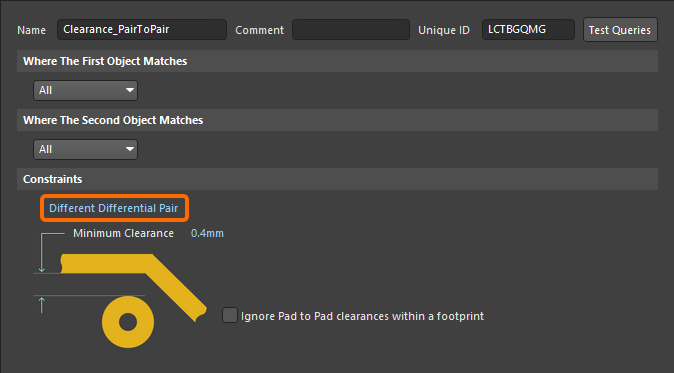

Аналогичный подход можно использовать для управления зазором between дифференциальных пар. На изображении ниже показано, как для этого можно использовать ограничение Different Differential Pair.

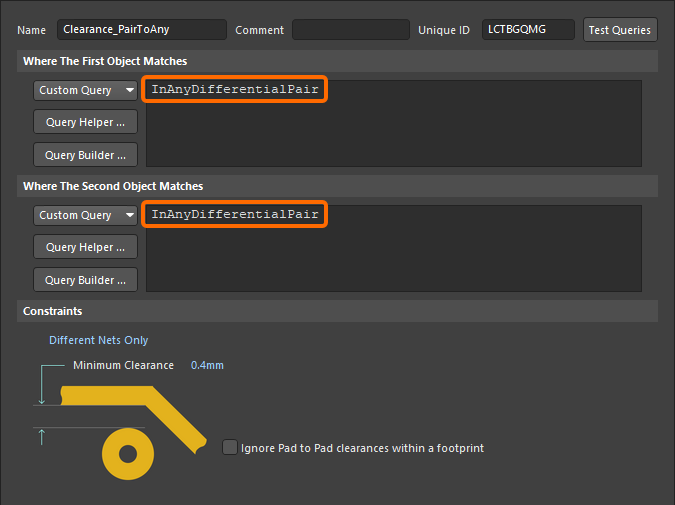

Как и в предыдущем примере, этого также можно добиться с помощью области действия правила вместо ограничения Different Differential Pairs. Помните, что приоритеты правил должны быть настроены так, чтобы правило с более жестким требованием по зазору имело более высокий приоритет.

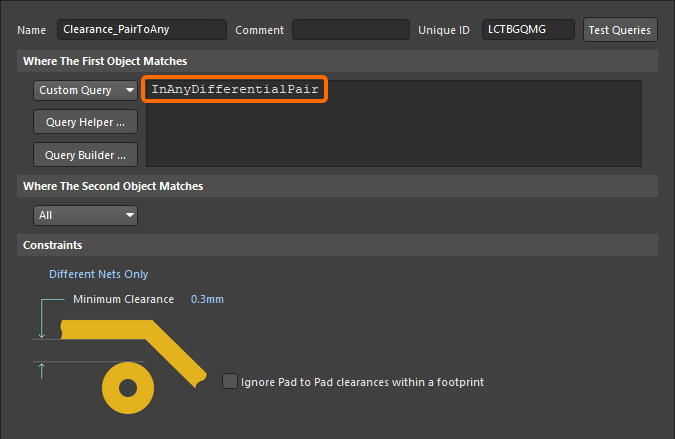

Чтобы задать другой зазор от цепи дифференциальной пары до любого другого объекта цепи, можно использовать следующее правило.

Это можно дополнительно уточнить так, чтобы оно применялось только между объектами дифференциальных пар и объектами, не относящимися к дифференциальным парам, как показано ниже.

Подробнее о трассировке дифференциальных пар. Подробнее об ограничении области действия правил проектирования для дифференциальных пар.

Применение правила

Online DRC, Batch DRC, интерактивная трассировка #, автотрассировка # и размещение polygon.

Примечания

- # Хотя DRC может проверять зазор между любыми типами объектов с использованием любого способа ограничения области действия правила, механизмы трассировки не поддерживают такой уровень детализации. Например, базовое правило зазора может требовать, чтобы все дорожки имели зазор 1 мм, а правило с более высоким приоритетом — чтобы дорожки длиной более 10 мм имели зазор 2 мм. В этой ситуации механизм интерактивной трассировки будет соблюдать базовое правило зазора, игнорируя правило с более высоким приоритетом для дорожек длиной более 10 мм. Другой пример — трассировка с дугами в углах. Если правило зазора задает больший зазор для дуг, чем для дорожек, и вы выполняете интерактивную трассировку с дугами в углах, механизм интерактивной трассировки проигнорирует настройку для дуг и будет следовать настройке для дорожек, размещая угловые дуги с тем же зазором, что и сегменты дорожек. В обоих этих примерах, как только трассировка будет завершена, Online DRC отметит такие ситуации как нарушения.

-

При задании ограничений для правила параметр Connective Checking обычно устанавливается в

Different Nets Only. Примером, когда можно использоватьSame Net OnlyилиAny Net, является проверка того, что via расположены слишком близко к pad или другим via в той же цепи либо в любой другой цепи. - Матрица минимальных зазоров применяется независимо от указанного метода проверки связности. Если между объектами одной и той же цепи требуются зазоры, отличающиеся от зазоров, заданных для объектов разных цепей, обязательно определите отдельные правила зазоров в соответствии с требованиями.

- Применимость матрицы зазоров зависит от области действия правила. Например, при области действия ALL-ALL применимы все ячейки матрицы (то есть все возможные пары объектов). Однако если область действия установлена в IsVia-IsTrack, тогда применима только одна ячейка для пары объектов Via-Track, а все остальные ячейки матрицы не используются.

-

При определении правила зазора для polygon правило фактически применяется к примитивам polygon, а не к самому polygon. В этом случае в Full Query следует использовать ключевое слово

InPolygon(илиInPoly) вместоIsPolygon(илиIsPoly). Если специальное правило зазора для polygon должно оказывать влияние, ему также необходимо назначить более высокий приоритет, чем любому общему правилу зазора. - Во время трассировки (и аналогичных операций) механизм правил постоянно проверяет наличие препятствий вокруг точки редактирования. Сканируемая область включает область примитива плюс область зазора, требуемую вокруг этого примитива. Это означает, что чем больше зазор, заданный в правилах, тем большую область нужно сканировать и тем медленнее будет выполняться операция. Если большой зазор нужен только для небольшого числа объектов, можно избежать замедления механизма трассировки, добавив keepout вокруг этих конкретных объектов вместо задания для них правила большого зазора.

- При использовании Dielectric Shapes Generator (в Printed Electronics) в режиме Auto форма диэлектрика автоматически расширяется, чтобы удовлетворить требованиям применимого правила проектирования Clearance Constraint.

- В Printed Electronics зазоры net-to-net проверяются на всех слоях, а не только на одном и том же слое.

Короткое замыкание

Правило по умолчанию: требуется

Это правило проверяет наличие коротких замыканий между примитивными объектами на медных (сигнальных и полигональных) слоях. Короткое замыкание существует, когда два объекта с разными именами цепей соприкасаются.

Ограничения

Ограничения по умолчанию для правила Short-Circuit

Allow Short Circuit — определяет, могут ли целевые цепи, попадающие под две области действия (полные запросы) правила, быть замкнуты между собой или нет. Если требуется замкнуть две разные цепи, например при соединении двух систем заземления в проекте, убедитесь, что этот параметр включен.

Применение правила

Online DRC, Batch DRC и во время автотрассировки.

Примечания

-

В Printed Electronics design когда разные цепи пересекаются на разных слоях, это отмечается как короткое замыкание. Такие пересечения изолируются размещением диэлектрической заплаты на непроводящем слое.

-

Это правило также применяется к Wire Bonding. Нарушение возникает, когда проволочная перемычка соединена с контактной площадкой кристалла или медным объектом другой цепи либо когда соединены конечные точки проволочных перемычек разных цепей.

Неразведенная цепь

Правило по умолчанию: требуется

Это правило проверяет статус завершенности каждой цепи, попадающей в область действия (полный запрос) правила. Если цепь не завершена, то каждый завершенный участок (подцепь) перечисляется вместе с процентом завершенности трассировки. Завершенность трассировки определяется следующим образом:

(connections complete / total number of connections) x 100

Система проверки правил проектирования в PCB Editor обычно считает цепь разведенной, если все узлы в этой цепи (контактные площадки компонентов) соединены с помощью объектов проектирования, учитывающих цепи (проводники, дуги, контактные площадки, переходные отверстия и полигоны). Эти объекты считаются соединенными, если они соприкасаются друг с другом. Однако, хотя простое соприкосновение воспринимается программой как соединение, при изготовлении платы хрупкость некоторых таких «соединений» может вызвать критические проблемы, особенно когда объекты — например, два смежных сегмента проводника или проводник, входящий в контактную площадку/переходное отверстие, — соприкасаются лишь незначительно. Такие соединения часто называют «плохими соединениями», «некачественными соединениями» или «неполными соединениями». Это правило также можно настроить для проверки таких некачественных соединений.

Ограничения

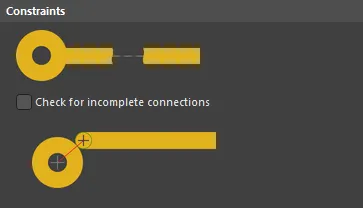

Ограничения по умолчанию для правила Un-Routed Net

Check for incomplete connections — при включении этого параметра выполняются следующие дополнительные проверки связности между применимыми объектами проекта:

- Track/Arc to Track/Arc - проверка того, что осевые линии или центры концов соединяемых сегментов проводников/дуг совпадают.

- Track/Arc to Via - проверка того, что осевая линия или центр конца сегмента проводника/дуги размещены на форме переходного отверстия.

- Track/Arc to Pad - проверка того, что осевая линия или центр конца сегмента проводника/дуги размещены на форме контактной площадки.

- Via to Pad - проверка того, что центр переходного отверстия размещен на форме контактной площадки.

- Via to Via - проверка того, что центр одного переходного отверстия размещен на форме другого переходного отверстия.

- Polygon to Track/Arc - проверка того, что осевая линия или центр конца сегмента проводника/дуги перекрываются полигоном.

- Polygon to Pad/Via - проверка того, что центр Pad/Via перекрывается полигоном, когда Pad/Via использует прямое соединение с полигоном.

Применение правила

Batch DRC.

Примечания

-

Некачественное соединение будет отмечено в рабочем пространстве проекта с помощью подробного маркера нарушения,

, а соответствующее сообщение появится на панели Messages.

, а соответствующее сообщение появится на панели Messages.

-

Где применимо, между несоединенными объектами в цепи будет проведена линия соединения, а данные о длине неразведенной цепи будут отражены в PCB panel (в режиме Nets mode).

-

Для работы некоторых проверок DRC правило Un-Routed Net должно быть включено для Batch.

-

В Printed Electronics переходы между слоями not требуют переходного отверстия, анализатор цепей распознает, что цепь не разорвана, если переходное отверстие удалено из разведенной цепи. Плата определяется как Printed Electronics, когда в Layer Stack Manager включен параметр Printed Electronics. Подробнее см. в Printed Electronics.

-

Это правило также применяется к Wire Bonding. Нарушение возникает, когда отсутствует соединение между контактными площадками кристалла, проволочными перемычками и/или медными объектами одной и той же цепи.

Неподключенный вывод

Правило по умолчанию: не требуется

Это правило обнаруживает выводы, которым не назначена цепь и к которым не подведены проводники.

Ограничения

Нет

Применение правила

Online DRC и Batch DRC.

Измененный полигон

Правило по умолчанию: требуется

Это правило обнаруживает полигоны, которые все еще скрыты и/или были изменены, но еще не были перезалиты.

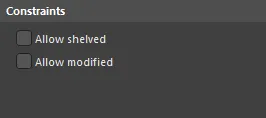

Ограничения

Ограничения по умолчанию для правила Modified Polygon

- Allow shelved — если включено, все полигоны, попадающие в область действия этого правила проектирования и в настоящее время скрытые, не будут отмечаться как нарушение.

- Allow modified - если включено, все полигоны, попадающие в область действия этого правила проектирования и в настоящее время измененные, но еще не перезалитые, не будут отмечаться как нарушение.

Применение правила

Online DRC и Batch DRC.

Длина пути утечки

Правило по умолчанию: не требуется

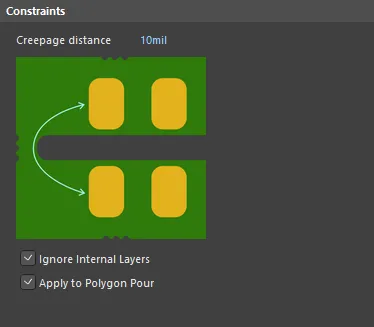

Это правило проверяет расстояние утечки между целевыми сигналами по поверхности платы через неметаллизированные отверстия, вырезы и по краю платы.

Ограничения

Ограничения по умолчанию для правила расстояния утечки

- Creepage distance – нарушение правила фиксируется, когда любая точка первого объекта находится на расстоянии, равном или меньшем, чем заданное расстояние до любой точки второго объекта.

- Ignore Internal Layers – используйте этот параметр, чтобы правило применялось только к внешним слоям.

- Apply to Polygon Pour – используйте этот параметр, чтобы применять правило к полигонам в области действия.

Применение правила

Online DRC, Batch DRC и во время автотрассировки.

Примечания

-

Правило Creepage Distance по умолчанию не включено для Online или Batch проверки правил проектирования. Включите Online/Batch-проверку в диалоговом окне Design Rule Checker (Tools » Design Rule Check, категория Electrical).

-

Также может потребоваться настроить отображение нарушений правил: Violation Details (локализованная информация о нарушении) и/или Violation Overlay (подсветка всех объектов, участвующих в нарушении) включаются на странице PCB Editor - DRC Violation Display диалогового окна Preferences.

-

Правило определяет ближайшие точки на целевых цепях и проверяет расстояние между ними в плоскостях X, Y и Z.

-

Если паз на плате был создан размещением контактной площадки, убедитесь, что параметр Plated отключен в свойствах площадки, так как программное обеспечение считает металлизированную стенку проводящей и соответственно уменьшает расстояние утечки.

-

Если заливка полигона и другие объекты попадают в область действия правила проектирования Creepage Distance с включенным параметром Apply to Polygon Pour и правила проектирования Clearance, учитываются оба правила, и при заливке полигона применяется большее значение. Например, если правило Creepage Distance имеет большее значение ограничения, чем правило Clearance, будет применено именно это большее значение.

Z-Axis Clearance

Правило по умолчанию: не требуется

Это правило проверяет минимальные зазоры между различными примитивами на разных медных слоях.

Ограничения

Ограничения по умолчанию для правила расстояния Z-Axis Clearance

Z-Axis Clearance – нарушение правила фиксируется, когда любая точка первого объекта находится на расстоянии, равном или меньшем, чем заданное расстояние до любой точки второго объекта, если первый и второй объекты размещены на разных медных слоях.

Применение правила

Online DRC, Batch DRC.

Примечания

-

Если для правила включено отображение Violation Details (страница PCB Editor – DRC Violations Display диалогового окна Preferences), текст нарушения в рабочем пространстве PCB отображается в формате:

< [RuleValue] ([Actual Z-Axis Clearance Value]; XY: [Z-Axis Clearance Projected on XY]),где

[RuleValue]— это ограничение, заданное в правиле, а[Actual Z-Axis Clearance Value]— кратчайшее расстояние по диагонали между краями примитивов на разных слоях.В других местах программного обеспечения используется следующий формат:

Z-Axis Clearance: ([Actual Z-Axis Clearance Value] < [RuleValue]) Between [Object1Description] And [Object2Description] -

Правило поддерживается полигональными заливками (сплошными и штрихованными) и внутренними плоскостями. Обратите внимание, что вырезы в полигонах создаются только при обнаружении нарушения между полигоном и объектами других типов (трассами, площадками и т. д.). Хотя зазоры и нарушения обнаруживаются между полигональными заливками на разных сигнальных слоях, вырезы в этом случае автоматически не создаются.

-

Также обратите внимание, что хотя зазоры и нарушения обнаруживаются между объектами (размещенными на сигнальных слоях) и внутренними плоскостями (по кратчайшему расстоянию), такие нарушения необходимо устранять вручную.

-

При открытии PCB, содержащей заданные правила/ограничения Z-Axis Clearance, в более старой версии Altium Designer, которая не поддерживает эту функцию, правила будут потеряны.

Локализовано с помощью ИИ

Локализовано с помощью ИИ