Routing Rule Types

Правила проектирования категории Routing описаны ниже.

Категория правил проектирования Routing

Ширина

Правило по умолчанию: требуется

Это правило задаёт ширину дорожек, размещаемых на медных (сигнальных) слоях.

Ограничения

Ограничения для правила Width, которые применяются ко всем слоям. Значения для конкретных слоёв задавайте в таблице (сетке) (наведите курсор, чтобы отобразить).

-

Preferred Width — задаёт предпочтительную ширину, используемую для дорожек при трассировке платы.

-

Min Width — задаёт минимально допустимую ширину дорожек при трассировке платы.

-

Max Width — задаёт максимально допустимую ширину дорожек при трассировке платы.

-

Check Tracks/Arcs Min/Max Width Individually – для каждого маршрута в цепи, на которую нацелено правило, проверьте, что ширина каждой отдельной дорожки и дуги находится в пределах минимального и максимального диапазона

-

Check Min/Max Width for Physically Connected – для каждого маршрута в цепи, на которую нацелено правило, проверьте, что фактическая ширина проложенной меди, сформированной комбинацией дорожек, дуг, заливок, площадок и переходных отверстий, находится в пределах минимального и максимального диапазона

-

Use Impedance Profile — этот параметр становится доступен, когда в Layer Stack Manager определён хотя бы один профиль импеданса. При включении используйте выпадающий список, чтобы выбрать нужный профиль импеданса. Когда правило настроено в этом режиме, требуемая Preferred Width на каждом слое трассировки рассчитывается как часть указанного профиля импеданса (значения Min Width и Max Width также будут установлены в это значение при включении опции). После определения правила, при трассировке цепи, попадающей в область действия правила, ширина дорожки будет автоматически устанавливаться в значение, необходимое для соблюдения заданного импеданса для этого слоя. Когда эта опция включена, Preferred Width нельзя редактировать в правиле, но значения Min Width и Max Width можно.

► Узнать больше о Configuring the Layer Stack for Controlled Impedance Routing

-

Show values for layer stack – этот параметр появляется в диалоге, когда в Layer Stack Manager определено несколько стеков слоёв. Если плата включает несколько стеков слоёв, то ограничения ширины (Width Constraints) должны быть настроены для каждого стека, используя либо поля «для всех слоёв» над изображением, либо поля для конкретных слоёв в таблице атрибутов слоёв.

► Узнать больше о Defining and Configuring Substacks

Настройте ограничения для каждого стека слоёв в проекте.

-

Layer Attributes Table — область сетки в нижней части диалога отображает все сигнальные слои, определённые в стеке слоёв, если только не включена опция Use Impedance Profile. Если эта опция включена, будут отображаться только слои, доступные в составе выбранного профиля импеданса. Отображаются минимальная, максимальная и предпочтительная ширины трассировки и другая информация, специфичная для слоя. Поля ширины трассировки можно задать глобально, определив значения в полях ограничений над изображением, либо индивидуально, вводя значения непосредственно в таблицу. Когда включена опция Use Impedance Profile, требуемые значения ширины будут автоматически рассчитаны и внесены для каждого слоя в таблицу. В этом режиме значения Preferred Width нельзя редактировать, но значения Min Width и Max Width можно.

Применение правила

Параметр Preferred Width учитывается автотрассировщиком (Autorouter).

Параметры Min Width и Max Width учитываются Online DRC и Batch DRC. Они также определяют диапазон допустимых значений, которые можно использовать при интерактивной трассировке (нажмите клавишу Tab во время трассировки, чтобы изменить ширину дорожки в пределах заданного диапазона через панель Properties panel). Если введено значение вне этого диапазона, оно будет автоматически ограничено.

Примечание

Ширина каждой цепи в дифференциальной паре контролируется соответствующим правилом Differential Pairs Routing rule.

Сужение при трассировке (Routing Neck-Down)

Правило по умолчанию: не требуется

Нередко одна и та же цепь трассируется разной шириной по мере прохождения по плате. Например, при входе в BGA или выходе из него часто требуются «выводные» дорожки уже, чем предпочтительные дорожки, допускаемые применённым профилем импеданса. Это правило позволяет задать максимально допустимую суммарную длину таких более узких участков, чтобы маршрут всё равно обеспечивал требуемый импеданс.

Правило можно определить как в представлении Physical Constraint Manager, так и в диалоге PCB Rules and Constraints Editor.

Ограничения

Ограничения для правила Routing Neck-Down

Neck-Down Length задают максимально допустимую длину непрерывных участков маршрута (в каждой цепи, попадающей в область действия правила), ширина которых находится между Min Width и Preferred Width, определёнными применимым правилом Routing Width. Либо используйте сетку, чтобы задать допустимую длину отдельно для каждого слоя.

Применение правила

Включите проверку типа правила Routing Neck-Down для онлайн- и/или пакетной проверки в диалоге Design Rule Checker, чтобы обнаруживать нарушения правил Routing Neck-Down в соответствующих режимах DRC. Обнаруженные нарушения будут отмечены штриховкой на соответствующих дорожках в рабочем поле.

Топология трассировки (Routing Topology)

Правило по умолчанию: требуется

Это правило задаёт топологию, которая должна применяться при трассировке цепей на плате. Топология цепи — это схема/шаблон соединений «вывод-вывод». По умолчанию соединения каждой цепи организуются так, чтобы обеспечить минимальную суммарную длину. Топология применяется по разным причинам: в высокоскоростных проектах, где нужно минимизировать отражения, цепь организуют топологией «гирлянда» (daisy chain); для цепей земли может применяться топология «звезда», чтобы все дорожки сходились в общую точку.

Ограничения

Ограничение по умолчанию для правила Routing Topology

Topology — задаёт топологию, которая будет использоваться для цепи(ей), на которые нацелена область действия (полный запрос) правила. Можно применить следующие топологии:

-

Shortest— эта топология соединяет все узлы цепи так, чтобы получить минимальную суммарную длину соединений. -

Horizontal— эта топология соединяет все узлы, отдавая предпочтение «короткости» по горизонтали перед «короткостью» по вертикали в соотношении 5:1. Используйте этот метод, чтобы принудительно ориентировать трассировку по горизонтали. -

Vertical— эта топология соединяет все узлы, отдавая предпочтение «короткости» по вертикали перед «короткостью» по горизонтали в соотношении 5:1. Используйте этот метод, чтобы принудительно ориентировать трассировку по вертикали. -

Daisy-Simple— эта топология выстраивает все узлы в цепочку, один за другим. Порядок цепочки рассчитывается так, чтобы обеспечить минимальную суммарную длину. Если указаны площадки источника и терминатора, то все остальные площадки выстраиваются между ними, чтобы получить минимально возможную длину. Отредактируйте площадку, чтобы назначить её источником или терминатором. Если задано несколько источников (или терминаторов), они объединяются в цепочку на каждом конце. -

Daisy-MidDriven— эта топология размещает узел(узлы) источника в центре «гирлянды», поровну распределяет нагрузки и выстраивает их цепочками по обе стороны от источника(ов). Требуются два терминатора — по одному на каждом конце. Несколько узлов-источников объединяются в цепочку в центре. Если терминаторов не ровно два, используется топологияDaisy-Simple. -

Daisy-Balanced— эта топология делит все нагрузки на равные цепочки, при этом общее число цепочек равно числу терминаторов. Затем эти цепочки подключаются к источнику по схеме «звезда». Несколько узлов-источников объединяются в цепочку. -

Starburst— эта топология подключает каждый узел напрямую к узлу-источнику. Если присутствуют терминаторы, они подключаются после каждого узла нагрузки. Несколько узлов-источников объединяются в цепочку, как в топологииDaisy-Balanced.

Применение правила

Batch DRC, во время автотрассировки.

Примечания

-

При использовании Autorouter время завершения трассировки может быть больше при применении топологий, отличных от

Shortest. -

Реализацию пользовательских топологий, определённых с помощью From-Tos, можно проверить во время Batch DRC правил проектирования Routing Topology, применённых к соответствующим цепям. Нарушение фиксируется, если между площадками From-To существует электрическое соединение, и кратчайший путь содержит как минимум одну другую площадку этой цепи. Нарушения не будут обнаруживаться для цепей с большим числом площадок (более 20) или примитивов (более 1024).

Приоритет трассировки (Routing Priority)

Правило по умолчанию: требуется

Это правило назначает приоритет трассировки для цепи(ей), на которые оно нацелено. Автотрассировщик использует назначенное значение приоритета, чтобы оценить важность трассировки каждой цепи в проекте и, соответственно, определить, какие цепи следует трассировать в первую очередь.

Ограничения

Ограничение по умолчанию для правила Routing Priority

Routing Priority — значение приоритета, назначенное цепи(ям), на которые нацелен охват (полный запрос) правила. Введите значение между 0 и 100. Чем выше назначенное число, тем выше приоритет при трассировке.

Применение правила

Во время автотрассировки.

Слои трассировки

Правило по умолчанию: требуется

Это правило задает, какие слои разрешено использовать для трассировки.

Ограничения

Ограничения по умолчанию для правила Routing Layers

Enabled Layers — перечислены все сигнальные слои, определенные в текущем проекте согласно стеку слоев. Используйте соответствующую опцию Allow Routing, чтобы при необходимости включать/отключать трассировку на слое.

Применение правила

Online DRC, Batch DRC, при интерактивной трассировке и во время автотрассировки.

Примечание

При использовании Автотрассировщика направление трассировки для каждого включенного сигнального слоя в проекте задается в рамках настройки Situs Autorouter. Направления задаются в диалоге Layer Directions dialog, который открывается нажатием кнопки Edit Layer Directions в диалоге Situs Routing Strategies dialog.

Углы трассировки

Правило по умолчанию: требуется

Это правило задает стиль углов, используемый при автотрассировке.

Ограничения

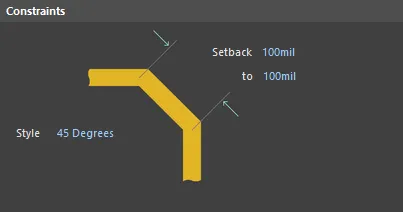

Ограничения по умолчанию для правила Routing Corners

-

Style — определяет, какой стиль углов трассировки использовать. Доступны следующие три стиля:

-

90 Degrees. -

45 Degrees. -

Rounded.

-

-

Setback — эти два поля позволяют задать минимальное и максимальное значение отступа (setback) при использовании стилей углов

45 DegreesиRounded. Отступ — это расстояние от «истинного» положения угла (которое существовало бы при использовании стиля90 Degrees) до точки, в которой Автотрассировщик должен начать фаску или скругление, тем самым фактически управляя размером усечения (miter) или радиусом угла.

Применение правила

Это правило предназначено для сторонних автотрассировщиков, которые реализуют трассировку под 45° как постобработку. Situs Autorouter его не соблюдает, поскольку реализует трассировку под 45° как нативный процесс.

Стиль переходных отверстий для трассировки

Правило по умолчанию: требуется

Это правило задает стиль переходных отверстий, которые можно использовать при трассировке. Можно определить конкретные значения Min/Max/Preferred для диаметра переходного отверстия и размера сверловки — в составе ограничений правила — либо использовать шаблоны, доступные для проекта платы.

Ограничения

Ограничения по умолчанию для правила Routing Via Style. Наведите курсор на изображение, чтобы сравнить два доступных режима.

Mode — используйте выпадающий список, чтобы выбрать один из следующих двух режимов:

- Min/Max preferred — выберите этот режим, чтобы задать допустимые значения (Minimum/Maximum/Preferred) для диаметра переходного отверстия и размера сверловки в самом правиле.

- Template preferred — выберите этот режим, чтобы использовать стили переходных отверстий, определенные через шаблоны переходных отверстий, доступные для платы.

Режим = Min/Max preferred

При выборе этого режима область ограничений изменяется и отображает следующие параметры:

-

Via Diameter — задает диапазон ограничений, который должен соблюдаться для диаметров переходных отверстий, устанавливаемых при трассировке платы. Можно определить следующие отдельные значения:

- Minimum — минимально допустимое значение диаметра переходного отверстия.

- Maximum — максимально допустимое значение диаметра переходного отверстия.

- Preferred — предпочтительное значение диаметра переходного отверстия.

-

Via Hole Size — задает диапазон ограничений, который должен соблюдаться для размеров сверловки переходных отверстий, устанавливаемых при трассировке платы. Можно определить следующие отдельные значения:

- Minimum — минимально допустимое значение размера сверловки переходного отверстия.

- Maximum — максимально допустимое значение размера сверловки переходного отверстия.

- Preferred — предпочтительное значение размера сверловки переходного отверстия.

Режим = Template preferred

При выборе этого режима область ограничений изменяется и отображает следующие параметры:

-

Templates List — перечисляет доступные шаблоны переходных отверстий, которые можно использовать с этим правилом. Это шаблоны переходных отверстий (локальные или определенные в Pad Via Template Libraries), которые становятся доступными для проекта платы как часть Local Pad & Via Library (доступно через панель PCB Pad Via Templates). Для каждого доступного шаблона отображается следующая информация:

- Template Name — имя шаблона (только для чтения). Для локального шаблона используется автоматически сгенерированное имя в соответствии со стандартами IPC. Для шаблона из PvLib это имя можно настроить в рамках конфигурации шаблона в этой библиотеке.

- Description — описание шаблона (только для чтения).

- Library — библиотека, из которой взят шаблон. Это может быть <Local> (когда переходное отверстие определено и сохранено вместе с документом PCB) или имя внешней библиотеки Pad Via Template Library (<LibraryName>.PvLib), которая была сделана доступной для документа PCB.

- Enabled — включите эту опцию, чтобы сделать шаблон доступным для установки переходных отверстий при интерактивной трассировке.

Применение правила

Online DRC, Batch DRC, во время автотрассировки и при интерактивной трассировке.

Когда режим правила установлен в Min/Max preferred, применяются следующие соображения:

- Атрибуты переходного отверстия Preferred используются Автотрассировщиком.

- Атрибуты переходного отверстия Minimum и Maximum соблюдаются Online DRC и Batch DRC.

- Атрибуты переходного отверстия Maximum и Minimum также определяют диапазон допустимых значений, которые можно использовать при интерактивной трассировке — когда вы нажимаете клавишу + (или *) на цифровой клавиатуре для переключения сигнальных слоев трассировки и установки переходного отверстия, нажимаете клавишу / на цифровой клавиатуре для установки fanout‑переходного отверстия или нажимаете сочетание клавиш 2 для установки переходного отверстия без смены слоя.

- Когда при интерактивной трассировке готовится установка переходного отверстия, вы можете циклически переключать определения переходного отверстия Minimum / Preferred / Maximum / User Choice, нажимая клавишу 4. Текущее выбранное состояние отображается в Heads‑Up Display и в строке состояния. Также во время трассировки можно нажать клавишу Tab, чтобы открыть Properties panel, где можно редактировать свойства переходного отверстия в пределах диапазона правила Min/Max. Если введено значение вне диапазона, оно будет автоматически ограничено.

-

Если в Layer Stack Manager определено несколько Via Types, например сквозные и глухие/скрытые переходные отверстия, то для текущего перехода между слоями может быть возможно использование разных Via Types. В этой ситуации нажмите клавишу 6, чтобы циклически переключать разрешенные Via Types. Выбранный Via Type отображается в Heads‑Up Display и в строке состояния. Либо нажмите клавишу 8, чтобы вывести всплывающее меню разрешенных Via Types, и щелкните нужный.

Когда режим правила установлен в Template preferred, применяются следующие соображения:

- Когда при интерактивной трассировке готовится установка переходного отверстия, вы можете циклически переключать включенные шаблоны переходных отверстий, нажимая клавишу 4. Выбранный шаблон отображается в Heads‑Up Display и в строке состояния. Также во время трассировки можно нажать клавишу Tab, чтобы открыть Properties panel, где можно изменить применяемый в данный момент шаблон переходного отверстия.

- Если в Layer Stack Manager определено несколько Via Types, например сквозные и глухие/скрытые переходные отверстия, то для текущего перехода между слоями может быть возможно использование разных Via Types. В этой ситуации нажмите клавишу 6, чтобы циклически переключать разрешенные Via Types. Выбранный Via Type отображается в Heads‑Up Display и в строке состояния. Либо нажмите клавишу 8, чтобы вывести всплывающее меню разрешенных Via Types, и щелкните нужный.

Примечание

Чтобы управлять размером глухих и скрытых переходных отверстий, можно настроить отдельные правила, нацеленные на разные пары слоев. Например, чтобы управлять размером переходного отверстия для глухих переходных отверстий между верхним слоем и mid-layer 1, можно использовать следующий охват (Full Query):

(StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')

Чтобы управлять размером переходного отверстия для скрытых переходных отверстий между mid-layer 2 и mid-layer 3, использовался бы следующий охват:

(StartLayer = 'Mid-Layer2') and (StopLayer = 'Mid-Layer3')

Либо вместо создания отдельных правил можно расширить запрос одного правила, используя OR, следующим образом:

((StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')) or((StartLayer = ' Mid-Layer2') and (StopLayer = 'Mid-Layer3'))

Управление fanout

Правило по умолчанию: требуется

Это правило задаёт параметры fanout, используемые при выполнении fanout для площадок SMD-компонентов в проекте, которые подключены к сигнальным сетям и/или сетям плоскостей питания. По сути, fanout с точки зрения трассировки превращает SMD-площадку в площадку сквозного отверстия, добавляя переходное отверстие (via) и соединяющий проводник. Это значительно повышает вероятность успешной трассировки платы, поскольку сигнал становится доступен на всех слоях трассировки, а не только на верхнем или нижнем слое. Это особенно важно в высокоплотных проектах, где пространство для трассировки очень ограничено.

Ограничения

Ограничения по умолчанию для правила Fanout Control (Fanout_Default)

-

Fanout Style — задаёт, как размещаются переходные отверстия fanout относительно SMD-компонента. Доступны следующие варианты:

-

Auto— выбирает стиль, наиболее подходящий для технологии компонента, чтобы обеспечить оптимальное пространство для трассировки. -

Inline Rows— переходные отверстия fanout размещаются в двух выровненных рядах. -

Staggered Rows— переходные отверстия fanout размещаются в двух шахматных рядах. -

BGA— fanout выполняется в соответствии с заданными параметрами BGA Options. -

Under Pads— переходные отверстия fanout размещаются непосредственно под SMD-площадками компонента.

-

-

Fanout Direction — задаёт направление, используемое для fanout. Доступны следующие варианты:

-

Disable— запретить fanout для SMD-компонентов, на которые нацелено правило. -

In Only— fanout только внутрь. Все переходные отверстия fanout и соединяющие проводники будут размещены внутри ограничивающего прямоугольника компонента. -

Out Only— fanout только наружу. Все переходные отверстия fanout и соединяющие проводники будут размещены вне ограничивающего прямоугольника компонента. -

In Then Out— сначала выполнить fanout всех площадок компонента внутрь. Все площадки, для которых fanout в этом направлении невозможен, следует выполнить наружу (если возможно). -

Out Then In— сначала выполнить fanout всех площадок компонента наружу. Все площадки, для которых fanout в этом направлении невозможен, следует выполнить внутрь (если возможно). -

Alternating In and Out— выполнить fanout всех площадок компонента (где возможно) попеременно: сначала внутрь, затем наружу.

-

-

Direction From Pad — задаёт направление, используемое для fanout. При выполнении fanout для BGA-компонента его площадки делятся на квадранты, и fanout применяется к площадкам в каждом квадранте одновременно. Доступны следующие варианты:

-

Away From Center— fanout для площадок в каждом квадранте выполняется под углом 45° от центра компонента. -

North-East— все площадки в каждом квадранте выполняют fanout в северо-восточном направлении (45° против часовой стрелки от горизонтали). -

South-East— все площадки в каждом квадранте выполняют fanout в юго-восточном направлении (45° по часовой стрелке от горизонтали). -

South-West— все площадки в каждом квадранте выполняют fanout в юго-западном направлении (135° по часовой стрелке от горизонтали). -

North-West— все площадки в каждом квадранте выполняют fanout в северо-западном направлении (135° против часовой стрелки от горизонтали). -

Towards Center— fanout для площадок в каждом квадранте выполняется под углом 45° к центру компонента. В большинстве случаев обеспечить единообразие направления не удастся из‑за того, что требуемое пространство для fanout уже занято переходным отверстием fanout другой площадки. В таких случаях fanout будет выполняться в следующем доступном направлении (северо‑восток, юго‑восток, юго‑запад, северо‑запад).

-

-

Via Placement Mode — задаёт, как размещаются переходные отверстия fanout относительно площадок BGA-компонента. Доступны следующие варианты:

-

Close To Pad (Follow Rules)— переходные отверстия fanout будут размещены максимально близко к соответствующим SMD-площадкам компонента без нарушения заданных правил зазоров. -

Centered Between Pads— переходные отверстия fanout будут центрированы между SMD-площадками компонента.

-

Применение правила

Во время интерактивной трассировки и автотрассировки.

Примечания

-

Следующие правила проектирования Fanout Control по умолчанию создаются автоматически и охватывают типовые типы корпусов компонентов (перечислены в порядке убывания приоритета). Эти правила можно редактировать или определить другие в соответствии с индивидуальными требованиями вашего проекта.

-

Fanout_BGA — с запросом

IsBGA. -

Fanout_LCC - с запросом

IsLCC. -

Fanout_SOIC — с запросом

IsSOIC. -

Fanout_Small — с запросом

(CompPinCount < 5). -

Fanout_Default — с запросом

All.

-

Fanout_BGA — с запросом

-

Стиль, используемый для переходных отверстий fanout, будет соответствовать применимому(ым) правилу(ам) проектирования Routing Via Style. Дополнительные проводники, прокладываемые в процессе fanout от площадки к via, будут соответствовать применимому(ым) правилу(ам) проектирования Routing Width.

-

Чтобы выполнить fanout площадок компонента, убедитесь, что под этим компонентом на любом слое нет полигональных заливок. Полигоны можно «убрать на полку» (shelve) перед созданием fanout и восстановить после.

Проволочная разварка

Правило по умолчанию: не требуется

Это правило задаёт ограничения, относящиеся к проектам, в которых используется Wire Bonding.

Constraints

- Wire To Wire — задаёт минимально допустимое расстояние между 3D-телами соседних бонд-проводов.

- Min Wire Length — задаёт минимально допустимую длину бонд-провода.

- Max Wire Length — задаёт минимально допустимую длину бонд-провода.

- Bond Finger Margin — задаёт минимально допустимый отступ от края площадки бонд-пальца (bond finger pad).

Rule Application

Пакетный DRC

Трассировка дифференциальных пар

Правило по умолчанию: требуется

Это правило определяет ширину трассировки каждой сети в дифференциальной паре и зазор (gap) между сетями в этой паре. Дифференциальные пары обычно трассируются с заданными параметрами «ширина‑зазор», чтобы обеспечить требуемый дифференциальный импеданс для данной пары сетей.

Подробнее о трассировке дифференциальных пар

Ограничения

-

Min WidthОграничения по умолчанию для правила Differential Pairs Routing

- Min Width — задаёт минимально допустимую ширину дорожек при трассировке дифференциальной пары.

- Min Gap — задаёт минимально допустимый зазор между примитивами на разных сетях в пределах одной дифференциальной пары во время трассировки. Параметры Min, Preferred и Max Gap в этом правиле проектирования используются при трассировке, перетрассировке или интерактивном изменении дифференциальной пары (во время Interactive Sliding). Обратите внимание: эти параметры Gap NOT используются при проверке правил (DRC). Во время DRC зазор проверяется применимым правилом Clearance Constraint — см. Примечания ниже для получения дополнительной информации о том, как этим управлять.

- Preferred Width — задаёт предпочтительную ширину дорожек при трассировке дифференциальной пары.

- Preferred Gap — задаёт предпочтительный зазор между примитивами на разных сетях в пределах одной дифференциальной пары.

- Max Width — задаёт максимально допустимую ширину дорожек при трассировке дифференциальной пары.

- Max Gap — задаёт максимально допустимый зазор между примитивами на разных сетях в пределах одной дифференциальной пары.

- Max Uncoupled Length — задаёт значение максимально допустимой несвязанной (uncoupled) длины между положительной и отрицательной сетями в дифференциальной паре.

-

Use Impedance Profile — этот параметр становится доступен, когда в Layer Stack Manager определён хотя бы один профиль импеданса. Если включено, используйте выпадающий список для выбора требуемого профиля импеданса. Когда правило настроено в этом режиме, значения Preferred Width и Preferred Gap, требуемые на каждом слое трассировки, вычисляются в рамках выбранного профиля импеданса. После определения правила, при трассировке дифференциальной пары, попадающей в область действия правила, ширины дорожек и зазор пары будут автоматически установлены в значения, необходимые для данного слоя, чтобы соответствовать заданному импедансу.

-

Show values for layer stack — этот параметр отображается в диалоге, когда в Layer Stack Manager определено несколько стеков слоёв. Если плата включает несколько стеков, то ограничения Differential Pairs Routing должны быть настроены для каждого стека — либо с помощью полей «для всех слоёв» над изображением, либо с помощью полей для конкретных слоёв в таблице Layer Attributes Table.

- Layer Attributes Table — область таблицы в нижней части диалога отображает все сигнальные слои, определённые в стеке слоёв, если только не включён параметр Use Impedance Profile. Если этот параметр включён, будут показаны только слои, доступные в составе выбранного профиля импеданса. Отображаются минимальные, максимальные и предпочтительные ограничения по ширине и зазору, а также другая информация, специфичная для слоя. Поля Width и Gap можно задать глобально, указав значения в полях ограничений над изображением, либо индивидуально — вводом значений непосредственно в таблицу. Когда включён параметр Use Impedance Profile, требуемые значения ширины будут автоматически рассчитаны и внесены для каждого слоя в таблице. В этом режиме значения Preferred Width и Preferred Gap редактировать нельзя, но значения Min и Max — можно.

Применение правила

Онлайн DRC, пакетный DRC, интерактивная трассировка (и перетрассировка), автотрассировка, интерактивная подстройка длины (Min Gap применяется), а также при интерактивном изменении пары, например при сдвиге сегмента дорожки одной из сетей пары.

Примечания

- Хотя ширина каждой цепи в дифференциальной паре контролируется соответствующим правилом Differential Pairs Routing (а не правилом Width), проверка зазоров между цепями в этой паре по-прежнему определяется применимым правилом проектирования Clearance. Если значение gap, используемое при трассировке дифференциальной пары, меньше минимально допустимого зазора между цепями дифференциальной пары, заданного правилом проектирования Electrical Clearance, возникнет нарушение правила Electrical Clearance. Иными словами, необходимо определить правило Clearance, нацеленное на дифференциальную пару (на конкретном слое, где это требуется), с режимом проверки соединённости, установленным в Same Differential Pair , и с зазором, заданным равным или меньшим, чем значение ограничения Min Gap, определённого для этого слоя в составе соответствующего правила Differential Pairs Routing.

- Зазор от цепи в дифференциальной паре до любого other электрического объекта, не входящего в пару, контролируется соответствующим правилом Clearance.

- Хотя оптимальные настройки Width-Gap могут быть достижимы для большей части платы, часто встречаются области, например под компонентом BGA, где необходимо использовать меньшие и более «плотные» настройки Width-Gap. Задание Min Gap меньше, чем Preferred Gap, позволяет трассировщику сближать проводники пары там, где этого требуют препятствия. Это работает, но имеет свою цену: операции трассировки становятся значительно сложнее и, следовательно, медленнее. Этого же можно добиться, определив несколько правил трассировки дифференциальных пар: правило с более низким приоритетом, нацеленное на дифференциальную пару по всей плате, и правило с более высоким приоритетом, нацеленное на дифференциальную пару в конкретной области, где требуется более узкая настройка Width-Gap. Затем вы нацеливаете дифференциальную пару в этой области, определив для неё правило Room Definition, и используете эту room как часть области действия (scope) правила трассировки дифференциальной пары, которому требуется более «плотная» настройка Width-Gap.

- Классы Differential Pair можно определить на схеме для использования при задании области действия правил (rule scoping).

► Узнать больше о проверке зазоров дифференциальных пар

).

). ).

).

Локализовано с помощью ИИ

Локализовано с помощью ИИ