配線ルールの種類

Routingカテゴリの設計ルールは以下の通りです。

Routingカテゴリの設計ルール

幅

デフォルトルール:必須

このルールは、銅(信号)層に配置されるトラックの幅を定義します。

制約

幅ルールに適用される制約で、すべての層に適用されます。グリッドに層固有の値を入力してください(カーソルを合わせると表示されます)。

-

Preferred Width - ボードの配線時にトラックに使用される推奨幅を指定します。

-

Min Width - ボードの配線時にトラックに使用される許容最小幅を指定します。

-

Max Width - ボードの配線時にトラックに使用される許容最大幅を指定します。

-

Check Tracks/Arcs Min/Max Width Individually - ルールの対象となるネット内の各ルートについて、各個のトラックおよびアークの幅が最小および最大の範囲内にあるかをチェックします(

)。 -

Check Min/Max Width for Physically Connected - ルールの対象となるネット内の各ルートについて、トラック、アーク、フィル、パッド、ビアの組み合わせによって形成された実際の銅の幅が最小および最大の範囲内にあるかをチェックします(

)。

)。

-

Use Impedance Profile - レイヤースタックマネージャーで少なくとも1つのインピーダンスプロファイルが定義されている場合に利用可能になります。有効にすると、ドロップダウンから希望のインピーダンスプロファイルを選択します。このモードでルールが設定されると、各配線層で要求される推奨幅は、指定されたインピーダンスプロファイルの一部として計算されます。このオプションが有効になると、ルール内の推奨幅は編集できませんが、最小幅と最大幅の値は編集できます。

►制御インピーダンス配線のためのレイヤースタックの設定についてもっと学ぶ

-

Show values for layer stack

- このオプションは、レイヤースタックマネージャーで複数のレイヤースタックが定義されている場合にダイアログに表示されます。ボードに複数のレイヤースタックが含まれている場合、幅の制約は、画像の上の全層フィールドまたはレイヤー属性テーブルの層固有フィールドを使用して、各スタックごとに設定する必要があります。 ►サブスタックの定義と設定についてもっと学ぶ

Javascript

設計内の各レイヤースタックの制約を設定します。 -

レイヤー属性テーブル - ダイアログの下部にあるグリッド領域には、Use Impedance Profileオプションが有効になっていない限り、レイヤースタックで定義されているすべての信号層が表示されます。このオプションが有効になっている場合は、選択されたインピーダンスプロファイルの一部として利用可能な層のみが表示されます。最小、最大、および推奨の配線幅およびその他の層固有情報が表示されます。配線幅フィールドは、画像の上の制約フィールドで値を定義することによりグローバルに設定することも、テーブルに直接値を入力することにより個別に設定することもできます。Use Impedance Profileオプションが有効になっている場合、必要な幅のエントリはテーブルの各層に対して自動的に計算されて入力されます。このモードでは、推奨幅の値は編集できませんが、最小幅と最大幅の値は編集できます。

ルール適用

オートルーターは、Preferred Width設定に従います。

Min WidthおよびMax Widthの設定は、オンラインDRCおよびバッチDRCによって遵守されます。また、これらはインタラクティブ配線中に使用できる許容値の範囲を決定します(配線中にTabキーを押すことで、Propertiesパネルを通じて定義された範囲内でトレース幅を変更できます)。この範囲外の値が入力された場合、自動的にクリップされます。

注意

各ネットの幅は、適用される差動ペア配線ルールによって監視されます。

ネックダウンの配線

デフォルトルール:不要

ネットがボードを横断する際に異なる幅で配線されることは珍しくありません。例えば、BGAに向かって配線する場合やBGAから出る場合、適用されたインピーダンスプロファイルによって許可された好ましい幅のルートよりも狭い逃げルートが必要になることがよくあります。このルールでは、そのような狭いトレースの最大許容全長を定義し、ルートが要求されるインピーダンスを還元することを可能にします。

ルールは、制約マネージャーのPhysicalビューとPCB Rules and 制約 Editorダイアログの両方で定義できます。

制約

Neck-Down Lengthは、適用される配線幅ルールで定義されたMin WidthとPreferred Widthの間にある幅の各ネットがスコープされたルールに対して、連続ルートの最大許可長を指定します。あるいは、グリッドを使用してレイヤーごとに許可される長さを定義します。

ルール適用

Design Rule Checkerダイアログでオンラインおよび/またはバッチチェックのためにRouting Neck-Downルールタイプチェックを有効にして、対応するDRCモードでの配線ネックダウンルールの違反を検出します。検出されたルール違反は、設計空間の対応するトレース上にハッチパターンでマークされます。

配線トポロジー

デフォルトルール:必須

このルールは、基板上でネットを配線する際に使用するトポロジーを指定します。ネットのトポロジーはピン間接続の配置またはパターンです。デフォルトでは、各ネットのピン間接続は全体の接続長を最短にするように配置されます。トポロジーはさまざまな理由でネットに適用されます。信号反射を最小限に抑える必要がある高速設計では、ネットはデイジーチェイントポロジーで配置されます。グラウンドネットには、すべてのトラックが共通のポイントに戻ることを確実にするためにスタートポロジーが適用される可能性があります。

制約

配線トポロジールールのデフォルト制約

Topology - スコープ(完全なクエリ)に対して対象となるネットワークのトポロジーを定義します。適用できるトポロジーは以下の通りです:

-

Shortest- このトポロジーは、ネット内のすべてのノードを接続して、全体の接続長を最短にします。 -

Horizontal- このトポロジーはすべてのノードを接続し、垂直の短さよりも水平方向の短さを5対1の比率で優先します。この方法を使用して水平方向の配線を強制してください。 -

Vertical- このトポロジーはすべてのノードを接続し、水平の短さよりも垂直の短さを5:1の比率で好む。配線を垂直方向に強制するためにこの方法を使用してください。 -

Daisy-Simple- このトポロジーは、すべてのノードを一つずつ連鎖させます。連鎖の順序は、全体の長さが最短になるように計算されます。ソースとターミネーターパッドが指定されている場合、他のすべてのパッドはその間に連鎖され、可能な限り短い長さになります。パッドを編集してそれをソースまたはターミネーターに設定します。複数のソース(またはターミネーター)が指定されている場合、それらは両端で連鎖します。 -

Daisy-MidDriven- このトポロジーは、ソースノードをデイジーチェーンの中心に配置し、負荷を均等に分割し、ソースの両側にチェーン接続します。端に1つずつ、合計2つのターミネーターが必要です。複数のソースノードが中央でチェーン接続されます。ターミネーターが正確に2つでない場合は、Daisy-Simpleトポロジーが使用されます。 -

Daisy-Balanced- このトポロジーはすべての負荷を等しいチェーンに分割し、チェーンの合計数はターミネーターの数と等しくなります。これらのチェーンは星形パターンでソースに接続されます。複数のソースノードがチェーンで接続されています。 -

Starburst- このトポロジーは各ノードを直接ソースノードに接続します。終端装置が存在する場合、それらは各負荷ノードの後に接続されます。複数のソースノードが連結され、Daisy-Balancedトポロジーのようになります。

ルール適用

オート配線中のバッチDRC。

注意

-

オートルーターを使用する場合、

Shortest以外のトポロジーを使用すると、配線完了時間が長くなる場合があります。 -

カスタムトポロジーはFrom-Tosを使用して定義され、対応するネットに適用された配線トポロジーデザインルールのバッチDRC中にチェックできます。From-Toのパッド間に電気的接続があり、最短経路にこのネットの他のパッドが少なくとも1つ含まれている場合、違反が検出されます。パッド(20以上)またはプリミティブ(1024以上)の数が多いネットでは、違反は検出されません。

配線優先度

デフォルトルール:必須

このルールは、ルールの対象となるネットに配線優先度を割り当てます。オートルーターは、割り当てられた優先度値を使用して、設計内の各ネットの配線の重要性を評価し、どのネットを最初に配線するかを決定します。

制約

配線優先度ルールのデフォルト制約

Routing Priority - ルールの範囲(完全クエリ)の対象となるネットに割り当てられた優先度値。 0から100の間の値を入力します。割り当てられた数値が高いほど、配線時の優先度が高くなります。

ルール適用

オート配線中。

配線レイヤー

デフォルトルール:必須

このルールは、配線に使用できるレイヤーを指定します。

制約

配線レイヤールールのデフォルト制約

Enabled Layers - レイヤースタックアップによって定義された設計の現在定義されている各信号レイヤーがリストされます。必要に応じて、関連するAllow Routingオプションを使用して、レイヤーでの配線を有効/無効にします。

ルール適用

オンラインDRC、バッチDRC、インタラクティブ配線中、およびオート配線中。

注記

オートルーターを使用する場合、設計内の各有効な信号レイヤーの配線方向は、Situsオートルーターのセットアップの一部として定義されます。方向は、Layer Directionsダイアログで指定され、Edit Layer DirectionsボタンをクリックしてSitus Routing Strategiesダイアログにアクセスすることでアクセスできます。

配線コーナー

デフォルトルール:必須

このルールは、オート配線中に使用されるコーナースタイルを指定します。

制約

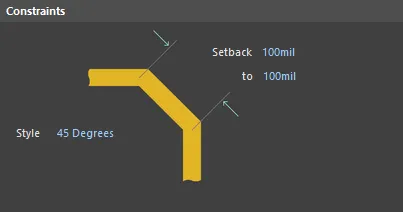

配線コーナールールのデフォルト制約

-

Style - 使用する配線コーナースタイルを指定します。以下の3つのスタイルが利用可能です:

-

90度。 -

45度。 -

丸み。

-

-

Setback - これら2つのフィールドを使用して、

45度および丸みコーナースタイルを使用する場合のセットバックの最小値と最大値を定義します。セットバックは、「真の」コーナー位置(90度スタイルを使用した場合に存在するであろう位置)から、オートルーターがその面取りまたは丸みを開始すべき点までの距離であり、ミターサイズまたはコーナー半径を効果的に制御します。

ルール適用

このルールは、45°配線をポストプロセスとして実装するサードパーティのオートルーターによって使用されることを意図しています。Situsオートルーターには適用されず、45°配線をネイティブプロセスとして実装します。

配線ビアスタイル

デフォルトルール:必須

このルールは、配線時に使用できるビアのスタイルを指定します。ルールの制約の一部として定義されたビアの直径と穴サイズについて、特定の最小/最大/推奨値を定義するか、ボード設計に利用可能なテンプレートを使用できます。

制約

スタイルルールによる配線のデフォルト制約。画像にマウスを重ねると、利用可能な二つのモードを比較できます。

Mode - ドロップダウンを使用して、次の2つのモードから選択してください:

-

Min/Max preferred - このモードを選択して、ルール自体の一部としてビアの直径と孔のサイズの許容値(最小/最大/推奨)を設定します。

-

Template preferred - このモードを選択すると、ボードで利用可能なテンプレートを通じて定義されたスタイルを使用できるようになります。

Mode = Min/Max preferred

このモードが選択されると、制約領域が変更され、次のオプションが表示されます:

-

Via Diameter - 基板を配線する際に配置されるビアの直径に関して遵守すべき制約範囲の値を指定します。次の個々の値が定義可能です:

-

Minimum - ビアの直径に対する最小許容値。

-

Maximum - ビアの直径に対する最大許容値。

-

Preferred - ビア径の推奨値。

-

-

Via Hole Size - ボードを配線する際に配置されたビアの穴サイズに関して遵守すべき制約範囲の値を指定します。次の個々の値が定義可能です:

-

Minimum - ビアホールサイズの最小許容値。

-

Maximum - ビアホールサイズの最大許容値。

-

Preferred - ビアホールサイズの好ましい値。

-

Mode = Template preferred

このモードが選択されると、制約領域が変更され、次のオプションが表示されます。

-

Templates List - 利用可能なテンプレートをルールと共に使用できるリストです。これらは、ボード設計に提供されるテンプレート(ローカルまたはPad Via Template Librariesに定義されたもの)であり、Local Pad & Via Libraryの一部として提供されます(PCB Pad Via Templatesパネルを通じてアクセス)。利用可能な各テンプレートについて、以下の情報が提示されます:

-

Template Name - テンプレートの読み取り専用名。ローカルテンプレートの場合、自動生成された名称がIPC基準に従って使用されます。PvLibから取得したテンプレートの場合、この名称はそのライブラリ内でのテンプレート設定の一部としてカスタマイズできます。

-

Description - テンプレート用に書かれた読み取り専用の説明。

-

Library - テンプレートが供給されるライブラリ。このライブラリは、PCBドキュメントと共に定義され、保存された<Local>であるか、PCBドキュメントに利用可能な外部Pad Viaテンプレートライブラリ(<LibraryName>.PvLib)の名前です。

-

Enabled - このオプションを有効にすると、インタラクティブ配線中に配置を介してテンプレートを利用可能にすることができます。

-

テンプレートを介して、PCB設計ファイルと一緒に保存されたビアはローカルであるか、または利用可能なライブラリセットの一部としてインストールされた1つまたは複数のパッドビアテンプレートライブラリ(*.PvLib)から取得できます。

ルール適用

オンラインDRC、バッチDRC、自動配線中、およびインタラクティブ配線中。

ルールのモードがMin/Max preferredに設定されている場合、以下の考慮事項が適用されます:

-

Preferredビア属性は、自動ルーターによって使用されます。

-

オンラインDRCとバッチDRCは、属性によるMinimumとMaximumを遵守しています。

-

属性を介してのMaximumとMinimumは、対話型配線中に使用できる許容値の範囲も決定します。これは、数値キーパッドの + (または *)キーを押して配線信号レイヤーを切り替え、ビアをドロップする場合、数値キーパッドの / キーを押してファンアウトビアを配置する場合、または 2 ショートカットキーを押してレイヤーを変更せずにビアを配置する場合です。

-

インタラクティブ配線中にビアの配置が行われる際、4キーを押すことでMinimum/Preferred/Maximum/User Choiceのビア定義をサイクルできます。現在選択されている状態はヘッズアップディスプレイとステータスバーに表示されます。また、配線中にTabキーを押すことでPropertiesパネルにアクセスでき、そこから最小/最大ルール範囲内でビアのプロパティを編集できます。範囲外の値が入力されると、自動的にクリップされます。

-

レイヤースタックマネージャーで複数のビアタイプが定義されている場合、例えばスルーホールビアやブラインド/ベリッドビアなど、異なるビアタイプが現在のレイヤー遷移に使用される可能性があります。この状況では、6キーを押して許可されているビアタイプを切り替えます。選択されたビアタイプはヘッズアップディスプレイとステータスバーに表示されます。または、8キーを押して許可されているビアタイプのポップアップメニューを表示し、必要なものをクリックします。

ルールのモードがTemplate preferredに設定されている場合、以下の考慮事項が適用されます:

-

インタラクティブ配線中に配線ビアを配置しようとするとき、4キーを押して有効なビアテンプレートを切り替えることができます。選択されたテンプレートはヘッズアップディスプレイとステータスバーに表示されます。また、配線中にTabキーを押してPropertiesパネルにアクセスし、現在適用されているビアテンプレートを変更することもできます。

-

レイヤースタックマネージャーで複数のビアタイプが定義されている場合、例えばスルーホールビアやブラインド/ベリッドビアなど、異なるビアタイプが現在のレイヤー遷移に使用される可能性があります。この状況では、6キーを押して許可されているビアタイプを切り替えます。選択されたビアタイプはヘッズアップディスプレイとステータスバーに表示されます。または、8キーを押して許可されているビアタイプのポップアップメニューを表示し、必要なものをクリックします。

注意

ブラインドビアとベリッドビアのサイズを制御するために、異なるレイヤーペアを対象とした個別のルールを設定できます。例えば、トップレイヤーとミッドレイヤー1の間のブラインドビアのサイズを制御するには、次のスコープ(フルクエリー)を使用できます:

(StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')

ミッドレイヤー2とミッドレイヤー3の間のベリッドビアのサイズを制御するには、次のスコープを使用します:

(StartLayer = 'Mid-Layer2') and (StopLayer = 'Mid-Layer3')

または、個別のルールを作成する代わりに、次のようにORを使用して1つのルールクエリを拡張することもできます:

((StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')) or((StartLayer = ' Mid-Layer2') and (StopLayer = 'Mid-Layer3'))

ファンアウト制御

デフォルトルール:必須

このルールは、設計内の信号および/または電力プレーンネットに接続する表面実装コンポーネントのパッドをファンアウトする際に使用されるファンアウトオプションを指定します。ファンアウトは、ビアと接続トラックを追加することでSMTパッドを配線の観点からスルーホールパッドに変換し、これにより信号がトップレイヤーまたはボトムレイヤーだけでなく、すべての配線レイヤーに利用可能になり、ボードの成功率が大幅に向上します。これは、配線スペースが非常に限られている高密度設計で特に必要です。

制約

ファンアウト制御ルールのデフォルト制約(Fanout_Default)

-

Fanout Style - SMTコンポーネントに対してファンアウトビアが配置される方法を指定します。以下のオプションが利用可能です:

-

Auto- コンポーネント技術に最も適したスタイルを選択し、最適な配線スペース結果を提供します。 -

Inline Rows- ファンアウトビアは2つの整列した行内に配置されます。 -

Staggered Rows- ファンアウトビアは2つの交互の行内に配置されます。 -

BGA- 指定されたBGAオプションに従ってファンアウトが行われます。 -

Under Pads- ファンアウトビアはSMTコンポーネントパッドの直下に配置されます。

-

-

Fanout Direction - ファンアウトの使用方向を指定します。以下のオプションが利用可能です

-

Disable- ルールによって対象とされるSMTコンポーネントに対してファンアウトを許可しないでください。 -

In Only- ファンアウトは内向きの方向にのみ行います。すべてのファンアウトビアと接続トラックは、コンポーネントの境界矩形内に配置されます。 -

Out Only- ファナウトは外向きの方向にのみ行います。すべてのファナウトビアと接続トラックは、コンポーネントの境界矩形の外側に配置されます。 -

In Then Out- 最初にすべてのコンポーネントパッドを内向きにファンアウトします。この方向にファンアウトできないすべてのパッドは、外向きにファンアウトする必要があります(可能であれば)。 -

Out Then In- 最初にすべてのコンポーネントパッドを外向きにファンアウトします。この方向にファンアウトできないすべてのパッドは、内向きにファンアウトする必要があります(可能であれば)。 -

Alternating In and Out- 可能な限りすべてのコンポーネントパッドを交互に展開し、最初は内側、次に外側に向かって展開します。

-

-

Direction From Pad - ファンアウトに使用する方向を指定します。BGAコンポーネントがファンアウトされると、そのパッドは四分円に分割され、各四分円のパッドに同時にファンアウトが適用されます。以下のオプションが利用可能です:

-

Away From Center- 各四分円におけるパッドへのファンアウトは、コンポーネントの中心から45°の角度で適用されます。 -

North-East- 各象限のすべてのパッドは、北東の方向(水平から45°反時計回り)に広がっています。 -

South-East- 各象限のすべてのパッドは、南東方向(水平から時計回りに45°)に広がっています。 -

South-West- 各象限のすべてのパッドは南西方向(水平面から時計回りに135°)に広がっています。 -

North-West- 各象限のすべてのパッドは、北西方向(水平から反時計回りに135°)に広がっています。 -

Towards Center- 各象限のパッドのファンアウトは、コンポーネントの中心に向かって45°の角度で適用されます。ほとんどの場合、必要なファンアウトスペースが他のパッドのファンアウトによって既に取られているため、方向の均一性は不可能です。この場合、ファンアウトは次の利用可能な方向(北東、南東、南西、北西)で発生します。

-

-

Via Placement Mode - ファナウトビアがBGAコンポーネントのパッドに対してどのように配置されるかを指定します。次のオプションが利用可能です:

-

Close To Pad (Follow Rules)- ファンアウトビアは、定義されたクリアランスルールに違反しない範囲で、対応するSMTコンポーネントパッドにできるだけ近く配置されます。 -

Centered Between Pads- ファンアウトビアはSMTコンポーネントパッドの間に配置されます。

-

ルール適用

インタラクティブ配線とオート配線中。

注意

-

以下のデフォルトのファンアウト制御設計ルールは、利用可能な典型的なコンポーネントパッケージタイプを網羅するために自動的に作成されます(優先順位の降順でリスト)。これらのルールは編集可能であり、個々の設計要件に応じて他のルールを定義することもできます。

-

Fanout_BGA –

IsBGAクエリ. -

Fanout_LCC -

IsLCCクエリ. -

Fanout_SOIC -

IsSOICクエリ. -

Fanout_Small -

(CompPinCount < 5)クエリ. -

Fanout_Default -

Allクエリ.

-

-

ファンアウトビアに使用されるスタイルは、適用可能な配線ビアスタイル設計ルールに従います。パッドからビアまでのファンアウトプロセスの一部として敷設される追加のトラックは、適用可能な配線幅設計ルールに従います。

-

コンポーネントのパッドをファンアウトするには、すべてのレイヤーでこのコンポーネントの下にポリゴンの注入がないことを確認してください。ポリゴンはファンアウトを作成する前に棚に置き、後で復元できます。

ワイヤボンディング

デフォルトルール:不要

この規則は、ワイヤボンディングを使用した設計に関連する制約を定義します。

制約

-

Wire To Wire – 隣接したボンドワイヤの3D物体間の最小許容距離を指定します。

-

Min Wire Length – 接続ワイヤの最小許容長さを指定します。

-

Max Wire Length – 接続ワイヤの最小許容長さを指定します。

-

Bond Finger Margin – ボンドフィンガーパッドの端からの最小許容マージンを指定します。

ルール適用

バッチDRC

差動ペア配線

デフォルトルール:必須

このルールは、差動ペア内の各ネットの配線幅とそのペア内のネット間のクリアランス(またはギャップ)を定義します。差動ペアは通常、そのネットペアに必要な差動インピーダンスを提供するために、特定の幅-ギャップ設定で配線されます。

差動ペア配線についてもっと学ぶ

制御インピーダンス配線についてもっと学ぶ

制約

差動ペア配線ルールのデフォルト制約

-

Min Width - 差動ペアの配線時に使用されるトラックの最小許容幅を指定します。

-

Min Gap - 配線中に同じ差動ペア内の異なるネット上のプリミティブ間の最小許容クリアランスを指定します。この設計ルールの最小、優先、最大ギャップ設定は、差動ペアが配線、再配線、またはインタラクティブに変更される(インタラクティブスライディング中)時に使用されます。これらのギャップ設定は、ルールチェック(DRC)中には使用されません。DRC中には、適用されるクリアランス制約ルールによってギャップがテストされます - これを管理する方法の詳細については、以下の注記を参照してください。

-

Preferred Width - 差動ペアの配線時に使用される優先幅を指定します。

-

Preferred Gap - 同じ差動ペア内の異なるネット上のプリミティブ間の優先クリアランスを指定します。

-

Max Width - 差動ペアの配線時に使用される最大許容幅を指定します。

-

Max Gap - 同じ差動ペア内の異なるネット上のプリミティブ間の最大許容クリアランスを指定します。

-

Max Uncoupled Length - 差動ペア内の正と負のネット間の最大許容非結合長を指定します。

-

Use Impedance Profile - レイヤースタックマネージャーで少なくとも1つのインピーダンスプロファイルが定義されている場合にこのオプションが利用可能になります。有効にすると、ドロップダウンから必要なインピーダンスプロファイルを選択します。このモードでルールが設定されると、各配線層で必要な優先幅と優先ギャップは、指定されたインピーダンスプロファイルの一部として計算されます。ルールが定義されると、ルールの範囲に該当する差動ペアを配線する際に、その層で指定されたインピーダンスを満たすために必要なトラック幅とペアギャップが自動的に設定されます。

-

Show values for layer stack - このオプションは、レイヤースタックマネージャーで複数のレイヤースタックが定義されている場合にダイアログに表示されます。ボードに複数のレイヤースタックが含まれている場合、差動ペア配線制約は、画像上の全層フィールドまたはレイヤー属性テーブルの層固有フィールドを使用して、各レイヤースタックごとに設定する必要があります。

-

レイヤー属性テーブル - ダイアログの下部にあるグリッド領域には、Use Impedance Profileオプションが有効になっていない限り、レイヤースタックで定義されているすべての信号層が表示されます。このオプションが有効な場合、選択されたインピーダンスプロファイルの一部として利用可能な層のみが表示されます。最小、最大、優先幅およびギャップ制約およびその他の層固有情報が表示されます。配線幅およびギャップフィールドは、画像上の制約フィールドに値を定義することにより、グローバルに設定することも、テーブルに直接値を入力することにより、個別に設定することもできます。Use Impedance Profileオプションが有効な場合、必要な幅エントリはテーブルの各層に対して自動的に計算されて入力されます。このモードでは、優先幅と優先ギャップ値は編集できませんが、最小値と最大値は編集できます。

ルールの適用

オンラインDRC、バッチDRC、インタラクティブ配線(および再配線)、オート配線、インタラクティブな長さ調整(Min Gap が適用される)、およびペアの一方のネットのトラックセグメントをスライドさせるような、ペアをインタラクティブに変更する場合。

注意

-

差動ペアの各ネットの幅は適用される差動ペアの配線ルールによって監視されます(幅ルールによってではなく)、しかしそのペアのネット間のクリアランスチェックは依然として適用されるクリアランス設計ルールに従います。差動ペアの配線に使用されるギャップ値が電気クリアランス設計ルールで設定された差動ペアネット間の最小許容クリアランスよりも小さい場合、電気クリアランス設計ルールの違反が発生します。言い換えれば、差動ペアをターゲットにしたクリアランスルールを定義する必要があり(必要な特定のレイヤーで)、その接続チェックモードはSame Differential Pairに設定され、クリアランスはそのレイヤーの適用される差動ペアの配線ルールの一部として定義されたMin Gap制約の値と等しいか、あるいはそれ以下に設定される必要があります。

-

差動ペアのネットからそのペアに含まれない他の電気オブジェクトまでのクリアランスは、適用されるクリアランスルールによって監視されます。

-

最適な幅ギャップ設定はほとんどの基板で達成可能ですが、BGAコンポーネントの下のような領域では、より小さくきつい幅ギャップ設定を使用する必要があることがよくあります。最小ギャップを推奨ギャップよりも小さく定義することで、ルーターはペアメンバーを互いに近づけることができ、障害物がこれを要求する場合に役立ちます。これは機能しますが、コストがかかります。配線操作はずっと複雑になり、そのため遅くなります。この要件は、基板全体の差動ペアを対象にする低優先度のルールと、狭い幅ギャップ設定が必要な特定の領域の差動ペアを対象にする高優先度のルールを定義することで達成することもできます。そして、その領域の差動ペアをターゲットにして、その領域のためのルーム定義ルールを定義し、そのルームを狭い幅ギャップ設定が必要な差動ペア配線ルールの範囲の一部として使用します

-

差動ペアクラスは、ルールスコーピングで使用するために回路図上で定義できます。

► 差動ペアクリアランスチェックについてもっと学ぶ