Altium Designer 全新功能

本页详细说明了 Altium Designer、Altium Designer Develop 与 Altium Designer Agile(即将发布) 各版本发布所包含的改进。每次更新不仅推进并成熟既有技术,还会根据客户在 AltiumLive Community 中的 BugCrunch 反馈,对软件进行多项修复与功能增强,帮助您持续打造前沿电子技术。

Version 26.3

Altium Designer Develop – 发布:2026 年 2 月 5 日 – Version 26.3.0 (build 5)

Altium Designer Agile(即将发布) – 发布:2026 年 2 月 5 日 – Version 26.3.0 (build 18)

Altium Designer – 发布:2026 年 2 月 5 日 – Version 26.3.0 (build 6)

PCB 设计改进

增强对 SOLIDWORKS 与 Parasolid 格式的支持

-

在处理三维主体时,已新增对 SOLIDWORKS 2024 和 2025 模型(

*.SldPrt)的支持。 -

将 PCB 导出为 Parasolid 文件格式(

*.x_t)时,现在使用 Parasolid 35.1 版本。这使得较新版本的 SOLIDWORKS(2024 和 2025)能够正确打开/导入该文件。

更多信息,请参阅Mechanical Data Import-Export Support 页面。

线束设计改进

显示跳线导线

现在,在线束接线图中定义的跳线导线,会在关联的线束项目布局图中得到正确呈现。跳线导线用于连接同一连接器的两个凹腔。在线束项目布局图中选择某个束体后,Properties面板的Bundle Objects区域会将这类起点与终点位于同一连接点的跳线导线,作为该束体的一部分显示出来。

此类导线仅支持手动定义长度。输入的长度值随后会被纳入线束项目的 ActiveBOM 文档以及制造图纸(BOM 表与接线清单)中。

更多信息,请参阅Creating the Layout Drawing页面。

改进 “Update From Libraries” 功能

针对线束设计的线束接线图(*.WirDoc)与线束项目布局图(*.LdrDoc),从库更新(Tools » Update From Libraries)功能已得到改进。

-

当从线束接线图访问该功能时,现在也会包含导线、凹腔元器件,以及关联元器件。

-

当从线束项目布局图访问该功能时,现在也会包含线束护套、布局标签,以及关联元器件。

更多信息,请参阅Defining the Wiring Diagram 与 Creating the Layout Drawing 页面。

版本 26.2

Altium Designer Develop – 发布日期:2026 年 1 月 8 日 – 版本 26.2.0 (build 10)

Altium Designer Agile(即将发布)– 发布日期:2026 年 1 月 8 日 – 版本 26.2.0 (build 28)

Altium Designer – 发布日期:2026 年 1 月 8 日 – 版本 26.2.0 (build 7)

Wire Bonding 改进

支持拼板 PCB

在 3D 查看拼板 PCB 文档时,现可显示 Wire Bonding 和裸片焊盘。

此外,现在支持从拼板 PCB 文档生成 Wire Bonding Table 报告。

有关拼板 PCB 的更多信息,请参阅 拼板 页面。

用于检测键合线的新查询关键字

新增 IsBondwire 查询关键字(PCB 对象类型检查),可用于在 PCB/PcbLib 中构建逻辑查询表达式,以筛选对象或限定设计规则范围。

更多信息请参阅对象类型检查页面。

线束设计改进

支持在线束束体上放置中断点

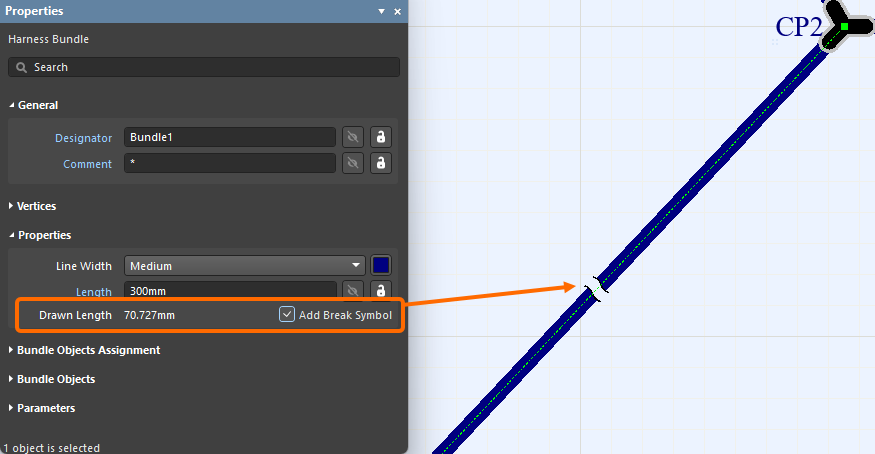

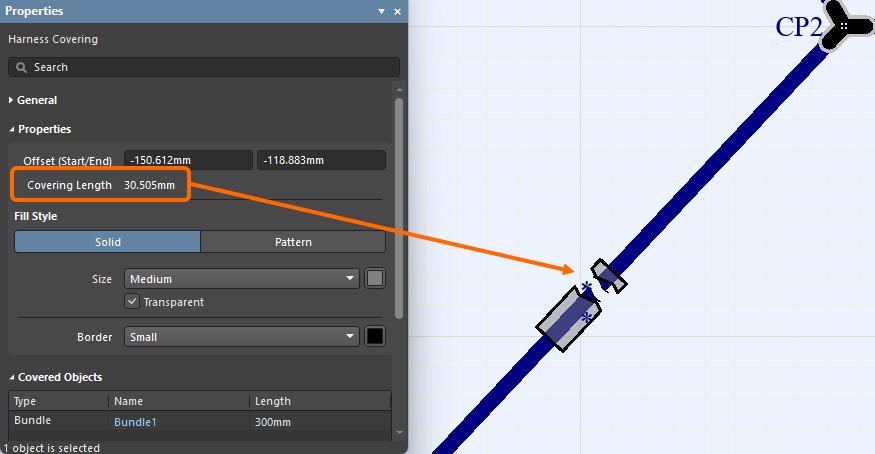

在线束布局图(*.LdrDoc)中,现在可以在线束束体上放置中断点,用于表明该束体为不按比例显示。束体会在其最长线段的中间位置显示一个中断符号(如下方第一张图所示),并且在 Properties 中会显示 Drawn Length,它反映的是在设计空间中按绘图结果得到的束体长度。通常情况下,束体的实际物理长度会大得多。当设置了 Length 字段(表示实际物理长度)且该值与绘制长度不同,束体会在其最长线段的中心显示中断符号,以指示该束体不按比例显示。要放置中断,请在束体属性的 Properties 区域中启用 Add Break Symbol 选项。覆盖了带有中断点之线束束体的线束包覆也会在相同位置显示该中断。如果线束包覆正好在束体的中断点处结束,包覆的绘制会略微加长,如第二张图所示。

更多信息,请参阅创建线束布局图页面。

数据管理改进

同步元件时可保留生命周期状态

在本次版本中,通过 Altium Designer 的 Components Synchronization 功能,在你的工作区与元件数据库之间执行元件同步时,现在支持保留生命周期状态。

该功能由新的 Preserve lifecycle state 选项提供支持。在 Components Synchronization Configuration 文档(*.CmpSync)中选定数据源(表)后,可在 Properties 面板的 Advanced 部分找到该选项。

请注意:该功能适用于被分配了 Allow to skip lifecycle state change for new revisions 操作权限的用户(了解更多可参阅 为工作区设置全局操作权限)。

关于 Components Synchronization 功能的更多信息,请参阅元件数据库到工作区的数据同步页面。

Altium Designer 26.2 正式公开的功能

以下功能在本次发行版中正式转为 Public:

-

BOM CoDesign - 自 25.1 起可用

-

从 BOM 比较结果中排除与供应商相关的字段 - 自 26.1 起可用

版本 26.1

Altium Designer Develop – 发布日期: 2025年12月3日 – 版本 26.1.0 (build 6)

Altium Designer Agile(即将发布) – 发布日期: 2025年12月3日 – 版本 26.1.0 (build 13)

Altium Designer – 发布日期: 2025年12月3日 – 版本 26.1.0 (build 7)

PCB 设计改进

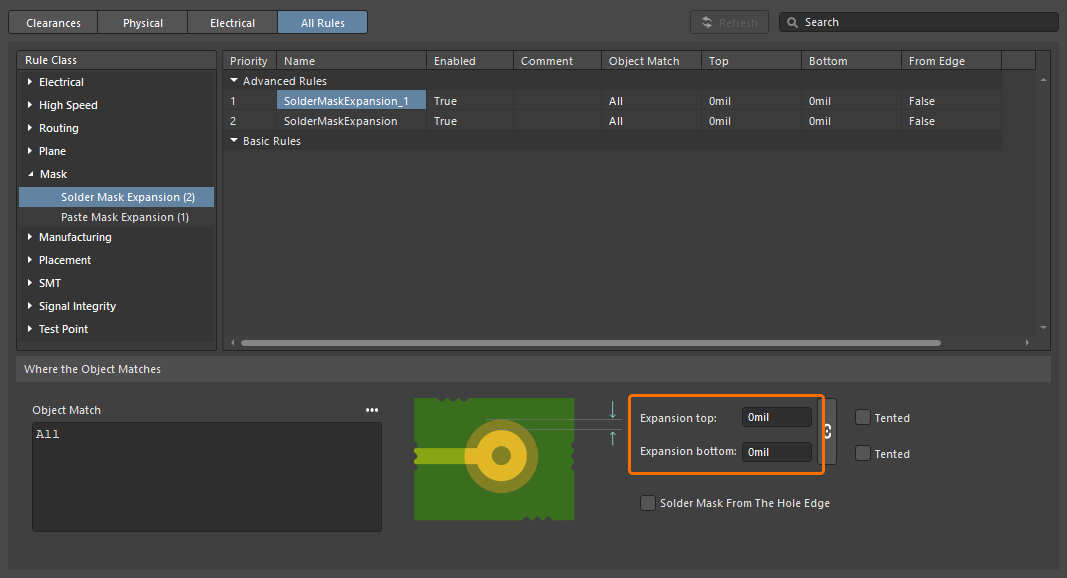

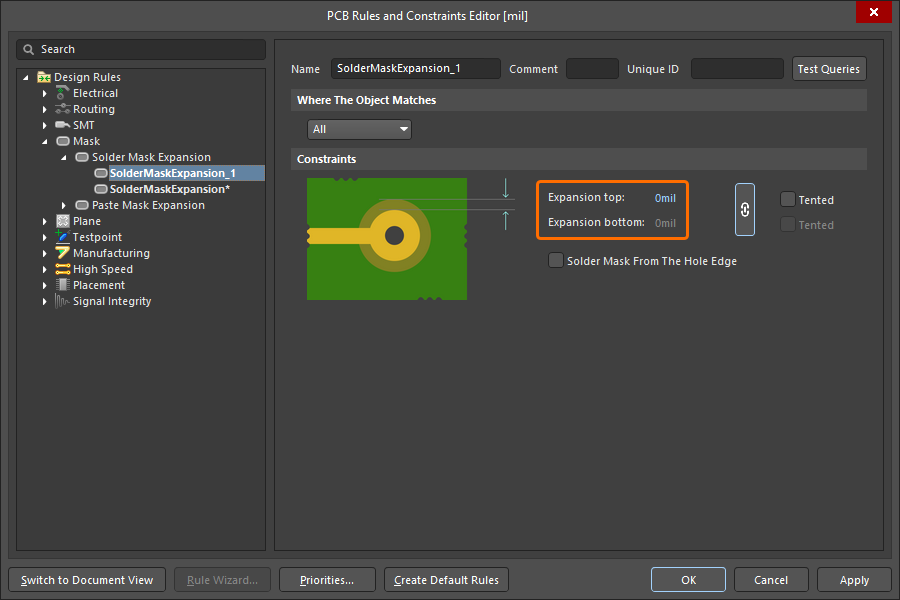

阻焊扩展规则默认值现为 0 mil(Open Beta)

遵循 IPC‑7351B 关于焊盘堆栈默认值的标准,即阻焊开窗通常与焊盘尺寸呈 1:1 关系,现将 PCB 文档中的 Solder Mask Expansion 规则以及 PCB 封装库文档中的规则驱动阻焊扩展的默认值设为 0 mil(此前为 4 mil)。

对于 PCB 封装库(*.PcbLib),新默认值在库级生效,并被该库中创建的所有元件封装继承。同一 PcbLib 在旧版 Altium Designer 中打开时,所有对象的规则驱动阻焊扩展显示为 4 mil;在本次发布及更高版本中打开则显示为 0 mil(如下以焊盘对象为例)。

对于 PCB 文档(*.PcbDoc),所有现有的 Solder Mask Expansion 规则会保留其初始值。任何新建规则的默认值由创建该规则的 Altium Designer 版本决定,跨版本打开不会改变:在旧版中创建则默认为 4 mil,在本次发布(及更高版本)中创建则默认为 0 mil(如下所示)。

在 Constraint Manager 中新建的 Solder Mask Expansion 设计规则。

在 PCB Rules and Constraints Editor 对话框中新建的 Solder Mask Expansion 设计规则。

关于 Solder Mask Expansion 设计规则的更多信息,参见 Mask Rule Types 页面。

Constraint Manager 改进

新增类过滤能力

在 Constraint Manager 的 Clearances 视图中新增了对类的过滤能力,以便在处理大量类时提升效率。你可以构建类的过滤器(或分组),以便在不同子集的间距矩阵之间切换并进行针对性操作。

点击 Clearances 视图右上角的按钮 ![]() ,打开弹窗以创建、编辑、移除并启用/禁用过滤器。

,打开弹窗以创建、编辑、移除并启用/禁用过滤器。

关于间距矩阵的更多信息,参见 Defining Design Requirements Using the Constraint Manager 页面。

Draftsman 改进

增强 DXF 导入到 Draftsman 文档(Open Beta)

新增对 R12 及更高版本 DXF 文件的导入支持,适用于制造图纸文档(*.PCBDwf, *.HarDwf, *.MbDwf);同时支持包含样条的 DXF 文件导入。

关于导入 DXF 文件的更多信息,请参见 Draftsman Placement & Editing Techniques 页面。

Wire Bonding 改进

面板中的键合线基元

键合线现以正确的类型(Bond Wire)呈现于以下位置:

-

PCB 面板的 Primitives 区域(在 Nets 模式下选中某元件时)

-

PCB 面板的 Component Primitives 区域(在 Components 模式下选中某网络时)

-

PCB Library 面板(在选中某封装时)

选择键合线基元会在设计空间内选中/高亮相应的键合线。

同时,在相关区域的右键上下文菜单中新增 Show Bond Wires 选项,用于切换键合线的显示。

关于 Wire Bonding 的更多信息,请参见 Wire Bonding 页面。

3D‑MID 设计改进

3D‑MID 设计规则检查(Open Beta)

此版本提供针对 3D 基板上布线的宽度、间距、长度和匹配长度规则违规的批量设计规则检查 (DRC)。请注意,虽然生成的 DRC 报告将提供所有这些检查的信息,但在设计空间中仅高亮显示间距 Clearance 违规。

更多信息参见 3D‑MID Design 页面。

多板设计改进

线束入口支持定义“终端类型”

现可在多板原理图上为线束入口定义 Termination Type。可选类型包括:

-

Connector – 连接到 PCB 上的配套连接器的标准选项,通常使用板载连接器。

-

Crimps/Ferrules – 单芯线先压接或套端后,再插入到 PCB 侧的连接器中。

-

Wire termination – 线束端直接剪平,然后通过螺丝或直接焊接到 PCB。这在部分 JST 直连线‑板连接中较常见。

所选终端类型会反映在该线束入口的属性以及相应模块条目的属性中。

关于在多板原理图中处理连接的更多信息,请参见 Working with Connections 页面。

线束设计改进

增强的导线同步

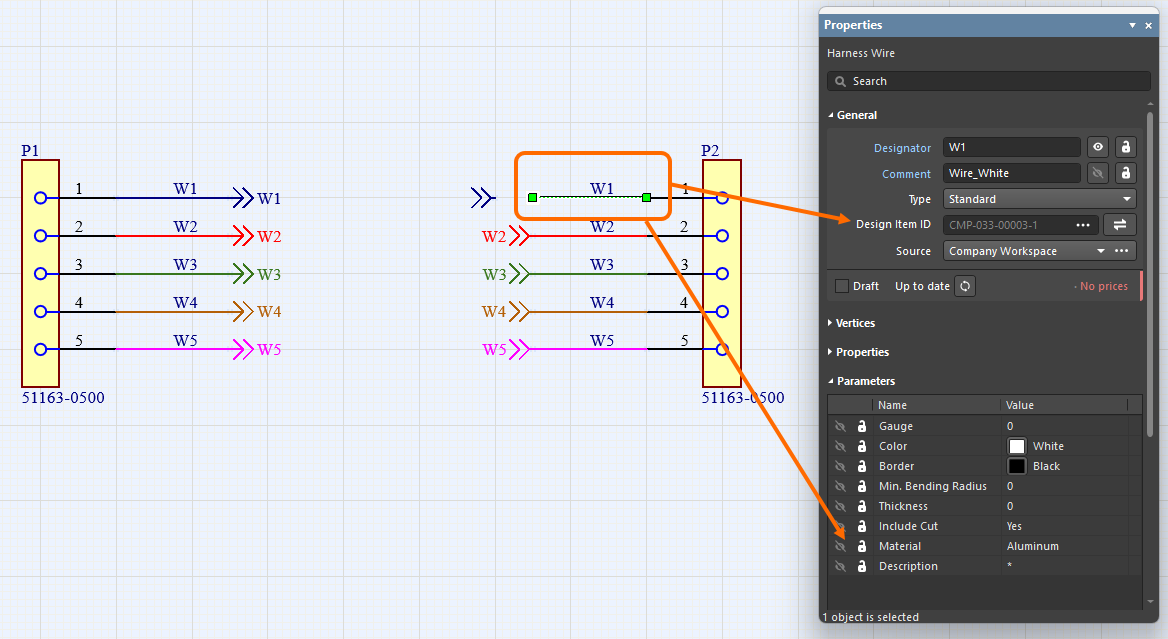

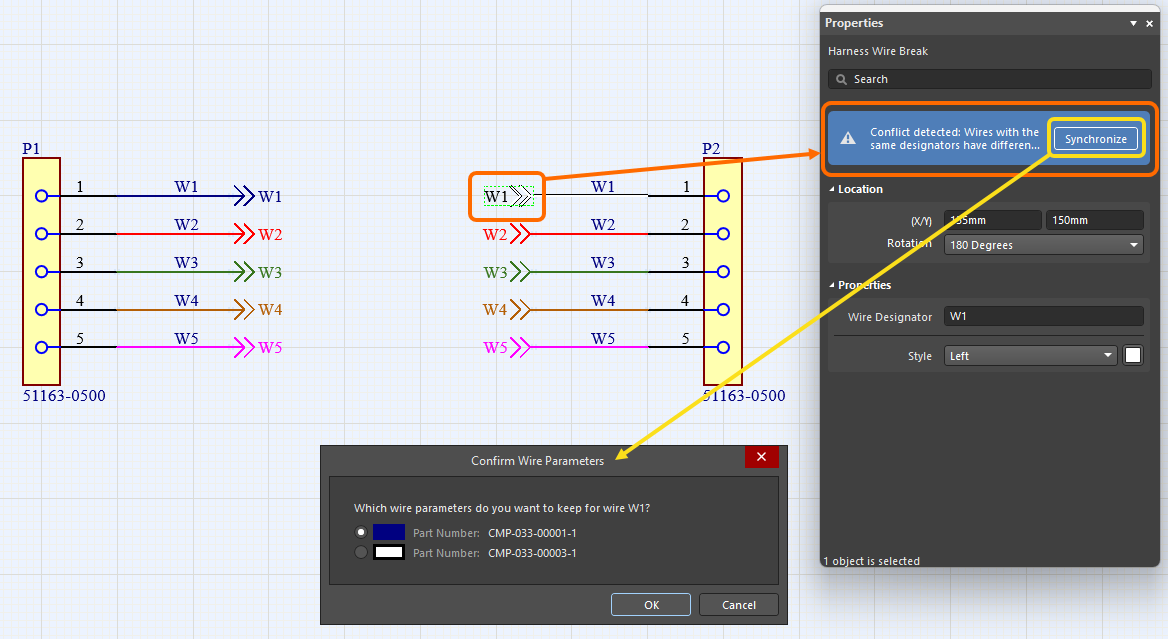

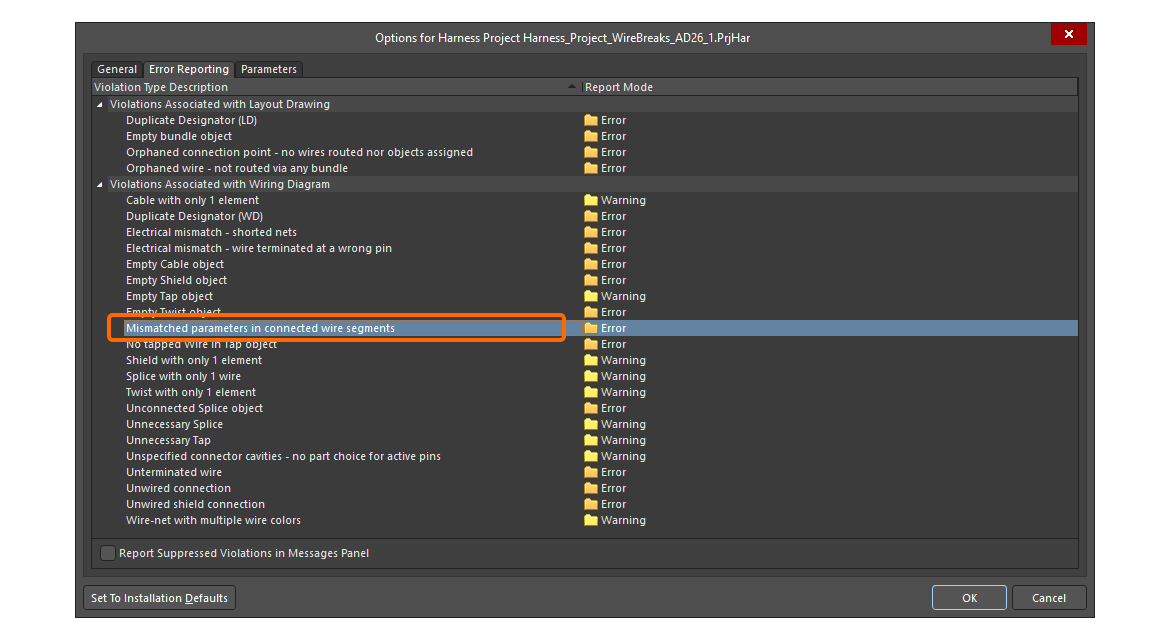

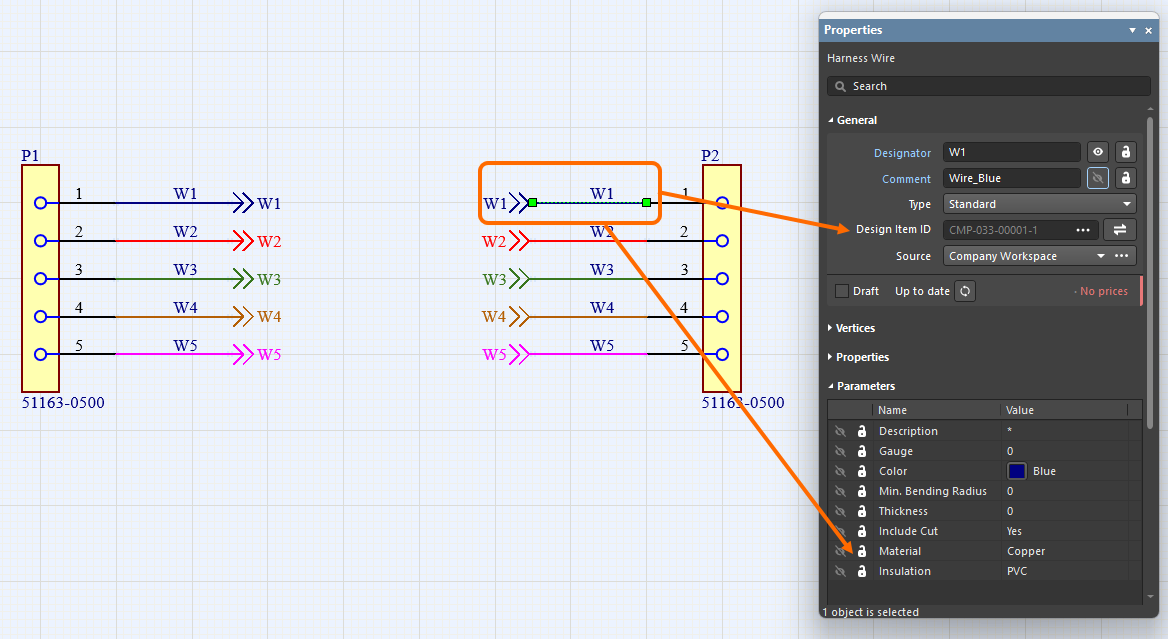

通过导线断点连接的线束导线,即使具有不同的 Design Item ID,现在也能够被识别。此外,所有由同一导线断点连接且位号相同的导线段,将被逐项比对(包含料号、注释、颜色与全部参数)。若发现差异,将报告“Mismatched parameters in connected wire segments(已连接的导线段参数不匹配)”违规。在导线与导线断点的 Properties 面板中也会出现警告,表示检测到参数冲突。点击警告中的 Synchronize 打开 Conflict Wire Parameters 对话框,你可以选择用于该导线段的参数集。

支持在汇合点上覆盖包覆件

现在可以在线束布局图纸(*.LdrDoc)中的汇合点(布局图上两个或多个线束合并处)应用或延展线束包覆。这消除了在包含多个连接器的区段中,必须在各汇合点之间分别设置多段包覆的需求。

此外,包覆的起点现在取其路径的最左上点,且该路径仅包含被该包覆覆盖的线束。

更多信息参见 Creating the Layout Drawing 页面。

BOM 中部分对象的 Quantity 字段改为 As Required

导线、线缆与线束包覆属于长度型对象,其数值显示在 Length 字段中。为避免混淆,制造图纸(*.HarDwf)中的材料清单表与 ActiveBOM 文档里,导线、线缆与线束包覆的 Quantity 字段现统一为 As Required。

更多信息参见 Managing Your Bill of Materials (BOM) with ActiveBOM 页面。

Wiring List 的引脚分组改进

在线束制造文档(*.HarDwf)中放置的 Wiring List,其引脚分组已得到改进。从本版本开始,将对拥有最多导线的连接器应用自动分组,且其所有插槽在 Wiring List 的 From 列中得到正确分组(如下图示例)。

面向线束制造商的 Excel 工作簿

通过 Output Job 现在可以生成一个单一 Excel 工作簿,其中包含供线束制造商使用的数据,为此,在 Report Outputs 部分新增了 Manufacturing Data 输出器。

生成的工作簿包含四个工作表:

-

Bill of Materials – 用于快速报价

-

Wiring List – 供线材加工设备使用

-

Labels – 线束捆绑件需打印的实体标签汇总,适用于 Zebra 等打印机

-

Coverings – 要应用到线束上的包覆件汇总

更多信息参见 Preparing Reports 页面。

平台改进

切换至 .NET 8

本次发布将 Altium Designer 从使用 .NET 6 切换到使用 .NET 8。这已作为 Altium Designer 的一部分捆绑在一起,使其能够利用 .NET 的最新功能与改进,包括整体性能增强。

更多信息参见 System Requirements 页面。

WebView2 (Open Beta)

从本版本起,Altium Designer 在浏览相关元素(如 Home 页面)上改用 WebView2。只需更新 Windows,即可在 Altium Designer 中获得最新的浏览器引擎。

数据管理改进

支持通过流程工作流复制工作区项目

新增通过已定义并启用的流程工作流复制工作区项目的能力。打开某工作区项目后,在 Projects 面板中右键点击该项目,选择 Project Creations 主题下的已激活流程定义,在“Make a copy of the managed project”子菜单中启动项目复制,系统将按该流程的底层工作流执行。

更多信息参见 Process‑based Project Creation 页面。

新增在发布模型新修订时保留生命周期状态

当把元件模型(原理图符号、PCB 封装、仿真模型或线束接线)发布为新修订至所连接的工作区时,现可保留该模型的当前生命周期状态。

该能力适用于拥有“Allow to skip lifecycle state change for new revisions”操作权限的用户。了解更多请参见 Setting Global Operation Permissions for a Workspace。

更多关于编辑工作区内容的信息,参见 Creating & Editing Content 页面。

设计评审评论链接

当在设计评审中添加评论时,Comments And Tasks 面板及设计空间中的上下文评论窗口中,将在对应评论条目显示指向该评审的链接(From <DesignReviewName>)。点击该链接,将在默认浏览器的新标签页打开该评审的 Overview 页面。

更多关于文档评论的信息,参见 Document Commenting 页面。

新增更多单位感知数据类型

在 Altium 平台的连接工作区中,作为元件模板的一部分定义用户参数时,现支持以下新增的单位感知数据类型:

-

面积 Area (mm2)

-

压力 Bar (bar)

-

位 Bit

-

发光强度 Candela (cd)

-

十进制数 Decimal

-

整数 Integer

-

能量 Joule (J)

-

光通量 Lumen (lm)

-

长度 Millimetre (mm)

-

压力 Pascal (Pa)

-

压力 Pounds per square inch (psi)

-

转速 Rotations per minute (rpm)

-

电导 Siemens (S)

-

磁通密度 Tesla (T)

使用这些单位类型的参数已在软件多处得到支持,包括 Components 面板、元件编辑器(单项与批量编辑)、Library Importer,以及 Components Synchronization 功能(在 Properties 面板的 Parameter Mapping 区域)。

更多关于单位感知的元件参数类型,参见 Component Templates 页面。

元件同步时支持同步器件选择

现可通过元件同步功能及其关联的元件同步配置文档(*.CmpSync)定义并同步器件选择信息。在文档中选中某个表格后,可在 Properties 面板的 Part Choices Mapping 区域控制同步的参数。使用按钮添加或移除器件选择参数对(Manufacturer / Part Number),并通过下拉菜单定义映射关系。当映射被定义后,相应参数会出现在文档表格区域的 Part Choice n 列中。

有关元件同步功能的更多信息,参见 Component Database to Workspace Data Synchronization 页面。

连接工作区问题的新增警告

当连接工作区出现问题,导致项目文档的最新 VCS 状态无法刷新时,Projects 面板的项目条目旁将出现 Refresh VCS Statuses 控件及相应的工具提示警告。连接恢复后,点击该控件即可使 VCS 状态重新同步,并查看最新更改。

有关文档状态指示的更多信息,参见 Managing Project Documents 页面。

BOM CoDesign 改进

在比较结果中排除供应商相关字段(Open Beta)

使用 BOM CoDesign 功能,从 ActiveBOM 文档访问 Properties 面板的 Related BOMs 选项卡并比较一个 ActiveBOM 与选定的 Managed BOM 时,当高级设置被禁用,供应商相关数据(Supplier 与 Supplier Part Number 参数)将被排除在 Differences 区域之外。

关于探索比较结果的更多信息,请参见 BOM CoDesign 页面。

导入/导出改进

增强 Allegro 设计导入

现已将所有所需的配置文件合并到 Allegro2Altium.bat 批处理文件中(随 Altium Designer 安装提供),用于在设计或库不与 Altium Designer 位于同一台电脑时,将 Allegro 二进制文件(*.brd或 *.dra)转换为 ASCII 格式。因此,导入仅需 bat 文件,无需其他文件。

更多信息参见 Importing a Design from Allegro 页面。

支持从 xDX Designer 设计导入的元件替代视图

在导入 xDX Designer 设计时,现已在生成的原理图与原理图库文档中支持元件的替代视图模式。

更多信息参见 Importing a Design from xDX Designer or DxDesigner 页面。

在 Altium Designer 26.1 中正式公开的功能

以下功能已在本次发布中正式对外公开:

-

Allegro 导入的详细焊盘堆栈 - 自版本 25.7 可用

-

Properties 面板的 PCB 对象属性优化 - 自版本 25.7 可用

Altium Designer 26.1 的其他功能

-

隐藏外部 VCS 存储库链接(Open Beta):在 Advanced Settings 对话框中新增

VCS.HideProjectExternalRepositoriesLinks选项。启用后,将在 Preferences 对话框( )的 Data Management – Design Repositories 页面隐藏指向外部 VCS 存储库的链接(这些链接是在将外部 VCS 下的项目可用到连接的工作区时自动创建的)。

)的 Data Management – Design Repositories 页面隐藏指向外部 VCS 存储库的链接(这些链接是在将外部 VCS 下的项目可用到连接的工作区时自动创建的)。

-

Simbeor 版本(Open Beta):在 Advanced Settings 对话框中新增

PCB.SimbeorVersion选项。该功能用于控制计算延迟与阻抗时所用的 Simbeor 版本(Simbeor 2020.3,选项值为 0;或 Simbeor 2023.1,选项值为 1)。 -

过孔实例化(Open Beta):在 Advanced Settings 对话框中新增

PCB.ViaInstancing选项。启用后将采用“过孔实例化”的概念,即构建过孔实例的几何而非过孔模板,以提升性能并减少内存占用与场景构建时间。 -

焊盘与过孔模板的加载优化(Open Beta):在 Advanced Settings 对话框中新增

PCB.Performance.PadViaTemplate.LoadingOptimization选项,通过优化焊盘与过孔模板的加载加速 PCB 打开速度。 -

ECO 处理优化(Open Beta):在 Advanced Settings 对话框中新增

WSM.DotNetECOImplementation选项,启用后将使用加速的 ECO 处理功能。