Routing Rule Types

Routing 카테고리의 설계 규칙은 아래에 설명되어 있습니다.

Width

기본 규칙: 필수

이 규칙은 구리(신호) 레이어에 배치되는 트랙의 폭을 정의합니다.

Constraints

모든 레이어에 적용되는 Width 규칙의 제약 조건입니다. 레이어별 값은 그리드에 입력하십시오(표시하려면 커서를 올리십시오).

-

Preferred Width - 보드 라우팅 시 트랙에 사용할 권장 폭을 지정합니다.

-

Min Width - 보드 라우팅 시 트랙에 사용할 수 있는 최소 허용 폭을 지정합니다.

-

Max Width - 보드 라우팅 시 트랙에 사용할 수 있는 최대 허용 폭을 지정합니다.

-

Check Tracks/Arcs Min/Max Width Individually 에 대해 자세히 알아보기

-

Check Tracks/Arcs Min/Max Width Individually – 규칙이 대상으로 하는 넷의 각 라우트에 대해, 각 개별 트랙 및 아크의 폭이 최소 및 최대 범위 내에 있는지 확인합니다.

-

Check Min/Max Width for Physically Connected – 규칙이 대상으로 하는 넷의 각 라우트에 대해, 트랙, 아크, 필, 패드 및 비아의 조합으로 형성된 실제 라우팅 구리의 폭이 최소 및 최대 범위 내에 있는지 확인합니다.

-

Use Impedance Profile - 이 옵션은 Layer Stack Manager에 임피던스 프로파일이 하나 이상 정의되어 있을 때 사용할 수 있습니다. 활성화하면 드롭다운을 사용하여 원하는 임피던스 프로파일을 선택합니다. 이 모드로 규칙을 구성하면 각 라우팅 레이어에 필요한 Preferred Width가 지정된 임피던스 프로파일의 일부로 계산됩니다(옵션이 활성화되면 Min Width 및 Max Width 값도 이 값으로 설정됨). 규칙이 정의된 후, 규칙 범위에 속하는 넷을 라우팅하면 해당 레이어에서 지정된 임피던스를 충족하는 데 필요한 폭으로 트랙 폭이 자동 설정됩니다. 이 옵션이 활성화되면 규칙에서 Preferred Width는 편집할 수 없지만 Min Width 및 Max Width 값은 편집할 수 있습니다.

► Configuring the Layer Stack for Controlled Impedance Routing

-

Show values for layer stack 에 대해 자세히 알아보기

-

Show values for layer stack – 이 옵션은 Layer Stack Manager에 여러 레이어 스택이 정의되어 있을 때 대화상자에 표시됩니다. 보드에 여러 레이어 스택이 포함된 경우 Width Constraints는 이미지 위의 전체 레이어 필드 또는 Layer Attributes Table의 레이어별 필드를 사용하여 각 스택별로 구성해야 합니다.

► Defining and Configuring Substacks

설계의 각 레이어 스택에 대한 Constraints를 구성합니다.

-

Layer Attributes Table - 대화상자 하단의 그리드 영역에는 Use Impedance Profile 옵션이 활성화되지 않은 한 레이어 스택에 정의된 모든 신호 레이어가 표시됩니다. 이 옵션이 활성화되면 선택한 임피던스 프로파일의 일부로 사용 가능한 레이어만 표시됩니다. 최소, 최대, 권장 라우팅 폭 및 기타 레이어별 정보가 표시됩니다. 라우팅 폭 필드는 이미지 위의 제약 조건 필드에서 값을 정의하여 전역으로 설정하거나, 표에 직접 값을 입력하여 개별적으로 설정할 수 있습니다. Use Impedance Profile 옵션이 활성화되면 필요한 폭 항목이 자동으로 계산되어 표의 각 레이어에 입력됩니다. 이 모드에서는 Preferred Width 값은 편집할 수 없지만 Min Width 및 Max Width 값은 편집할 수 있습니다.

Rule Application

Preferred Width 설정은 Autorouter가 따릅니다.

Min Width 및 Max Width 설정은 Online DRC와 Batch DRC가 따릅니다. 또한 대화형 라우팅 중 사용할 수 있는 허용 값 범위를 결정합니다(라우팅 중 Tab 키를 눌러 Properties panel을 통해 정의된 범위 내에서 트레이스 폭을 변경할 수 있습니다). 이 범위를 벗어난 값을 입력하면 자동으로 제한됩니다.

Note

차동 페어의 각 넷 폭은 해당 Differential Pairs Routing rule에 의해 모니터링됩니다.

Routing Neck-Down

기본 규칙: 필요하지 않음

보드 전체를 따라 라우팅이 진행되는 동안 하나의 넷이 서로 다른 폭으로 라우팅되는 경우는 드물지 않습니다. 예를 들어 BGA 안으로 또는 밖으로 라우팅할 때는 적용된 임피던스 프로파일에서 허용하는 권장 폭 라우트보다 더 좁은 이스케이프 라우트가 필요한 경우가 많습니다. 이 규칙을 사용하면 이러한 더 좁은 트레이스의 총 허용 최대 길이를 정의하여 라우트가 여전히 필요한 임피던스를 제공하도록 할 수 있습니다.

이 규칙은 Constraint Manager의 Physical 보기와 PCB Rules and Constraints Editor 대화상자 모두에서 정의할 수 있습니다.

Constraints

Routing Neck-Down 규칙의 제약 조건

Neck-Down Length 은(는) 해당 Routing Width 규칙에 의해 정의된 Min Width 와 Preferred Width 사이 폭을 갖는 연속 라우트(규칙 범위에 포함되는 각 넷에서)의 최대 허용 길이를 지정합니다. 또는 그리드를 사용하여 레이어별 허용 길이를 정의할 수 있습니다.

Rule Application

해당 DRC 모드에서 Routing Neck-Down 규칙 위반을 감지하려면 Design Rule Checker 대화상자에서 온라인 및/또는 배치 검사에 대해 Routing Neck-Down 규칙 유형 검사를 활성화하십시오. 감지된 규칙 위반은 설계 공간의 해당 트레이스에 해치 패턴으로 표시됩니다.

Routing Topology

기본 규칙: 필수

이 규칙은 보드에서 넷을 라우팅할 때 사용할 토폴로지를 지정합니다. 넷의 토폴로지는 핀 간 연결의 배열 또는 패턴입니다. 기본적으로 각 넷의 핀 간 연결은 전체 연결 길이가 가장 짧아지도록 배열됩니다. 토폴로지는 여러 이유로 넷에 적용됩니다. 신호 반사를 최소화해야 하는 고속 설계에서는 넷을 데이지 체인 토폴로지로 배열하고, 접지 넷에는 모든 트랙이 공통 지점으로 돌아오도록 스타 토폴로지를 적용할 수 있습니다.

Constraints

Routing Topology 규칙의 기본 제약 조건

Topology - 규칙의 범위(전체 쿼리)가 대상으로 하는 넷에 사용할 토폴로지를 정의합니다. 다음 토폴로지를 적용할 수 있습니다.

-

Shortest- 이 토폴로지는 넷의 모든 노드를 연결하여 전체 연결 길이가 가장 짧아지도록 합니다. -

Horizontal- 이 토폴로지는 모든 노드를 함께 연결하되, 수직 방향의 짧음을 5:1 비율로 희생하고 수평 방향의 짧음을 우선합니다. 이 방법을 사용하여 수평 방향 라우팅을 강제할 수 있습니다. -

Vertical- 이 토폴로지는 모든 노드를 함께 연결하되, 수평 방향의 짧음을 5:1 비율로 희생하고 수직 방향의 짧음을 우선합니다. 이 방법을 사용하여 수직 방향 라우팅을 강제할 수 있습니다. -

Daisy-Simple- 이 토폴로지는 모든 노드를 하나씩 차례대로 체인으로 연결합니다. 체인 순서는 전체 길이가 가장 짧아지도록 계산됩니다. 소스 및 종단 패드가 지정된 경우 다른 모든 패드는 그 사이에 체인으로 연결되어 가능한 한 가장 짧은 길이가 되도록 합니다. 패드를 편집하여 소스 또는 종단으로 설정할 수 있습니다. 여러 소스(또는 종단)가 지정된 경우 각 끝에서 함께 체인으로 연결됩니다. -

Daisy-MidDriven- 이 토폴로지는 소스 노드를 데이지 체인의 중앙에 배치하고, 부하를 균등하게 나눈 다음 소스의 양쪽으로 체인 연결합니다. 각 끝에 하나씩, 두 개의 종단이 필요합니다. 여러 소스 노드는 중앙에서 함께 체인으로 연결됩니다. 종단이 정확히 두 개가 아니면Daisy-Simple토폴로지가 사용됩니다. -

Daisy-Balanced- 이 토폴로지는 모든 부하를 동일한 체인으로 나누며, 전체 체인 수는 종단 수와 같습니다. 그런 다음 이 체인들은 스타 패턴으로 소스에 연결됩니다. 여러 소스 노드는 함께 체인으로 연결됩니다. -

Starburst- 이 토폴로지는 각 노드를 소스 노드에 직접 연결합니다. 터미네이터가 있는 경우 각 부하 노드 뒤에 연결됩니다. 여러 소스 노드는Daisy-Balanced토폴로지에서와 같이 체인 형태로 연결됩니다.

규칙 적용

자동 배선 중 Batch DRC.

참고

-

Autorouter를 사용할 때

Shortest이외의 토폴로지를 사용하면 배선 완료 시간이 더 길어질 수 있습니다. -

From-Tos를 사용해 정의한 사용자 지정 토폴로지의 구현은 해당 넷에 적용된 Routing Topology 설계 규칙의 Batch DRC 중에 검사할 수 있습니다. From-To의 패드들 사이에 전기적 연결이 있고 최단 경로에 이 넷의 다른 패드가 하나 이상 포함되어 있으면 위반이 감지됩니다. 패드 수가 많거나(20개 초과) 프리미티브 수가 많은(1024개 초과) 넷에 대해서는 위반이 감지되지 않습니다.

배선 우선순위

기본 규칙: 필수

이 규칙은 규칙의 대상이 되는 넷에 배선 우선순위를 할당합니다. Autorouter는 할당된 우선순위 값을 사용해 설계 내 각 넷의 배선 중요도를 판단하고, 그에 따라 어떤 넷을 먼저 배선할지 결정합니다.

제약조건

Routing Priority 규칙의 기본 제약조건

Routing Priority - 규칙의 범위(전체 쿼리)가 대상으로 하는 넷에 할당되는 우선순위 값입니다. 0와 100 사이의 값을 입력하십시오. 숫자가 클수록 배선 시 우선순위가 높아집니다.

규칙 적용

자동 배선 중.

배선 레이어

기본 규칙: 필수

이 규칙은 배선에 사용할 수 있는 레이어를 지정합니다.

제약조건

Routing Layers 규칙의 기본 제약조건

Enabled Layers - 레이어 스택업에 정의된 현재 설계의 각 신호 레이어가 나열됩니다. 필요에 따라 연결된 Allow Routing 옵션을 사용하여 레이어별 배선을 활성화/비활성화하십시오.

규칙 적용

Online DRC, Batch DRC, 대화형 배선 중, 그리고 자동 배선 중.

참고

Autorouter를 사용할 때 설계에서 활성화된 각 신호 레이어의 배선 방향은 Situs Autorouter 설정의 일부로 정의됩니다. 방향은 Edit Layer Directions 버튼을 클릭해 접근하는 Situs Routing Strategies dialog의 Layer Directions dialog에서 지정합니다.

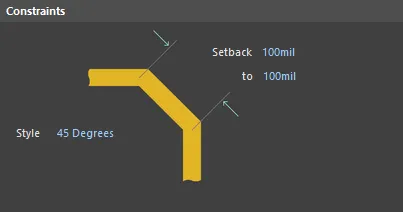

배선 코너

기본 규칙: 필수

이 규칙은 자동 배선 중 사용할 코너 스타일을 지정합니다.

제약조건

Routing Corners 규칙의 기본 제약조건

-

Style - 사용할 배선 코너 스타일을 지정합니다. 다음 세 가지 스타일을 사용할 수 있습니다:

-

90 Degrees. -

45 Degrees. -

Rounded.

-

-

Setback - 이 두 필드는

45 Degrees및Rounded코너 스타일을 사용할 때 setback의 최소값과 최대값을 정의할 수 있게 합니다. setback은 '실제' 코너 위치(90 Degrees스타일을 사용할 경우 존재하는 위치)에서 Autorouter가 챔퍼 처리 또는 라운딩을 시작해야 하는 지점까지의 거리로, 결과적으로 마이터 크기 또는 코너 반경을 제어합니다.

규칙 적용

이 규칙은 45° 배선을 후처리로 구현하는 타사 Autorouter에서 사용하도록 의도되었습니다. 45° 배선을 네이티브 프로세스로 구현하는 Situs Autorouter에서는 이 규칙을 따르지 않습니다.

배선 비아 스타일

기본 규칙: 필수

이 규칙은 배선 시 사용할 수 있는 비아 스타일을 지정합니다. 규칙의 제약조건 일부로 정의되는 비아의 직경 및 홀 크기에 대해 특정 최소/최대/선호 값을 정의하거나, 보드 설계에서 사용할 수 있는 템플릿을 사용할 수 있습니다.

제약조건

Routing Via Style 규칙의 기본 제약조건. 이미지를 가리키면 사용 가능한 두 가지 모드를 비교할 수 있습니다.

Mode - 드롭다운을 사용하여 다음 두 가지 모드 중에서 선택합니다:

- Min/Max preferred - 이 모드를 선택하면 규칙 자체에서 비아의 직경 및 홀 크기에 대한 허용값(최소/최대/선호)을 설정할 수 있습니다.

- Template preferred - 이 모드를 선택하면 보드에서 사용할 수 있는 비아 템플릿을 통해 정의된 비아 스타일을 사용할 수 있습니다.

Mode = Min/Max preferred

이 모드를 선택하면 제약조건 영역이 다음 옵션을 표시하도록 변경됩니다:

-

Via Diameter - 보드 배선 시 배치되는 비아의 직경과 관련하여 준수해야 할 제약 범위 값을 지정합니다. 다음 개별 값을 정의할 수 있습니다:

- Minimum - 비아 직경의 허용 최소값입니다.

- Maximum - 비아 직경의 허용 최대값입니다.

- Preferred - 비아 직경의 선호값입니다.

-

Via Hole Size - 보드 배선 시 배치되는 비아의 홀 크기와 관련하여 준수해야 할 제약 범위 값을 지정합니다. 다음 개별 값을 정의할 수 있습니다:

- Minimum - 비아 홀 크기의 허용 최소값입니다.

- Maximum - 비아 홀 크기의 허용 최대값입니다.

- Preferred - 비아 홀 크기의 선호값입니다.

Mode = Template preferred

이 모드를 선택하면 제약조건 영역이 다음 옵션을 표시하도록 변경됩니다:

-

Templates List - 규칙과 함께 사용할 수 있는 비아 템플릿 목록입니다. 이는 Local Pad & Via Library의 일부로 보드 설계에서 사용할 수 있게 된 비아 템플릿(로컬 또는 Pad Via Template Libraries에 정의된 것)입니다(PCB Pad Via Templates 패널을 통해 접근). 사용 가능한 각 템플릿에 대해 다음 정보가 표시됩니다:

- Template Name - 템플릿의 읽기 전용 이름입니다. 로컬 템플릿의 경우 IPC 표준을 준수하는 자동 생성 이름이 사용됩니다. PvLib에서 가져온 템플릿의 경우 이 이름은 해당 라이브러리 내 템플릿 구성의 일부로 사용자 지정할 수 있습니다.

- Description - 템플릿에 대해 작성된 읽기 전용 설명입니다.

- Library - 템플릿이 제공되는 라이브러리입니다. 이는 <Local>(비아가 PCB 문서와 함께 정의 및 저장되는 경우) 또는 PCB 문서에서 사용할 수 있게 된 외부 Pad Via Template Library(<LibraryName>.PvLib)의 이름일 수 있습니다.

- Enabled - 이 옵션을 활성화하면 대화형 배선 중 비아 배치에 해당 템플릿을 사용할 수 있습니다.

규칙 적용

Online DRC, Batch DRC, 자동 배선 중, 그리고 대화형 배선 중.

규칙의 모드가 Min/Max preferred로 설정된 경우 다음 사항이 적용됩니다:

- The Preferred 비아 속성은 Autorouter에서 사용됩니다.

- The Minimum 및 Maximum 비아 속성은 Online DRC와 Batch DRC에서 준수됩니다.

- The Maximum and Minimum 비아 속성은 대화형 배선 중 사용할 수 있는 허용값 범위도 결정합니다. 즉, 숫자 키패드에서 +(또는 *) 키를 눌러 배선 신호 레이어를 전환하고 비아를 드롭할 때, 숫자 키패드에서 / 키를 눌러 팬아웃 비아를 배치할 때, 또는 레이어를 변경하지 않고 비아를 배치하기 위해 2 단축키를 누를 때 적용됩니다.

- 대화형 배선 중 배선 비아를 배치하려고 할 때 4 키를 눌러 Minimum / Preferred / Maximum / User Choice 비아 정의를 순환할 수 있습니다. 현재 선택된 상태는 Heads-Up Display와 상태 표시줄에 표시됩니다. 또한 배선 중 Tab 키를 눌러 Properties panel에 접근할 수 있으며, 여기서 Min/Max 규칙 범위 내에서 비아 속성을 편집할 수 있습니다. 범위를 벗어난 값을 입력하면 자동으로 제한됩니다.

-

Layer Stack Manager에 여러 Via Type(예: 스루홀 및 블라인드/버리드 비아)이 정의되어 있으면 현재 레이어 전환에 서로 다른 Via Type을 사용할 수 있습니다. 이 경우 6 키를 눌러 허용된 Via Type을 순환할 수 있습니다. 선택된 Via Type은 Heads-Up Display 및 상태 표시줄에 표시됩니다. 또는 8 키를 눌러 허용된 Via Type의 팝업 메뉴를 표시한 다음 필요한 항목을 클릭할 수 있습니다.

규칙의 모드가 Template preferred로 설정된 경우 다음 사항이 적용됩니다:

- 대화형 배선 중 배선 비아를 배치하려고 할 때 4 키를 눌러 활성화된 비아 템플릿을 순환할 수 있습니다. 선택된 템플릿은 Heads-Up Display와 상태 표시줄에 표시됩니다. 또한 배선 중 Tab 키를 눌러 Properties panel에 접근할 수 있으며, 여기서 현재 적용된 비아 템플릿을 변경할 수 있습니다.

- Layer Stack Manager에 여러 Via Type(예: thruhole, blind/buried vias)이 정의되어 있으면, 현재 레이어 전환에 서로 다른 Via Type을 사용할 수 있습니다. 이런 경우 허용된 Via Type 사이를 순환하려면 6 키를 누르십시오. 선택된 Via Type은 Heads-Up Display와 Status bar에 표시됩니다. 또는 8 키를 눌러 허용된 Via Type의 팝업 메뉴를 표시한 다음, 필요한 항목을 클릭할 수 있습니다.

참고

블라인드 및 버리드 비아의 크기를 제어하려면 서로 다른 레이어 페어를 대상으로 하는 개별 규칙을 설정할 수 있습니다. 예를 들어, top layer와 mid-layer 1 사이의 블라인드 비아 크기를 제어하려면 다음 범위(Full Query)를 사용할 수 있습니다.

(StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')

mid-layer 2와 mid-layer 3 사이의 버리드 비아 크기를 제어하려면 다음 범위를 사용합니다.

(StartLayer = 'Mid-Layer2') and (StopLayer = 'Mid-Layer3')

또는 개별 규칙을 만드는 대신, 다음과 같이 OR를 사용하여 하나의 규칙 쿼리를 확장할 수 있습니다.

((StartLayer = 'Top Layer') and (StopLayer = 'Mid-Layer1')) or((StartLayer = ' Mid-Layer2') and (StopLayer = 'Mid-Layer3'))

Fanout 제어

기본 규칙: 필요

이 규칙은 설계에서 signal 및/또는 power plane net에 연결되는 표면실장 부품의 패드를 fanout할 때 사용할 fanout 옵션을 지정합니다. Fanout은 비아와 연결 트랙을 추가하여, 라우팅 관점에서 SMT 패드를 사실상 스루홀 패드로 바꿉니다. 이렇게 하면 신호를 top 또는 bottom layer에만 국한하지 않고 모든 라우팅 레이어에서 사용할 수 있게 되어 보드 라우팅 성공 가능성이 크게 높아집니다. 이는 특히 라우팅 공간이 매우 제한적인 고밀도 설계에서 필요합니다.

제약조건

Fanout Control 규칙의 기본 제약조건(Fanout_Default)

-

Fanout Style - SMT 부품에 대해 fanout 비아를 어떻게 배치할지 지정합니다. 다음 옵션을 사용할 수 있습니다.

-

Auto- 최적의 라우팅 공간 결과를 얻기 위해 부품 기술에 가장 적합한 스타일을 선택합니다. -

Inline Rows- fanout 비아를 정렬된 두 개의 행 안에 배치합니다. -

Staggered Rows- fanout 비아를 엇갈린 두 개의 행 안에 배치합니다. -

BGA- 지정된 BGA 옵션에 따라 fanout을 수행합니다. -

Under Pads- fanout 비아를 SMT 부품 패드 바로 아래에 배치합니다.

-

-

Fanout Direction - fanout에 사용할 방향을 지정합니다. 다음 옵션을 사용할 수 있습니다.

-

Disable- 이 규칙이 대상으로 하는 SMT 부품에 대해서는 fanout을 허용하지 않습니다. -

In Only- 안쪽 방향으로만 fanout합니다. 모든 fanout 비아와 연결 트랙은 부품의 bounding rectangle 내부에 배치됩니다. -

Out Only- 바깥쪽 방향으로만 fanout합니다. 모든 fanout 비아와 연결 트랙은 부품의 bounding rectangle 외부에 배치됩니다. -

In Then Out- 먼저 모든 부품 패드를 안쪽 방향으로 fanout합니다. 이 방향으로 fanout할 수 없는 패드는 (가능한 경우) 바깥쪽 방향으로 fanout해야 합니다. -

Out Then In- 먼저 모든 부품 패드를 바깥쪽 방향으로 fanout합니다. 이 방향으로 fanout할 수 없는 패드는 (가능한 경우) 안쪽 방향으로 fanout해야 합니다. -

Alternating In and Out- 모든 부품 패드를 (가능한 경우) 번갈아가며, 먼저 안쪽 그다음 바깥쪽 방향으로 fanout합니다.

-

-

Direction From Pad - fanout에 사용할 방향을 지정합니다. BGA 부품을 fanout할 때는 패드를 사분면으로 나누고, 각 사분면의 패드에 동시에 fanout을 적용합니다. 다음 옵션을 사용할 수 있습니다.

-

Away From Center- 각 사분면의 패드 fanout은 부품 중심에서 바깥쪽으로 향하는 45° 각도를 따라 적용됩니다. -

North-East- 각 사분면의 모든 패드를 북동 방향(수평선에서 반시계 방향으로 45°)으로 fanout합니다. -

South-East- 각 사분면의 모든 패드를 남동 방향(수평선에서 시계 방향으로 45°)으로 fanout합니다. -

South-West- 각 사분면의 모든 패드를 남서 방향(수평선에서 시계 방향으로 135°)으로 fanout합니다. -

North-West- 각 사분면의 모든 패드를 북서 방향(수평선에서 반시계 방향으로 135°)으로 fanout합니다. -

Towards Center- 각 사분면의 패드 fanout은 부품 중심을 향하는 45° 각도를 따라 적용됩니다. 대부분의 경우, 다른 패드의 fanout 비아가 이미 필요한 fanout 공간을 차지하고 있기 때문에 방향의 균일성을 유지할 수 없습니다. 이런 경우 fanout은 다음으로 가능한 방향(북동, 남동, 남서, 북서)으로 수행됩니다.

-

-

Via Placement Mode - BGA 부품의 패드에 대해 fanout 비아를 어떻게 배치할지 지정합니다. 다음 옵션을 사용할 수 있습니다.

-

Close To Pad (Follow Rules)- 정의된 clearance 규칙을 위반하지 않는 범위에서 fanout 비아를 해당 SMT 부품 패드에 최대한 가깝게 배치합니다. -

Centered Between Pads- fanout 비아를 SMT 부품 패드 사이의 중앙에 배치합니다.

-

규칙 적용

대화형 라우팅 및 자동 라우팅 중.

참고

-

다음 기본 Fanout Control 설계 규칙은 일반적으로 사용 가능한 부품 패키지 유형을 포괄하도록 자동 생성됩니다(우선순위 높은 순으로 나열). 이러한 규칙은 편집할 수 있으며, 개별 설계 요구사항에 맞게 다른 규칙을 정의할 수도 있습니다.

-

Fanout_BGA – 쿼리는

IsBGA. -

Fanout_LCC - 쿼리는

IsLCC. -

Fanout_SOIC - 쿼리는

IsSOIC. -

Fanout_Small - 쿼리는

(CompPinCount < 5). -

Fanout_Default - 쿼리는

All.

-

Fanout_BGA – 쿼리는

-

fanout 비아에 사용되는 스타일은 적용 가능한 Routing Via Style 설계 규칙을 따릅니다. fanout 과정에서 패드에서 비아까지 추가로 배치되는 트랙은 적용 가능한 Routing Width 설계 규칙을 따릅니다.

-

부품의 패드를 fanout하려면, 어떤 레이어에서도 해당 부품 아래에 polygon pour가 없도록 하십시오. Fanout을 생성하기 전에 polygon을 shelve하고 afterward 복원할 수 있습니다.

와이어 본딩

기본 규칙: 필요하지 않음

이 규칙은 Wire Bonding이 포함된 설계와 관련된 제약조건을 정의합니다.

Constraints

- Wire To Wire – 인접한 bond wire의 3D body 사이에 허용되는 최소 거리를 지정합니다.

- Min Wire Length – bond wire의 허용 가능한 최소 길이를 지정합니다.

- Max Wire Length – bond wire의 허용 가능한 최소 길이를 지정합니다.

- Bond Finger Margin – bond finger pad 가장자리로부터 허용되는 최소 여유를 지정합니다.

Rule Application

배치 DRC

차동 페어 라우팅

기본 규칙: 필요

이 규칙은 차동 페어의 각 net에 대한 라우팅 폭과 해당 페어 내 net 사이의 clearance(또는 gap)를 정의합니다. 차동 페어는 일반적으로 해당 net pair에 필요한 차동 임피던스를 제공하기 위해 특정 width-gap 설정으로 라우팅됩니다.

Differential Pair Routing

제약조건

- Min WidthDifferential Pairs Routing 규칙의 기본 제약조건

- Min Gap - 차동 페어를 라우팅할 때 트랙에 사용할 수 있는 최소 허용 폭을 지정합니다.

- Min Gap - 라우팅 중 동일한 차동 페어 내 서로 다른 net의 primitive 사이에 허용되는 최소 clearance를 지정합니다. 이 설계 규칙의 Min, Preferred & Max Gap 설정은 차동 페어를 라우팅, 재라우팅 또는 대화형 수정(Interactive Sliding 중)할 때 사용됩니다. 이러한 Gap 설정은 규칙 검사(DRC) 중에는 NOT 사용되지 않습니다. DRC 중 Gap은 적용 가능한 Clearance Constraint 규칙으로 검사됩니다. 이에 대한 자세한 내용은 아래의 Notes를 참조하십시오.

- Preferred Width - 차동 페어를 라우팅할 때 트랙에 사용할 기본 폭을 지정합니다.

- Preferred Gap - 동일한 차동 페어 내 서로 다른 net의 primitive 사이에 사용할 기본 clearance를 지정합니다.

- Max Width - 차동 페어를 라우팅할 때 트랙에 사용할 수 있는 최대 허용 폭을 지정합니다.

- Max Gap - 동일한 차동 페어 내 서로 다른 net의 primitive 사이에 허용되는 최대 clearance를 지정합니다.

- Max Uncoupled Length - 차동 페어 내 positive net과 negative net 사이에서 허용되는 최대 비결합 길이 값을 지정합니다.

-

Use Impedance Profile - 이 옵션은 Layer Stack Manager에 하나 이상의 impedance profile이 정의되어 있을 때 사용할 수 있습니다. 활성화하면 드롭다운에서 필요한 impedance profile을 선택하십시오. 이 모드로 규칙을 구성하면 각 라우팅 레이어에 필요한 Preferred Width와 Preferred Gap이 지정된 impedance profile의 일부로 계산됩니다. 규칙이 정의된 후, 해당 규칙의 범위에 속하는 차동 페어를 라우팅하면 트랙 폭과 페어 gap이 지정된 임피던스를 만족하도록 해당 레이어에 필요한 값으로 자동 설정됩니다.

-

Show values for layer stack - 이 옵션은 Layer Stack Manager에 여러 layer stack이 정의되어 있을 때 대화상자에 표시됩니다. 보드에 여러 layer stack이 포함된 경우 Differential Pairs Routing Constraints는 이미지 위의 all-layer 필드 또는 Layer Attributes Table의 layer-specific 필드를 사용하여 각 layer stack에 대해 구성해야 합니다.

- Layer Attributes Table- 대화상자 하단의 그리드 영역에는 레이어 스택에 정의된 모든 신호 레이어가 표시됩니다. 단, Use Impedance Profile 옵션이 활성화된 경우는 예외입니다. 이 옵션이 활성화되면 선택한 임피던스 프로파일에 포함된 레이어만 표시됩니다. 최소, 최대, 선호 폭 및 간격 제약과 기타 레이어별 정보가 표시됩니다. 라우팅 Width 및 Gap 필드는 이미지 위의 제약 필드에서 값을 정의하여 전역으로 설정하거나, 표에 직접 값을 입력하여 개별적으로 설정할 수 있습니다. Use Impedance Profile 옵션이 활성화되면 필요한 폭 항목이 자동으로 계산되어 표의 각 레이어에 입력됩니다. 이 모드에서는 Preferred Width 및 Preferred Gap 값은 편집할 수 없지만, Min 및 Max 값은 편집할 수 있습니다.

규칙 적용

온라인 DRC, 배치 DRC, 대화형 라우팅(및 재라우팅), 자동 라우팅, 대화형 길이 튜닝(Min Gap 적용됨), 그리고 페어를 대화형으로 수정할 때(예: 페어에 속한 네트 중 하나의 트랙 세그먼트를 슬라이딩할 때) 적용됩니다.

참고

- 차동 페어의 각 네트 폭은 적용 가능한 Differential Pairs Routing 규칙에 의해 모니터링되며(Width 규칙이 아님), 해당 페어 내 네트 간의 클리어런스 검사는 여전히 적용 가능한 Clearance design rule에 의해 관리됩니다. 차동 페어 라우팅에 사용된 간격 값이 Electrical Clearance design rule에서 설정한 차동 페어 네트 간 최소 허용 클리어런스보다 작으면 Electrical Clearance design rule 위반이 발생합니다. 즉, 차동 페어를 대상으로 하는 Clearance 규칙을 정의해야 하며(필요한 특정 레이어에서), 그 connective checking mode는 Same Differential Pair로 설정하고, 클리어런스는 적용 가능한 Differential Pairs Routing 규칙의 일부로 해당 레이어에 대해 정의된 Min Gap 제약값과 같거나 그보다 낮게 설정해야 합니다.

- 차동 페어에 속한 네트와 페어에 속하지 않는 임의의 other 전기적 객체 사이의 클리어런스는 적용 가능한 Clearance 규칙에 의해 모니터링됩니다.

- 최적의 Width-Gap 설정은 보드 대부분 영역에서 달성 가능할 수 있지만, BGA 컴포넌트 아래와 같은 영역에서는 더 작고 더 촘촘한 Width-Gap 설정을 사용해야 하는 경우가 많습니다. Min Gap을 Preferred Gap보다 작게 정의하면 장애물 때문에 필요한 경우 라우터가 페어 구성원들을 서로 더 가깝게 배치할 수 있습니다. 이는 동작하지만 대가가 따릅니다. 라우팅 작업이 훨씬 더 복잡해지고, 따라서 더 느려집니다. 이 요구사항은 여러 개의 차동 페어 라우팅 규칙을 정의해서도 충족할 수 있습니다. 즉, 보드 전체에서 차동 페어를 대상으로 하는 낮은 우선순위 규칙과, 더 좁은 Width-Gap 설정이 필요한 특정 영역에서 차동 페어를 대상으로 하는 높은 우선순위 규칙을 정의하는 방식입니다. 그런 다음 해당 영역에 대해 Room Definition rule을 정의하고, 더 촘촘한 Width-Gap 설정이 필요한 차동 페어 라우팅 규칙의 범위 일부로 그 room을 사용하여 그 영역의 차동 페어를 대상으로 지정합니다.

- 규칙 스코핑에 사용할 Differential Pair 클래스는 회로도에서 정의할 수 있습니다.

)

) )

)

AI로 번역됨

AI로 번역됨