Testowanie jest ważną częścią procesu wytwarzania płytki. Po wykonaniu płytka jest zwykle testowana, aby upewnić się, że nie ma zwarć ani przerw w obwodach. Po pełnym obsadzeniu wszystkimi komponentami płytka jest często testowana ponownie, aby potwierdzić integralność sygnału i poprawne działanie urządzenia. Aby wesprzeć ten proces, zasadniczo korzystne jest posiadanie na płytce schematu punktów - Testpoints - które sprzęt testujący może sondować i wykonywać wymagane testy.

Lokalizacja punktów testowych na płytce będzie zależeć od czynników takich jak tryb testowania (w tym testy płytki nieobsadzonej po fabrykacji, testy montażowe in-circuit itp.) oraz metoda testowania (w tym testy automatyczne z użyciem sond latających i przyrządów typu bed-of-nails, testy ręczne itp.). Na przykład podczas testów płytki nieobsadzonej po fabrykacji płytka nie jest jeszcze obsadzona, więc wszystkie pady i przelotki są „dozwolone” przy wyznaczaniu punktów testowych. Natomiast lokalizacje używane jako punkty testowe podczas testów montażowych in-circuit prawie zawsze będą inne. Gdy płytka jest obsadzona, możesz już nie mieć dostępu sondą do padów elementów, a na pewno nie masz dostępu do padów i przelotek pod komponentem!

Altium Designer udostępnia rozbudowany system do obsługi potrzeb związanych z punktami testowymi i zwiększania testowalności płytek, umożliwiając osobne przypisywanie punktów testowych do testów płytki nieobsadzonej po fabrykacji i/lub do testów montażowych in-circuit — zależnie od potrzeb. Punkty testowe można przypisywać ręcznie albo w bardziej usprawniony i zautomatyzowany sposób, korzystając z okna dialogowego Testpoint Manager dialog.

Planowanie strategii punktów testowych

Zanim przejdziesz do przypisywania padów i przelotek jako lokalizacji punktów testowych, warto zrobić krok wstecz i zastanowić się, co jest wymagane. Poniżej kilka wskazówek, które warto rozważyć przy definiowaniu strategii uwzględnienia punktów testowych w projekcie:

- Wybierając stronę płytki, na której będą dozwolone punkty testowe, należy uwzględnić procesy testowe i powiązane przyrządy, które będą używane. Na przykład: czy płytka będzie sondowana tylko od strony dolnej, tylko od strony górnej, czy z obu stron.

- Punkt testowy pod komponentem (po tej samej stronie płytki co komponent) jest zwykle używany na etapie testów płytki nieobsadzonej. Należy to uwzględnić podczas planowania lokalizacji punktów testowych dla testów płytki zmontowanej.

- Zaleca się umieszczenie wszystkich punktów testowych tylko po jednej stronie płytki, w razie potrzeby wykorzystując do tego przelotki. Wynika to z faktu, że dwugłowicowy przyrząd testowy jest droższy niż przyrząd jednogłowicowy.

- Im bardziej niestandardowy i złożony jest układ punktów testowych, tym droższe będzie skonfigurowanie przyrządu do testowania płytki. Najlepszą filozofią jest opracowanie metodyki, która zapewni „ogólną” testowalność. Dobrze dopracowana i elastyczna polityka punktów testowych pozwoli testować różne projekty sprawnie i ekonomicznie.

- Należy uważnie rozważyć wszelkie wymagania dotyczące tentingu przelotek w projekcie. Zatentowanie przelotki wyznaczonej jako punkt testowy skutecznie zablokuje kontakt sondy testowej. Nawet częściowy tenting z użyciem soldermaski typu Liquid Photo Imageable (LPI) spowoduje problemy z kontaktem, ponieważ płynna maska ma tendencję do „uciekania” przez otwór przelotki. Co prawda można użyć zrywalnej soldermaski, aby zapewnić tymczasowy tenting takich wyznaczonych przelotek, ale często okazuje się to dość kosztowne.

- Ściśle konsultuj się z wykonawcą PCB i montażownią, aby upewnić się, że przy definiowaniu punktów testowych uwzględniono wszelkie specyficzne parametry projektowe. Mogą to być m.in. odstępy punkt–punkt oraz punkt–komponent, które mogą być bardziej rygorystyczne niż standardowe odstępy dla rozmieszczenia i prowadzenia ścieżek.

Poniższe sekcje przyglądają się bliżej testom fabrykacyjnym i montażowym, w tym konkretnym ograniczeniom i zagadnieniom dotyczącym punktów testowych dla każdego z nich.

Testy fabrykacyjne

Testy fabrykacyjne dotyczą testowania płytki drukowanej na etapie przed montażem, zanim jakiekolwiek komponenty zostaną umieszczone na płytce. Dlatego często nazywa się je testami płytki nieobsadzonej (bare-board). Taka metoda testowania zwykle obejmuje użycie urządzenia z sondami latającymi do testowania sieć-po-sieci. W praktyce dwie sondy są programowane do pracy w tandemie: jedna podaje impuls sygnału do danej sieci, a druga wykrywa obecność (lub brak) tego sygnału.

Dwa typowe scenariusze testów płytki nieobsadzonej po fabrykacji to:

- Test w celu upewnienia się, że celowo ciągła miedź na całej długości przewodzi czysty sygnał (poniżej maksymalnego dopuszczalnego progu impedancji) bez przerw w obwodzie.

- Test w celu upewnienia się, że sieci nie są ze sobą zwarte.

Testpoint Location Constraints

- Dedykowane pady/przelotki punktów testowych zwykle nie są potrzebne do testów fabrykacyjnych. Ponieważ płytka nie jest jeszcze obsadzona komponentami, sondy mają swobodny dostęp do padów elementów. Ponieważ na tym etapie pady zwykle nie są pokryte soldermaską, punkty testowe są zazwyczaj lokalizowane bezpośrednio na samych padach.

- Testy sondą latającą nie są ograniczone siatką, ponieważ urządzenia tego typu potrafią pozycjonować się bardzo precyzyjnie.

- Każda para lokalizacji jest ograniczona minimalnym odstępem — ze względu na fizyczne wymiary głowic sond.

Exceptions and other Considerations

- W przypadku elementów o drobnym rastrze (fine-pitch) sondowanie pojedynczego padu komponentu może nie być możliwe (a nawet praktyczne). Takie obszary miedzi mogą być bardzo małe i delikatne, dlatego czasem zaleca się, aby unikały kontaktu z sondami testowymi. W takich sytuacjach dobrym pomysłem może być dodanie przez projektanta dedykowanych padów/przelotek testowych do płytki.

- Podczas testów fabrykacyjnych płytki nieobsadzonej można również użyć przyrządu typu bed-of-nails. Zwykle ma to miejsce w produkcji wielkoseryjnej, gdzie użycie takiego przyrządu wymaga mniej czasu testowania niż sonda latająca. Jednak testy bed-of-nails mogą wiązać się z bardziej rygorystycznymi ograniczeniami lokalizacji punktów testowych i — jeśli przyrząd nie jest wykonywany na zamówienie — często wymagają, aby punkty testowe były zgodne z określoną siatką.

- Zdarzają się sytuacje, w których sonda latająca nie testuje w tandemie konkretnych par lokalizacji punktów testowych. Zwykle ma to miejsce wtedy, gdy nie ma ryzyka zwarcia (lub przesłuchu) między sieciami, ponieważ sieci nie są ze sobą sąsiadujące (wszystkie obiekty obu sieci są wzajemnie odseparowane fizycznie).

Testy montażowe

Testy montażowe dotyczą testowania płytki drukowanej na etapie po montażu, po obsadzeniu płytki wszystkimi komponentami określonymi w powiązanym zestawieniu materiałowym (BOM). Dlatego często nazywa się je testami in-circuit lub testami elektrycznymi. Taka metoda testowania zwykle obejmuje (ale w żadnym razie nie ogranicza się do!) użycia ręcznie konfigurowanego przyrządu typu bed-of-nails. W zależności od rodzaju testu wykonywanego przy użyciu przyrządu, płytka może być zasilana lub nie.

Dwa typowe scenariusze testów montażowych in-circuit to:

- Jednoczesne sondowanie jednego dedykowanego punktu testowego dla każdej sieci (lub sieci będącej przedmiotem zainteresowania). Realizuje się to przez podawanie impulsu sygnału przez każdą sondę osobno i wykrywanie wyników odbioru sygnału przez wszystkie pozostałe sondy.

- Testowanie konkretnych komponentów/magistral w celu upewnienia się, że samo urządzenie działa poprawnie. Są to testy specjalistyczne, które można przeprowadzać różnymi metodami. W najprostszym przypadku przyrząd bed-of-nails może zostać użyty do testowania bezpośrednio na padach komponentu.

Testpoint Location Constraints

- Lokalizacje punktów testowych zwykle muszą spełniać wymaganie minimalnego odstępu. Sprzęt testowy, taki jak głowice sond w przyrządzie bed-of-nails, ma określone wymiary, które ograniczają ich wzajemne zbliżenie. O ile nie używa się przyrządu wykonywanego na zamówienie, lokalizacje punktów testowych często muszą leżeć na określonej siatce. Wykonanie przyrządu na zamówienie jest droższe i bardziej czasochłonne niż skonfigurowanie wielokrotnego użytku przyrządu bed-of-nails.

- Punkty testowe mogą być wymagane do umieszczenia z zachowaniem minimalnego odstępu względem obrysów komponentów. Głowice sond większości przyrządów testowych są zwykle większe bliżej przyrządu, zwężając się do mniejszego rozmiaru w miarę zbliżania do trzpienia sondy. Wyższe komponenty wymagają większego odstępu. Dlatego najlepiej uwzględnić maksymalną wysokość komponentów na płytce i zdefiniować ogólny odstęp od obrysów, który bierze pod uwagę ten najgorszy przypadek.

- Lokalizacje punktów testowych mogą być wymagane do umieszczenia z zachowaniem minimalnego odstępu względem krawędzi płytki. Proces kontaktowania płytki parą sond latających lub matrycą sond bed-of-nails może być obciążający dla samej płytki, a płytka może w pewnym stopniu uginać się pod wpływem naprężeń testów automatycznych. Z tego powodu ryzyko uszkodzenia cienkich, delikatnych płytek jest mniejsze, gdy punkty testowe są umieszczone w pewnej odległości od krawędzi płytki.

- Zwykle wymagane jest dodanie do każdej sieci dedykowanego, dostępnego dla sondy padu/przelotki punktu testowego z kilku powodów:

- Gołe miedziane pady komponentów zwykle stają się niedostępne z powodu obecności zamontowanych elementów.

- Jeśli płytka nie jest projektowana z myślą o testowaniu, pady komponentów i przelotki raczej nie będą rozmieszczone zgodnie z wymaganą siatką punktów testowych.

- Nawet jeśli sam pad komponentu wydaje się odpowiedni jako lokalizacja punktu testowego, ograniczenia odstępu od obrysu komponentu często uniemożliwiają jego użycie.

Exceptions and other Considerations

- Chociaż przyrządy bed-of-nails są powszechną metodą testów montażowych, nie jest to jedyna metoda. Wśród różnych alternatyw są przypadki, w których używa się urządzeń z sondami latającymi — z zachowaniem ostrożności, aby nie doszło do kolizji z zamontowanymi komponentami.

- Podczas wykonywania testu elektrycznego na konkretnym komponencie pola lutownicze (pady) tego komponentu mogą być w pewnym stopniu dostępne dla sondy testowej. Należy jednak pamiętać, że korpus komponentu często zasłania środek takich padów. Innymi słowy, po zmontowaniu płytki dostępna część pada rzadko obejmuje jego środek.

Obsługa punktów testowych na padach i przelotkach

Altium Designer zapewnia pełną obsługę punktów testowych, umożliwiając wskazanie padów (przelotowych lub SMD) i/lub przelotek jako lokalizacji punktów testowych do testów na etapie produkcji i/lub montażu. Pad lub przelotka są wskazywane do użycia jako punkt testowy poprzez ustawienie odpowiednich właściwości punktu testowego oraz udzielenie odpowiedzi na dwa kluczowe pytania:

- Czy pad/przelotka ma być używana jako punkt testowy dla produkcji i/lub montażu?

- Po której stronie płytki pad/przelotka ma być używana jako punkt testowy — Top, Bottom czy po obu stronach?

Właściwości te można znaleźć w panelu Properties, gdy w obszarze projektu zostanie zaznaczony odpowiednio obiekt pad (zob. Pad Properties) lub przelotka (zob. Via Properties).

Zaznaczony pad lub przelotka są określane do użycia jako punkt testowy poprzez odpowiednie opcje dostępne dla nich w panelu Properties.

Zaznaczony pad lub przelotka są określane do użycia jako punkt testowy poprzez odpowiednie opcje dostępne dla nich w panelu Properties.

Aby usprawnić proces i wyeliminować konieczność ręcznego ustawiania właściwości punktów testowych dla padów/przelotek, Altium Designer udostępnia metodę automatycznego przypisywania punktów testowych na podstawie zdefiniowanych reguł projektowych, z użyciem

Testpoint Manager. To automatyczne przypisanie ustawia w każdym przypadku odpowiednie właściwości punktu testowego dla pada/przelotki. Masz także możliwość ręcznego wskazywania punktów testowych — w praktyce „ręcznego dopracowania” na poziomie pojedynczego pada/przelotki — co daje pełną kontrolę nad schematem punktów testowych zastosowanym na płytce.

Podczas otwierania projektów PCB utworzonych w wersji oprogramowania wcześniejszej niż wydanie Summer 09, wszelkie włączone opcje punktów testowych zostaną włączone jako Fabrication opcje punktów testowych.

Reguły projektowe punktów testowych

Ograniczenia projektu PCB należy przemyśleć i wdrożyć jako dopracowany zestaw reguł projektowych. Aby wdrożyć skuteczny schemat punktów testowych — taki, w którym wszystkie zdefiniowane punkty testowe są dostępne i mogą być użyte w testach płytki nieobsadzonej (bare-board) i/lub w testach in-circuit — trzeba wprowadzić odpowiednie ograniczenia. W tym celu w systemie reguł projektowych edytora PCB można zdefiniować następujące typy reguł:

Dostęp do reguł tych typów oraz ich definicję uzyskasz w oknie PCB Rules and Constraints Editor dialog (Design » Rules).

Zdefiniuj osobne reguły projektowe, aby ograniczyć, które pady i/lub przelotki w projekcie mogą być używane jako punkty testowe dla produkcji (Fabrication) i montażu (Assembly), oraz które sieci wymagają punktów testowych.

Zdefiniuj osobne reguły projektowe, aby ograniczyć, które pady i/lub przelotki w projekcie mogą być używane jako punkty testowe dla produkcji (Fabrication) i montażu (Assembly), oraz które sieci wymagają punktów testowych.

Reguły Testpoint Style i Usage są identyczne pod względem ograniczeń w obu trybach testowania (produkcja i montaż). Reguła stylu zasadniczo określa ograniczenia, które pad lub przelotka muszą spełnić, aby mogły być brane pod uwagę jako lokalizacja punktu testowego. Reguła użycia (usage) określa, które sieci wymagają punktu testowego.

Domyślne ograniczenia dla reguł Testpoint Usage (u góry) oraz Testpoint Style (na dole).

Domyślne ograniczenia dla reguł Testpoint Usage (u góry) oraz Testpoint Style (na dole).

Podczas definiowania reguły stylu zakres reguły można szybko utworzyć tak, aby precyzyjnie wskazać obiekty padów i/lub przelotek brane pod uwagę jako punkty testowe, korzystając z opcji dostępnych w obszarze Rule Scope Helper.

Reguły projektowe punktów testowych są wykorzystywane przez Testpoint Manager, Autorouter, procesy DRC Online i Batch, a także podczas generowania danych wyjściowych.

Istnieją domyślne reguły Fabrication i Assembly dla Testpoint Style oraz Testpoint Usage. Sprawdź, czy spełniają wymagania Twojej płytki, i w razie potrzeby wprowadź zmiany. Jeśli potrzebujesz wielu reguł tego samego typu, użyj priorytetów reguł projektowych, aby reguły o bardziej szczegółowym zakresie były stosowane jako pierwsze (np. podczas uruchamiania DRC).

Aby Testpoint Manager mógł pomyślnie przypisać punkty testowe, musi always istnieć co najmniej jedna odpowiadająca reguła Testpoint Style o zakresie All.

Podczas otwierania projektów PCB lub importowania reguł projektowych utworzonych w wersji oprogramowania wcześniejszej niż wydanie Summer 09, reguły Testpoint Style staną się regułami Fabrication Testpoint Style, a reguły Testpoint Usage staną się regułami Fabrication Testpoint Usage.

Zarządzanie punktami testowymi

Ręczne przypisywanie punktów testowych może być żmudne i czasochłonne, a tym bardziej w przypadku złożonej płytki obsadzonej setkami komponentów (i to po obu stronach płytki). Aby usprawnić zarządzanie punktami testowymi w projektach płytek, Altium Designer wyposaża edytor PCB w Testpoint Manager. Testpoint Manager umożliwia automatyczne przypisywanie punktów testowych — do testów produkcyjnych płytki nieobsadzonej i/lub testów montażowych in-circuit — na podstawie zdefiniowanych reguł projektowych. To automatyczne przypisanie ustawia w każdym przypadku odpowiednie właściwości punktu testowego dla pada/przelotki.

Dostęp uzyskasz, wybierając polecenie Tools » Testpoint Manager z menu głównego.

Szybko i efektywnie zarządzaj wymaganiami punktów testowych dla produkcji i montażu, korzystając z Testpoint Manager.

Szybko i efektywnie zarządzaj wymaganiami punktów testowych dla produkcji i montażu, korzystając z Testpoint Manager.

Użyj tego okna dialogowego, aby automatycznie przypisywać i usuwać punkty testowe z jednego, wygodnego miejsca. Lista wszystkich sieci w projekcie jest dostępna w obszarze Testpoint Net Status, wraz ze statusem wskazującym pokrycie punktami testowymi — Complete lub Incomplete — zarówno dla testów produkcyjnych płytki nieobsadzonej, jak i testów montażowych in-circuit. Kliknij przyciski Fabrication Testpoints lub Assembly Testpoints albo kliknij prawym przyciskiem w siatce, aby uzyskać dostęp do poleceń przypisywania lub usuwania danego typu punktu testowego. Zwróć uwagę, że możesz ręcznie zaznaczać sieci w górnym obszarze okna dialogowego, aby selektywnie przypisywać/usuwać punkty testowe.

Niezależnie od tego, czy przypisujesz punkty testowe dla części czy dla wszystkich sieci w projekcie, Testpoint Manager stosuje reguły stylu i użycia zdefiniowane dla punktów testowych produkcyjnych i montażowych. Aby zobaczyć kolejność przeszukiwania poprawnych obiektów, kliknij przycisk Search Order.

Aby zmienić kolejność, kliknij prawym przyciskiem na wpisie na liście kolejności wyszukiwania i użyj poleceń z menu kontekstowego albo skrótów Shift+Up Arrow i Shift+Down Arrow, aby przesunąć wpis w górę lub w dół listy.

Jeśli sieć ma przypisany punkt testowy naruszający obowiązującą regułę projektową punktów testowych, zostanie to wskazane

Illegal w obszarze

Testpoint Net Status okna dialogowego

Testpoint Manager. Użyj funkcji sprawdzania reguł projektowych edytora PCB, aby

sprawdzić poprawność przypisanych punktów testowych.

Obszar Status Summaries zapewnia pełne podsumowanie statusu punktów testowych dla płytki w obu trybach testowania. Ten obszar aktualizuje się po każdej operacji przypisania lub usunięcia. Aby uzyskać bardziej szczegółowe informacje, użyj obszaru Assignment Results. Zapewnia on m.in. szczegóły dotyczące liczby padów/przelotek Top/Bottom objętych przypisaniem/usunięciem, wraz ze wskazaniem niepowodzeń.

Sprawdzanie poprawności punktów testowych

Zdefiniowane reguły punktów testowych dla produkcji i montażu są uwzględniane w ramach funkcji Design Rule Checking (DRC) edytora PCB. Sprawdzanie DRC Online i/lub Batch można włączyć dla poszczególnych typów reguł w oknie Design Rule Checker dialog (Tools » Design Rule Check).

Uwzględnij reguły projektowe punktów testowych w procesach DRC Online lub Batch.

Uwzględnij reguły projektowe punktów testowych w procesach DRC Online lub Batch.

Pola zapytań związane z punktami testowymi

Aby wspierać różne punkty testowe produkcyjne i montażowe, które można przypisać w projekcie, dostępne są następujące słowa kluczowe do użycia przy wskazywaniu punktów testowych za pomocą logicznych wyrażeń zapytań. Każde z poniższych znajduje się w kategorii PCB Functions - Fields podczas korzystania z Query Helper:

IsAssyTestpoint - jest punktem testowym montażowym.IsFabTestpoint - jest punktem testowym produkcyjnym.IsTestpoint - jest punktem testowym po stronie Top lub Bottom.Testpoint - czy jest punktem testowym po stronie Top lub Bottom?TestpointAssy - czy jest punktem testowym montażowym?TestpointAssyBottom - czy jest punktem testowym montażowym po stronie Bottom?TestpointAssyTop - czy jest punktem testowym montażowym po stronie Top?TestpointBottom - czy jest punktem testowym po stronie Bottom?TestpointFab - czy jest punktem testowym produkcyjnym?TestpointFabBottom - czy jest punktem testowym produkcyjnym po stronie Bottom?TestpointFabTop - czy jest punktem testowym produkcyjnym po stronie Top?TestpointTop - czy jest punktem testowym po stronie Top?

Twórz logiczne wyrażenia zapytań, aby w razie potrzeby wskazywać i zwracać punkty testowe w projekcie. Przykłady logicznych wyrażeń zapytań wskazujących punkty testowe produkcyjne i montażowe:

(ObjectKind = 'Pad') And (TestpointAssy = 'True')

Wskazuje wszystkie pady będące punktami testowymi montażowymi.IsPad And (TestpointAssyTop = 'True')

Wskazuje wszystkie pady będące punktami testowymi montażowymi po stronie Top.(ObjectKind = 'Pad') And (TestpointFab = 'True')

Wskazuje wszystkie pady będące punktami testowymi produkcyjnymi.((IsPad Or IsVia)) And (TestpointAssy = 'True')

Wskazuje wszystkie pady i przelotki będące punktami testowymi montażowymi.((IsPad Or IsVia)) And IsFabTestpoint

Wskazuje wszystkie pady i przelotki będące punktami testowymi produkcyjnymi.

Generowanie raportów punktów testowych

Altium Designer zawiera dedykowane generatory raportów do tworzenia raportów punktów testowych odpowiednio dla produkcji i montażu. Te dwa generatory raportów wykorzystują odpowiednie właściwości punktów testowych dla prymitywów padów i przelotek w projekcie.

Raport punktów testowych dla produkcji będzie używać wyłącznie ustawień Fabrication punktów testowych dla padów i przelotek. Raport punktów testowych dla montażu będzie używać wyłącznie ustawień Assembly punktów testowych.

Raporty można generować na dwa sposoby:

- Bezpośrednio z dokumentu PCB, używając poleceń File » Fabrication Outputs » Test Point Report i File » Assembly Outputs » Test Point Report.

- Za pomocą odpowiednio skonfigurowanych wyjść zdefiniowanych w pliku Output Job Configuration (

*.OutJob).

Uwzględnij i skonfiguruj wyjścia raportów punktów testowych dla produkcji i montażu w samodzielnym i wszechstronnym pliku Output Job Configuration. Po zdefiniowaniu uzyskasz raporty jednym kliknięciem!

Uwzględnij i skonfiguruj wyjścia raportów punktów testowych dla produkcji i montażu w samodzielnym i wszechstronnym pliku Output Job Configuration. Po zdefiniowaniu uzyskasz raporty jednym kliknięciem!

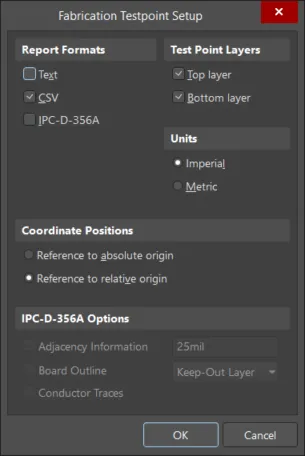

Niezależnie od metody generowania raportu, same opcje raportu są definiowane w tym samym oknie dialogowym. Dla raportu punktów testowych produkcyjnych jest to okno Fabrication Testpoint Setup dialog. Dla raportu punktów testowych montażowych używa się okna Assembly Testpoint Setup dialog. Opcje raportu są identyczne w obu tych oknach.

Zdefiniuj opcje raportu, w tym format generowanego pliku, używając odpowiedniego okna konfiguracji raportu.

Ustawienia zdefiniowane w oknie dialogowym Testpoint Setup podczas generowania danych wyjściowych bezpośrednio z PCB są inne i niezależne od tych zdefiniowanych dla tego samego typu danych wyjściowych w pliku Output Job Configuration. W pierwszym przypadku ustawienia są zapisywane w pliku projektu, natomiast w drugim — w pliku Output Job.

Opcje w obszarze Coordinate Positions okna dialogowego umożliwiają eksportowanie lokalizacji punktów testowych we wszystkich formatach raportów względem bezwzględnego początku płytki lub bieżącego początku płytki.

Wszystkie typy raportów punktów testowych obsługują osadzone tablice płytek. Podczas eksportu z dokumentu PCB zawierającego wiele osadzonych tablic płytek generowanych jest wiele plików netlist IPC-D-356A.

Rola pliku netlist IPC-D-356A

Jednym z trzech wariantów formatów wyjściowych raportu punktów testowych jest plik netlist IPC-D-356A. Plik ten jest zwykle używany do testowania w trybie kontroli gołej płytki (bare-board). Plik IPC jest następnie przetwarzany na polecenia sterujące urządzeniem testowym typu flying probe.

Niezależnie od tego, które elementy są konkretnie wskazane jako lokalizacje punktów testowych w pliku IPC-D-356A, zakłady produkcji płytek PCB zazwyczaj mogą wykorzystać dane z pliku do realizacji dowolnego rodzaju testów, choć — w zależności od okoliczności i zawartości pliku — może to wymagać pewnej ręcznej ingerencji.